c/v

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Ассоциативное устройство для линейной интерполяции | 1989 |

|

SU1649567A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки массивов чисел. Целью изобретения является повышение быстродействия. Для этого в устройство, содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, три группы элементов И, элемент И и две группы элементов задержки, введены четвертая группа элементов И и шифратор суммы. Устройство реализует последовательный по разрядам и параллельный по словам метод суммирования. Увеличение быстродействия достигается благодаря тому, что устройство не совершает дополнительные такты суммирования переносов, а игнорирует старшие разряды суммы в параллельном коде из переносов. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки массивов чисел.

Целью изобретения является повышение быстродействия устройства.

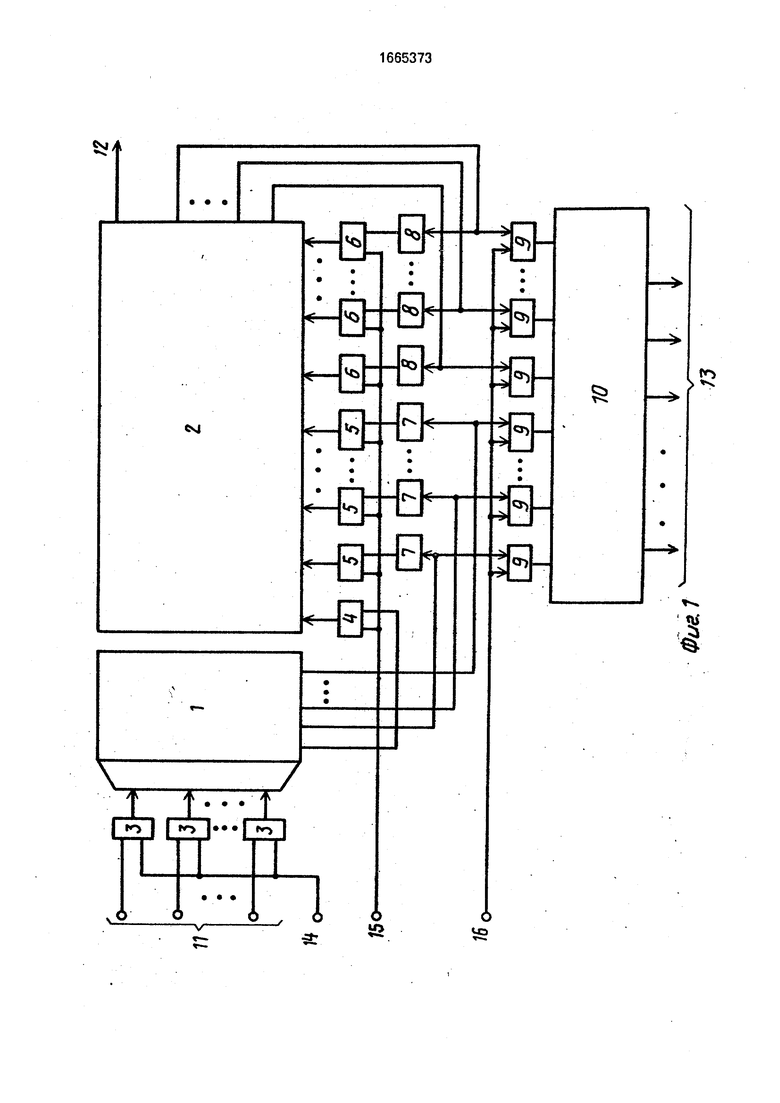

На фиг.1 приведена структурная схема ассоциативного суммирующего устройства; на фиг.2 - схема размещения информации в блоках устройства для суммирования пяти слагаемых.

Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, группу 3 элементов И, элемент И 4, группы 5 и 6 элементов И. группы 7 и 8 элементов задержки, группу 9 элементов И и шифратор 10 суммы, который может быть выполнен, например, на основе ассоциативного запоминающего блока (фиг.2). Устройство имеет входы 11 слагаемых, первый выход 12 суммы, второй

выход 13 суммы и шины 14-16 синхронизации.

Устройство работает следующим образом.

На входы 11 устройства одновременно подают одноименные разряды К слагаемых с разрядностью № 1, которые в течение тактового импульса определяют адрес слова, считываемого из блока 1. Считанное из блока 1 слово само является частью признака, подаваемого на входы опроса блока 2, причем все разряды, кроме младшего, задерживаются на один такт. Остальной частью признака являются все, кроме старшего, разряды, считываемые из блока 2 и задержанные на один такт.

Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи сигнала по шине 15, передний фронт которого начинается позже, а

О

о ел

CJ

VJ

Сл

задний раньше тактового импульса, подаваемого по шине 14. Эта мера вызвана неидеальностью элементов 7 и 8 задержки.

В том же такте, в котором был подан разрядный срез слагаемых, на выходе 12 блока 2 появляется очередной разряд суммы, Таким образом, на первом выходе получается первая часть результата суммирования в последовательном коде, причем количество тактов, за которое вычисляется первая часть результата суммы, равно разрядности слагаемых.

Вторая часть результата суммы формируется на выходах 13 блока 10 путем подачи сигнала по шике синхронизации устройства 16. Шифратор 10 шифрует старшие разряды,

Формула изобретения

Ассоциативное суммирующее устройство, содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, три группы элементов И, элемент И, две группы элементов задержки, первый вход элемента И соединен с выходом младшего разряда постоянного запоминающего блока, адресные входы которого соединены с выходами соответствующих элементов И первой группы, первые входы которых соединены с первой шиной синхронизации устройства, а вторые входы соединены с соответствующими входами слагаемых устройства, второй вход элемента И и первые входы элементов И второй и третьей групп соединены с второй шиной синхронизации устройства, выходы элементов И второй и

третьей групп соединены с соответствующими разрядами входа опроса ассоциативного запоминающего блока, выход младшего разряда которого является первым выходом суммы устройства, выходы

разрядов постоянного запоминающего блока, кроме младшего разряда, соединены через соответствующие элементы задержки первой группы с вторыми входами элементов И второй группы, выходы разрядов ассоциативного запоминающего блока, кроме младшего разряда, подключены через соответствующие элементы задержки второй группы к вторым входам элементов И третьей группы, отличающееся тем,

что, с целью повышения быстродействия, устройство дополнительно содержит четвертую группу элементов И и шифратор суммы, причем входы элементов задержки первой и второй групп соединены с первыми входами соответствующих элементов И четвертой группы, вторые входы которых подключены к третьей шине синхронизации устройства, а выходы соединены с соответствующими разрядами входа шифратора

суммы, выходы которого соединены с разрядами второго выхода суммы устройства.

Фие.1

I

VVV

13

Фиг 2

Ю

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-23—Публикация

1989-06-14—Подача