Изобретение относится к вычислительной технике и предназначено для использования в полупроводниковых ЗУ с динамическими запоминающими элементами.

Известно устройство для управления регенерацией информации в динамических ЗУ, содержащее адресный блок, дешифратор, элементы памяти, элементы ИЛИ, НЕ, информатор,и блок управления fll.

В этом устройстве используется принцип слежения за обращением ко всем строкам ЗУ. Цикл регенерации проводится, если за период , где - допустимое время хранения информации в ЗУ, хотя бы к одной строке не было обращения, При этом доступ внешних устройств к ЗУ на время всего цикла .регенерации запрещается.

Недостатком этого устройства является его сложность и низкое быс родействие в связи с удвоенной час тотой следования запросов на регенерацию. Время ожидания конца регенерации в худшем случае может быть равно времени регенерации всей памяти.

Известно другое устройство регенерации информации в блоках матричной памяти, содержащее адресный блок, дешифратор строк, элементы памяти, коммутатор, счетчик адреса регенерации, дешифратор адреса регенерации, блок синхронизирующих импульсов 2...

По одному запросу на регене- .рацию проводится цикл регенерации одной строки, если за последний период времени 2/3 Тцр к данной строк не было обращения, каждая строка регенерируется с периодом 2/3 . Недостатком данного устройства является необходимость большого количества элементов фиксации обращений.

Наиболее близким по технической

сущности к изобретению является устройство для управления регенерацией информации в блоках динамической памяти, содержащее блок управления, счетчик адресов строк, первый блок задания адресов строк, второй блок задания адресов строк, дешифра;тор адреса строк, первые элементы И, элементы памяти, вторые элементы И, элемент ИЛИ, шины адреса, причем первый входпервого блок задания адресов строк подключен к адресным шинам, а второй - к первому выходу блока управления, второй выход которого соединен с первыми входами элементов памяти, выходы которых подключены соответственно к первым Входам первых элементов И, выходы которых через элеменш или соединены с входом блока, управлени

счетчик адреса строк соединен с блоком управления и третьими входами блоков задания адресов строк, первый и второй входы второго блока задания адресов строк соединены соответственно с выходом первого блока задания адресов строк и третьим выходом блока управления, а выход через дешифратор адреса строк, - со вторыми входами первых и вторых элементов И, причем первые входы втор ых элементов И подключены к четвертому выходу блока управления, а выходы вторых элементов И соединены соответственно со вторыми входами элементов памяти СЗТ.

Недостатком известного устройства является его сложность. Количество запоминающих элементов, первых элементов И, вторых элементов И равно количеству адресов строк. Кроме того, дешифратор строк и схема ИЛИ очень громоздки.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в устройство для управления регенерацией информации в блоках памяти, содержащее блок управления, счетчик адресов строк, .блок задания адресов строк/причем первый вход блока управления является одним входом устройства, а первый выход подключен к входу счетчика адресов строк, выход которого соединен с первым входом блока задания адресов строк, второй вход которого и выход являются соответственно, другим входом и первым выходом устройства, введены первый и второй триггеры, элементы НЕ, И, И-НЕ, ИЛИ, причем единичный вход первого триггера подключен ко второму выходу блока управления, а его нулевой выход соединен с первым входом элемента И и первым входом элемента ИЛИ, выход которого соединен с третьим входом блока задания адресов строк и втоРЫГ4 входом блока управления, третий выход которого соединен с нулевыми входами триггеров, первый выход блока управления подключен к единичному входу второго триггера, единичный выход которого подключен к единичному входу первого триггера и первом входу элемента И-НБ, выход которого соединен с вторым входом элемента ИЛИ, второй вход элемента И-НЕ подклчен к-выходу элемента НЕ, вход которого является управляющим входом устройства и соединен со вторым Ьходом элемента И, выход которого подключен к четвертому входу блока задания адресов строк и является вторы выходом устройства.

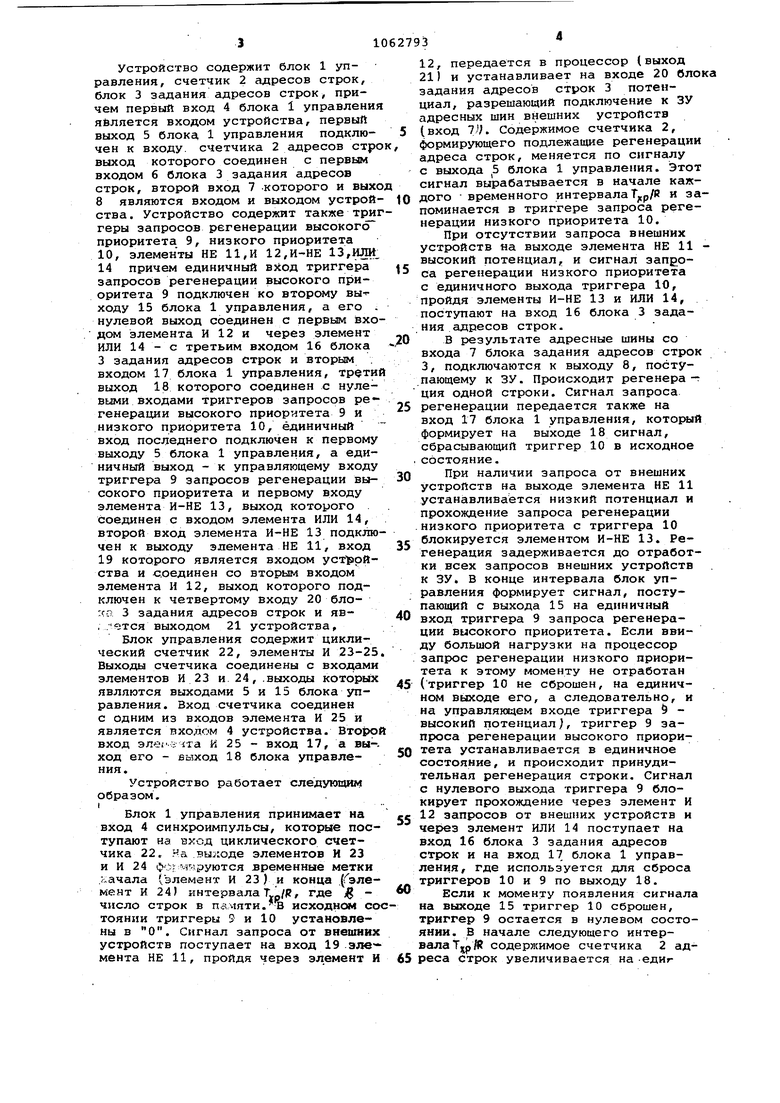

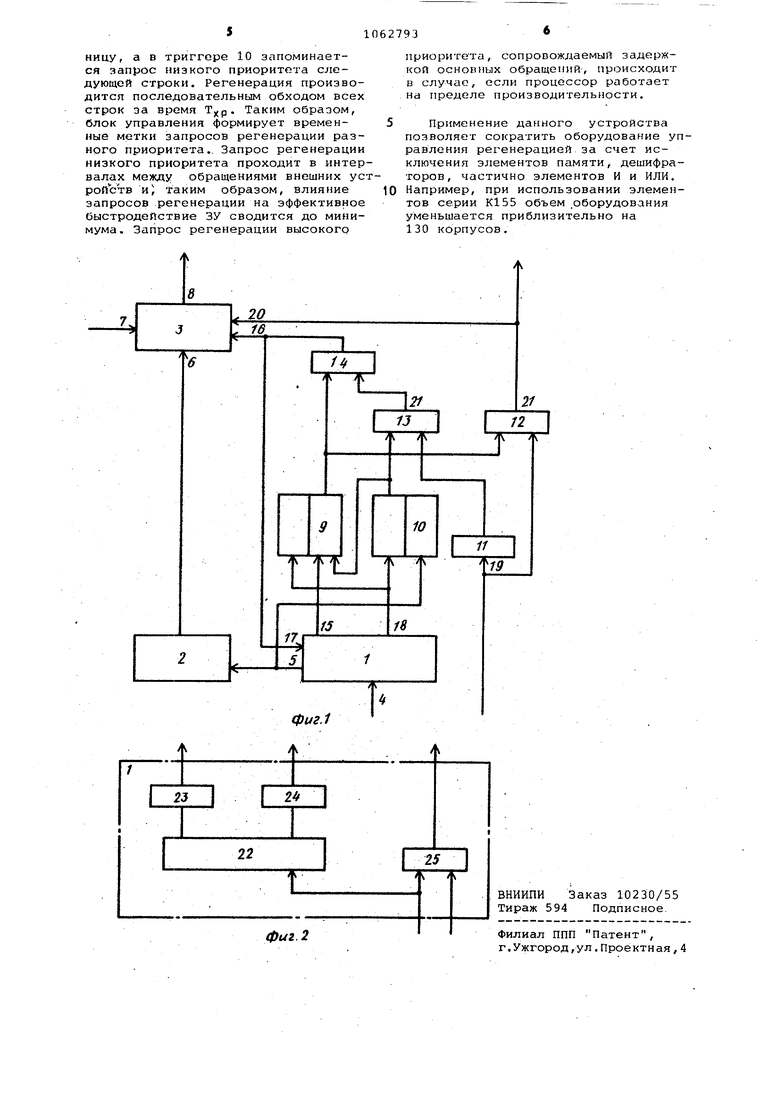

На фиг. 1 приведена схема предлагаемого устройства;на фиг. 2 - схема блока управления. Устройство содержит блок 1 управления, счетчик 2 адресов строк, блок 3 задания адресов строк, причем первый вход 4 блока 1 управлени является входом устройства, первый выход 5 блока, 1 управления подключен к входу, счетчика 2 адресов стр выход которого соединен с первым входом 6 блока 3 задания адресов строк, второй вход 7 которого и вых 8 являются входом и выходом устрой ства. Устройство содержит также три геры запросов регенерации высокого приоритета 9, низкого приоритета 10, элементы НЕ 11,И 12,И-НЕ 13,ИЛИ 14 причем единичный вход триггера запросов регенерации высокого приоритета 9 подключен ко второму вытходу 15 блока 1 управления, а его нулевой выход соединен с первым йхо дом элемента И 12 и через элемент ИЛИ 14 - с третьим входом 16 блока 3 задания адресов строк и вторым входом 17 блока 1 управления, трети выход 18 которого соединен с нулевыми входами триггеров запросов регенерации высокого приоритета 9 и низкого приоритета 10, единичный вход последнего подключен к первому выходу 5 блока 1 управления, а единичный выход - к управляющему входу триггера 9 запросов регенерации высокого приоритета и первому входу элемента И-НЕ 13, выход которого соединен с входом элемента ИЛИ 14, второй вход элемента И-НЕ 13 подклю чен к выходу элемента НЕ 11, вход 19 которого является входом устройства и соединен со вторым входом элемента И 12, выход которого подключен к четвертому входу 20 бло:сп 3 задания адресов строк и яв, .ется выходом 21 устройства. Блок управления содержит циклический счетчик 22, элементы И 23-25 Выходы счетчика соединены с входами элементов И 23 и 24,.выходы которых являются выходами 5 и 15 блока s iравления. Вход счетчика соединен с Одним из входов элемента И 25 и является входом 4 устройства. вход злее i 4та И 25 - вход 17, а выход его - выход 18 блока управлеУстройство работает следующим образом. I. Блок 1 управления принимает на вход 4 синхроимпульсы, которые поступают на вход циклического счетчика 22. На вылоде элементов И 23 и И 24 О X -РУотся временные метки /шчала (элемент И 23) и конца { элемент И 24) интервала TJP/R, где J число строк в пал1яти.в исходном со тоянии триггеры 5 и 10 установлены в О. Сигнал запроса от внешних устройств поступает на вход 19 эле мента НЕ 11, пройдя через элемент И 12, передается в процессор (выход 21) и устанавливает на входе 20 блока зсщания адресов строк 3 потенциал, разрешающий подключение к ЗУ адресных шин внешних устройств (вход 7V. Содержимое счетчика 2, формирующего подлежащие регенерации адреса строк, меняется по сигналу с выхода 5 блока 1 управления. Этот сигнал вырабатывается в начале каждого временного интервала и запоминается в триггере запроса регенерации низкого приоритета 10. При отсутствии запроса внешних устройств на выходе элемента НЕ 11 высокий потенциал, и сигнал запроса регенерации низкого приоритета с единичного выхода триггера 10, пройдя элементы И-НЕ 13 и ИЛИ 14, поступают на вход 16 блока 3 задания адресов строк. В результате адресные шины со входа 7 блока задания адресов строк 3, подключаются к выходу 8, поступающему к ЗУ. Происходит регенерация одной строки. Сигнал запроса регенерации передается также на вход 17 блока 1 управления, котогмлй формирует на выходе 18 сигнал, сбрасывающий триггер 10 в исходное состояние. При наличии запроса от внешних устройств На выходе элемента НЕ 11 устанавливается низкий потенциал и прохождение запроса регенерации низкого приоритета с триггера 10 блокируется элементом И-НЕ 13. Регенерация задерживается до отработки всех запросов внешних устройств к ЗУ. В конце интервала блок управления формирует сигнал, поступающий с выхода 15 на единичный вход триггера 9 запроса регенерации высокого приоритета. Если ввиду большой нагрузки на процессор запрос регенерации низкого приоритета к этому моменту не отработан (триггер 10 не сброшен, на единичном выходе его, а следовательно, и на управляющем входе триггера высокий потенциал), триггер 9 запроса регенерации высокого приоритета устанавливается в единичное состояние, и происходит принудительная регенерация строки. Сигнал с нулевого выхода триггера 9 блокирует прохождение через элемент И 12 запросов от внешних устройств и через элемент ИЛИ 14 поступает на вход 16 блока 3 задания адресов строк и на вход 17, блока 1 управления, где используется для сброса триггеров 10 и 9 по выходу 18. Если к моменту появления сигнала на выходе 15 триггер 10 сброшен, триггер 9 остается в нулевом состоянии. В начале следующего интервала Tjp№ содержимое счетчика 2 адеса строк увеличивается на -едитницу, а в триггере 10 запоминается запрос низкого приоритета следующей строки. Регенерация производится последовательньом обходом всех строк за время . Таким образом, блок управления формирует временные метки запросов регенерации разного приоритета.. Запрос регенерации низкого приоритета проходит в интервалах между обращениями внешних устройств и) Таким образом, влияние запросов регенерации на эффективное быстродействие ЗУ сводится до минимума. Запрос регенерации высокого

приоритета, сопровождаемый задержкой основных обращений, происходит в случае, если процессор работает на пределе производительности.

Применение данного устройства позволяет сократить оборудование управления регенерацией за счет исключения элементов памяти, дешифраторов, частично элементов И и ИЛИ. Например, при использовании элементов серии К155 объем .оборудования уменьшается приблизительно на 130 корпусов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией информации в блоках памяти | 1987 |

|

SU1434496A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Устройство для управления регенерацией динамической памяти | 1983 |

|

SU1239749A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для управления оперативной динамической памятью | 1987 |

|

SU1481850A1 |

| Устройство для регенерации информации в динамической памяти | 1981 |

|

SU1012346A1 |

| Динамическое полупроводниковое запоминающее устройство | 1987 |

|

SU1439680A1 |

| Устройство для регенерации информации в динамической памяти | 1983 |

|

SU1193729A1 |

| Устройство для регенерациииНфОРМАции B диНАМичЕСКиХблОКАХ пАМяТи | 1979 |

|

SU809388A1 |

| Устройство для управления регенерацией информации в блоках динамической памяти | 1978 |

|

SU792290A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ ИНФОРМАЦИК В БЛОКАХ ПАМЯТИ, содержащее блок управления -втчик адресов строк, блок зада.. адресов строк, причем первый ВХОД блока управления является одним ВХОДОМ устройства, а первый ВЫХОД подключен к входу счетчика адресовстрок, выход которого соединен с первым ВХОДОМ блока задания адресов строк, второй вход которого и ВЫХОД ЯВЛЯЮТСЯ соответственно другим ВХОДОМ и первым выходом устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит первый и второй триггеры, злементы НЕ, И, И-НЕ, ИЛИ, причем единичньлй вход первого триггера подключен ко второму выходу блока управления, а его нулевой выход соединен с первым входом элемента И и первым ВХОДОМ элемента ИЛИ ВЫХОД которого соединен с третьим . ВХОДОМ блока задания адресов строк и вторым ВХОДОМ блока управления третий ВЫХОД которого соединен с нулевыми входами триггеров, -первый ВЫХОД блока управления подключен к единичному входу второго триггера, единичный ВЫХОД которого подключен (Л к единичному входу первого триггера и первому ВХОДУ элемента И-НЕ, выход которого соединен с пторьлм входом элемента ИЛИ, второй вход элемента И-НЕ подключен к выходу элемента НЕ, ВХОД которого является управляющим ВХОДОМ у :тройства и соединен со вторым ВХОДОМ элемента И, выход которого подключен к четвертому входу блока задания адресов строк и являа: ется вторым ВЫХОДОМ устройства. ОС ОС

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1974 |

|

SU514346A1 |

| G, 11 С 21/00, 1976 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| G, 11 с 21/00, 1980 (прототип) | |||

Авторы

Даты

1983-12-23—Публикация

1982-10-20—Подача