Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах (ЗУ) на динамических элементах памяти..

Цель изобретения - повышение быстродействия ЗУ.

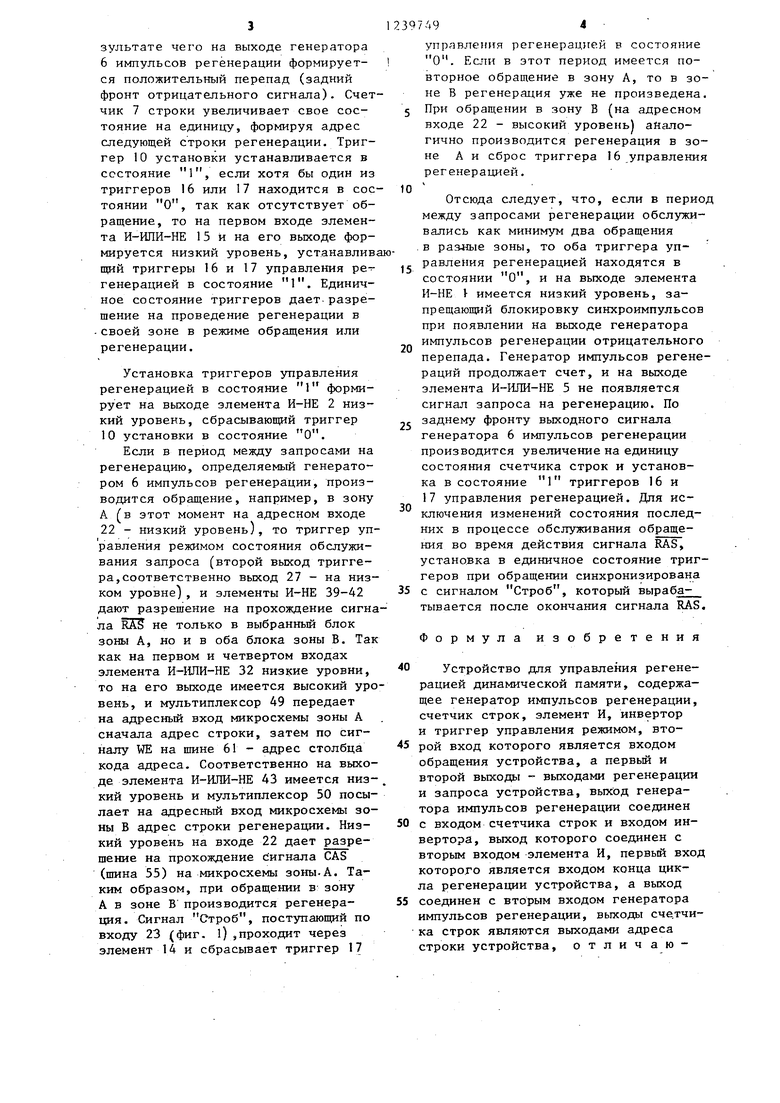

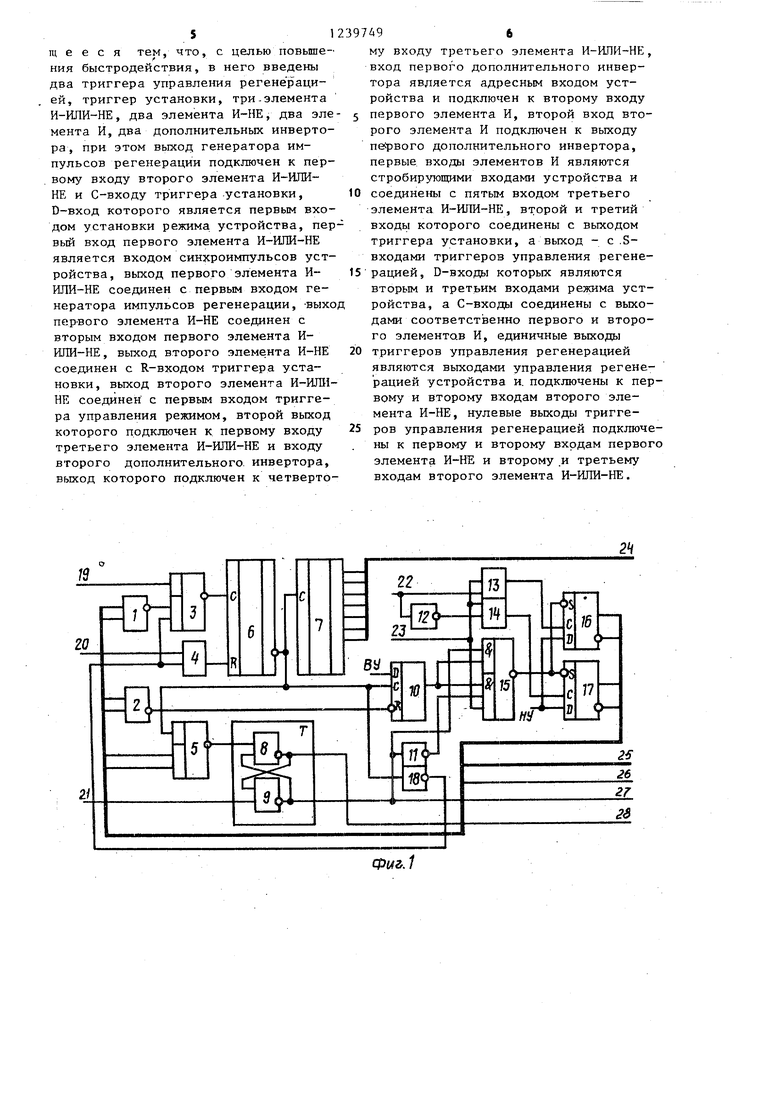

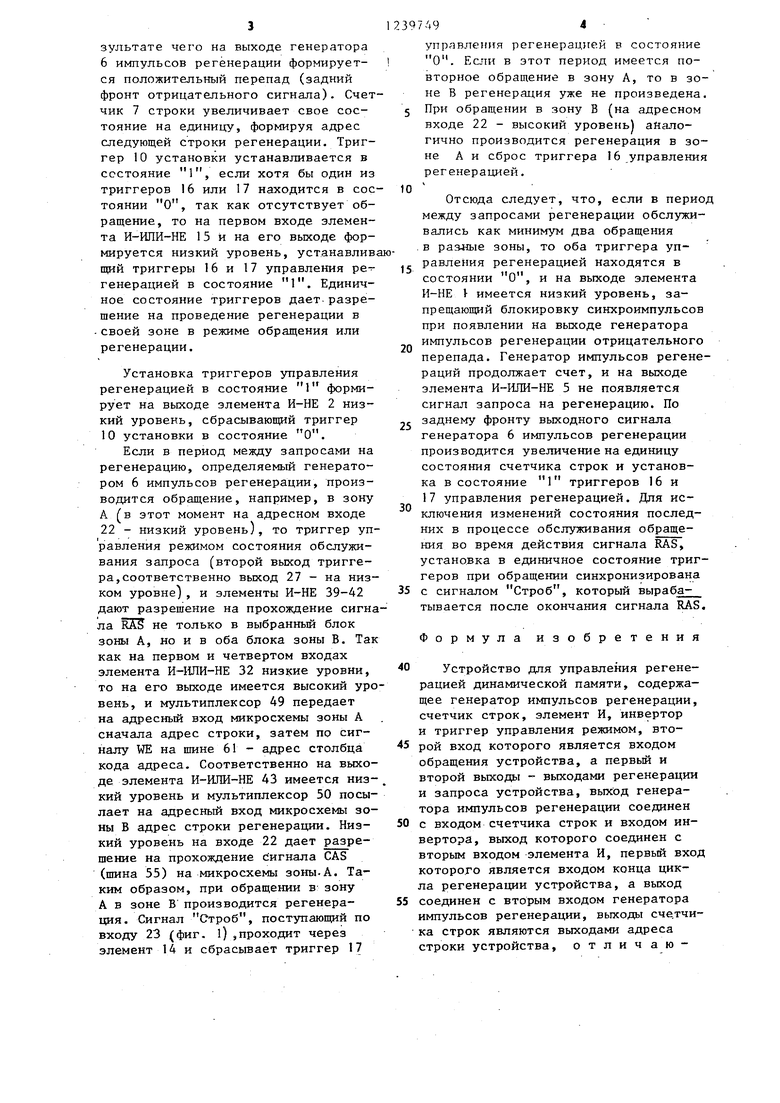

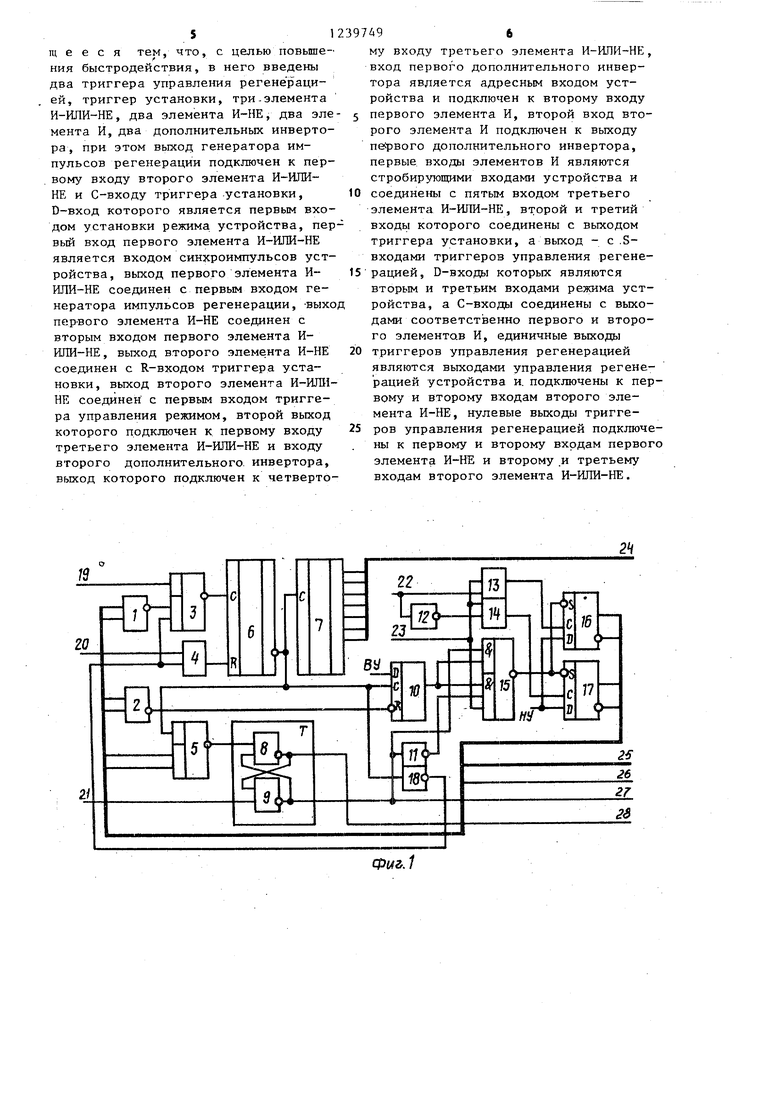

На.фиг. 1 показана функциональная схема устройства; на фиг. 2 - схематично организация одного разряда накопительной части ЗУ,

Устройство содержит элементы И- НЕ 1 и 2, элемент И-ИЛИ-НЕ 3, элемент И 4, элемент И-ИЛИ-НЕ 5, генератор 6 импульсов регенерации, счет- чик 7 строк, триггер управления режимом на элементах И 8 и 9, триггер 10 установки, инверторы 11 и 12, элементы И 13 и 14, элемент И-ИПИ-НВ 15 триггеры 16 и 17 управления регенера цией, инвертор 18, вход 19 синхроимпульсов, вход 20 конца цикла реген эации, вход 21 обращения, адресный 1вход 22, стробирующий вход 23, вы- 1ход 24 адреса строки, выходы 25 и 26 ;УПравления регенерацией, выход 27 запроса обращения и выход 28 регенерации .

На фиг. 2 приведен примервьшол- нения предлагаемого устройства, со- держащего инверторы 29-31, элемент И-ИПИ-НЕ 32, элементы И-НЕ 33-42, элемент И-ИЛИ-НЕ 43, элементы И-НЕ 44 -47, инвертор 48, мультиплексоры 49 и 50, выполненные на микросхемах блоки 51-54 памяти, управляющий вход 55, адресный вход 56,управляющий вход 57, входы 58 информации, адресные входы 59 и 60, управляющий вход 61.

Блоки памяти разделены на две зоны: зона А содержит блоки 51 и 52J зона В - блоки 53 и 54.

Зоны имеют общие входы информации 58 и управления записью 61. Выходы зон объединены в выходы 62 устройства. Зоны разделяются адресным входом, который поступает на вхо 22 устройства, причем состояние О выбирает зону А, состояние 1 - .зону В. Выборка зоны осуществляется дешифратором CAS (синхросигнал приема столбца) , построенным на

ментах И-НЕ 37 и 38. Дещифратор RAS (синхросигнал приема строки) постро- ен на элементах 33-36, 39-42.

Элементы 32-36, 39-47 управляют разрешением на прохождение сигнала

5

О

5 0 5

о , 0

5

5

0

fiffS в блоки памяти для выборки или для регенерации, элементы 32 и 43 также управляют прохождением на выход мультиплексоров адреса обращения или адреса строки регенерации.

Дешифрация производится двумя разрядами адреса обращения, поступающими на входы 22 и 56 соответственно.

Вход 22 является (фиг. 1 и 2), выходы 24-27 на фиг, 1 являются выходными, а на фиг. 2 - входными.

Два мультиплексора 49 и 50 пропускают на адресный вход АО блоков зон А и В соответственно адрес строки и столбца обращения или адреса строки регенерации. Аналогично мультиплексируются остальные разряды адреса блоков памяти. Принцип такой организации заключается в том, что при распределенном методе регенерации в период между запросами на регенерацию одной стро-ки одновременно с обслуживанием обращения в зону А по заданному адресу в зоне В производится регенерация той строки, адрес которой определяет счетчик строк. Соответственно при обращении в зону В в зоне А производится регенера- ;Ция. В этом случае к моменту, определяемому генератором импульсов регенерации, згшрос на регенерацию не вырабатьшается, и- доступ к памяти свободен.

Рассмотрим работу устройства в период, когда нет обращений к памяти. I

Исходное состояние триггеров 16 и 17 управления регенерацией - единичное, триггера 10 установки - нулевое,, По синхроимпульсам, поступающим по входу 19, генератор 6 импульсов регенерации, являющийся двоичным, счетчиком, производит счет до появления на его выходе отрицательного перепада, блокирующего дальнейшее прохождение синхроимпульсов на С-вход генератора. На выходе элемента 5 формируется положительный период, устанавливающий триггер управления режимом в состояние обслуживания регенерации, т.е. на выходе 28 - :низкий уровень. Производится цикл регенерации, в конце которого формируется сигнал конца цикла регенерации, поступающий по щине 20 в устройство на первый вход элемента И 4 ;и сбрасывающий генератор импульсов регенерации в состояние О, в результате чего на выходе генератора 6 импульсов регенерации формирует- ся положительный перепад (задний фронт отрицательного сигнала). Счетчик 7 строки увеличивает свое сое- 5 тояние на единицу, формируя адрес следующей строки регенерации. Триггер 10 установки устанавливается в состояние 1, если хотя бы один из триггеров 16 или 17 находится в сое- 10 тоянии О, так как отсутствует обращение, то на первом входе элемента И-ИПИ-НЕ 15 и на его выходе формируется низкий уровень, устанавливающий триггеры 16 и 17 управления ре- is генерацией в состояние 1, Единичное состояние триггеров дает-разреение на проведение регенерации в своей зоне в режиме обращения или регенерации.20

Установка триггеров управления регенерацией в состояние 1 формирует на выходе элемента И-НЕ 2 низкий уровень, сбрасывающий триггер 10 установки в состояние О.

Если в период между запросами на регенерацию, определяемый генератором 6 импульсов регенерации, производится обращение, например, в зону А в этот момент на адресном входе

22 - низкий уровень), то триггер упI . .

равления режимом состояния обслуживания запроса (второй выход триггера, соответственно выход 27 - на низком уровне), и элементы И-НЕ 39-42 дают разрешение на прохождение сигнала RAe не только в выбранный блок зоны А, но и в оба блока зоны В. Так как на первом и четвертом входах элемента ИЧШИ-НЕ 32 низкие уровни, то на его выходе имеется высокий уровень, и мультиплексор 49 передает на адресный вход микросхемы зоны А сначала адрес строки, затем по сигналу WE на шине 61 - адрес столбца кода адреса. Соответственно на выходе элемента И-ИЛИ-НЕ 43 имеется низкий уровень и мультиплексор 50 посылает на адресный вход микросхемы зоны В адрес строки регенерации. Низкий уровень на входе 22 дает разрешение на прохождение Сигнала CAS (шина 55) на микросхемы зоны-А. Таким образом, при обращении в: зону А в зоне В производится регенерация. Сигнал Строб, поступающий по входу 23 (фиг. 1) ,проходит через элемент 14 и сбрасывает триггер 17

25

5 10 is20

0

5

0

5

0

5

упрявления регенерацией в состояние О. Если в этот период имеется повторное обращение в зону А, то в зоне В регенерация уже не произведена. При обращении в зону В (на адресном входе 22 - высокий уровень) аналогично производится регенерация в зоне Аи сброс триггера 16 управления регенерацией.

Отсюда следует, что, если в период между запросами регенерации обслуживались как минимум два обращения в раз«ые зоны, то оба триггера уп- равлеНия регенерацией находятся в состоянии о, и на выходе элемента И-НЕ 1- имеется низкий уровень, запрещающий блокировку синхроимпульсов при появлении на выходе генератора импульсов регенерации отрицательного перепада. Генератор импульсов регенераций продолжает счет, и на выходе элемента И-ИЛИ-НЕ 5 не появляется сигнал запроса на регенерацию. По заднему фронту выходного сигнала генератора 6 импульсов регенерации производится увеличение на единицу состояния счетчика строк и установка в состояние 1 триггеров 16 и 17 управления регенерацией. Для исключения изменений состояния последних в процессе обслуживания обращения во время действия сигнала RAS, установка в единичное состояние триггеров при обращении синхронизирована с сигналом Строб, который выраба- тывается после окончания сигнала RAS.

Формула изобретения

Устройство для управления регенерацией динамической памяти, содержащее генератор импульсов регенерации, счетчик строк, элемент И, инвертор и триггер управления режимом, второй вход которого является входом обращения устройства, а первый и второй выходы - выходами регенерации и запроса устройства, выход генератора импульсов регенерации соединен с входом счетчика строк и входом инвертора, выход которого соединен с вторым входом элемента И, первый вход которого является входом конца цикла регенерации устройства, а выход соединен с вторым входом генератора импульсов регенерации, выходы сче.тчи- ка строк являются выходами адреса строки устройства, отлич ающ е е с я тем, что, с целью повышения быстродействия, в него введены два триггера управления регенерацией, триггер установки, три-элемента И-ИЛИ-НЕ, два элемента И-НЕ, два элемента И, два дополнительных инвертора, при этом выход генератора импульсов регенерации подключен к первому входу второго элемента И-ИЛИ- НЕ и С-входу триггера установки, D-вход которого является первым входом установки режима устройства, первый вход первого элемента И-ИЛИ-НЕ является входом синхроимпульсов устройства, выход первого элемента И- ИЛИ-НЕ соединен с первым входом генератора импульсов регенерации, -выход пер-вого элемента И-НЕ соединен с вторым входом первого элемента И- ШШ-НЕ, выход второго элемента И-НЕ соединен с R-входом триггера установки, выход второго элемента И-ИЛИ- НЕ соединен с первым входом триггера управления режимом, второй выход которого подключен к первому входу третьего элемента И-ИЛИ-НЕ и входу второго дополнительного, инвертора, выход которого подключен к четверто2397496

му входу третьего элемента И-ИЛИ-НЕ, вход первого дополнительного инвертора является адресным входом устройства и подключен к второму входу 5 первого элемента И, второй вход второго элемента И подключен к выходу первого дополнительного инвертора, первые входы элементов И являются стробирующими входами устройства и

10 соединены с пятым входом третьего элемента И-ИЛИ-НЕ, второй и третий входы которого соединены с выходом триггера установки, а выход - с .S- входами триггеров управления регене15 рацией, D-входы которых являются

вторым и третьим входами режима устройства, а С-входы соединены с выходами соответственно первого и второго элементов И, единичные выходы

20 триггеров управления регенерацией являются выходами управления регенерацией устройства и. подключены к первому и второму входам второго элемента И-НЕ, нулевые выходы тригге25 ров управления регенерацией подключе. ны к первому и второму входам первого элемента И-НЕ и второму .и третьему входам второго элемента И-ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Устройство для управления регенерацией информации в блоках памяти | 1987 |

|

SU1434496A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1377909A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1374280A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1987 |

|

SU1501170A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих .устройствах на динамических элементах памяти. Цель изобретения - повышение бы-, стродействия запоминающего устройства. Устройство содержит элементы НЕ, элементы И-ИЛИ-НЕ, элемент И, элемент И-ИЛИ-НЕ, генератор импульсов регенерации, счетчик строк, триггер управления на элементах И, триггер установки, инверторы, элементы И, элемент И-ИЛИ-НЕ, триггеры управления регенерацией, инвертор,вход синхроимпульсов, вход конца цикла регенерации, вход обращения, адресный вход, стробирующий вход, выход адреса строки, выход управления регенерацией, выход запроса обращения и выход регенерации. Повышение быстродействия запоминающего устройства достигается путем разбиения блока памяти на две зоны И осуществления регенерации одной из зон при обращении в другую зону. 2 ил. С € (Л (О : со -J {Sib ;о

Ю

15

2f

26

JL

2S

Фи&.1

Составитель С.Шустенко Редактор Н.Бобкова Техред Н.Бонкало

Заказ 3401/51 . Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и -открытий 113035, Москва, Ж-35, Раушская., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Ф1хг.2

Корректор А.Обручар

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент СМА № 4112513, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1986-06-23—Публикация

1983-11-29—Подача