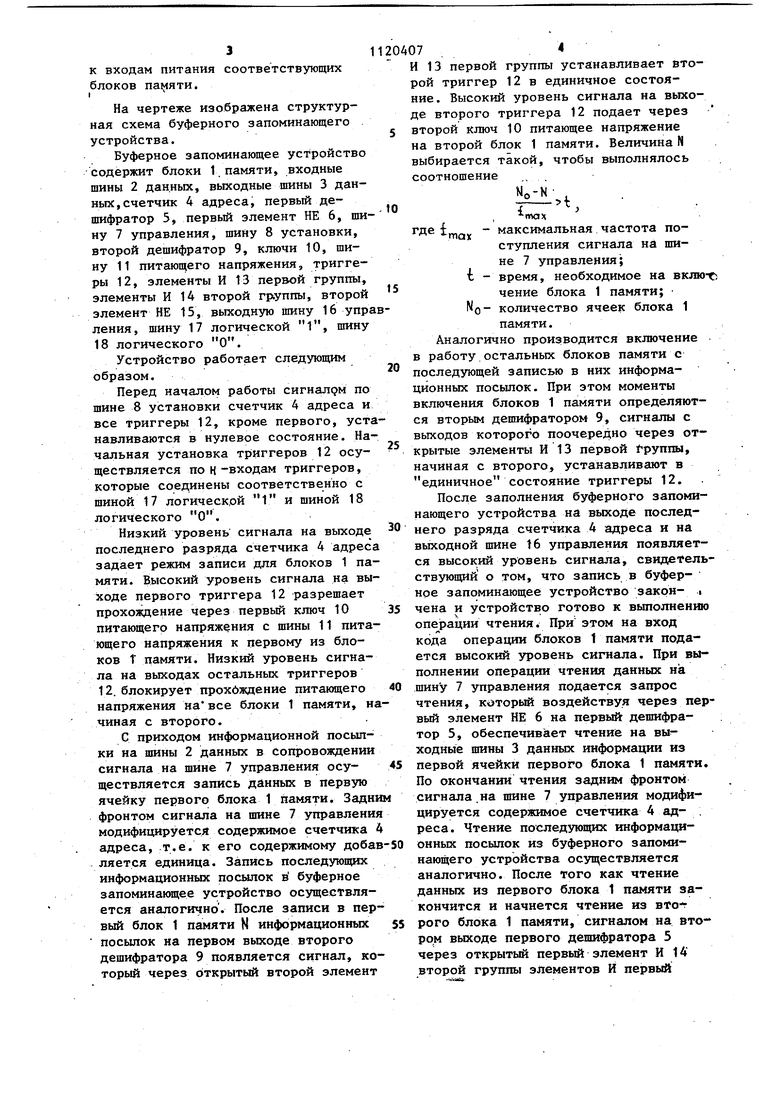

Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства в системах сбора и регистрации измерительной информации. . Известно буферное запоминающее ус ройство, содержащее накопитель, счет чик адреса, регистр адреса, дешифратор адреса, регистр числа и блок управления. В этом устройстве процес записи данных по всем вдресам накопителя и процесс чтения данных по всем адресам накопителя разнесены во времени, что позволяет его использовать для предварительного накопления блока данных и последующего вывода на регистрирунщее устройство u Недостатком устройства является большое энергопотребление, так как в его составе отсутствуют средства, регулирующие подачу питающего напряжения лишь на те запоминающие элемен ты накопителя, которые в данный момент участвуют в процессе хранения информации. Наиболее близким к изобретению по технической сущности является буферное запоминающее устройство, содержащее блоки памяти, выходы которых являются информационными выходами устройства, информационные входы блоков памяти являются соответствующими входами устройства, одни адресные входы блоков памяти подключены к выходам первой группы счетчика адреса, другие адресные входы блоков памяти подключены к выходам первого дешифратора, один вход которого подключен к выходу первого элемента НЕ, вход первого элемента Н является первым управлякицим входом устройства и подключен к тактовому входу счетчика адреса, установочный вход которого является вторым управляющим входом устройства, другие вхо ды первого дешифратора подключены к выходам второй группы счетчика адреса, управляющий вход которого подключён к соответствующим входам блоков памяти и является управляющим выходом устройства . Недостатком известного устройства также является большое знергопотребление. Цель изобретения - снижение энергопотребления устройства. Поставленная цель достигается тем, что буферное запоминающее устройство, содержащее блоки памяти, выходы которых являются информационными выходами устройства, информационные входы блоков памяти являются соответствующими входами устройства, одни адресные входы блоков памяти подключены, к выходам первой группы счетчика адреса, другие адресные входы блоков памяти подключены к выходам первого дешифратора, один вход которого подключен к выходу первого элемента НЕ, вход первого элемента НЕ является первым управляющим входом устройства и подключен к тактовому входу счетчика адреса, установочный вход которого является вторым управляющим входом устройства, другие входы первого дешифратора подключены к выходам второй группь счетчика адреса, управляющий вькод которого подключен к соответствующим входам блоков памяти и является управляющим выходом устройства, дополнительно содержит ключи, триггеры, группы элементов И, второй дешифратор и второй элемент НЕ, вход которого подключен к управляющему выходу счетчика адреса, к первым входам элементов И первой группы, кроме первого элемента И данной группы, к первому входу последнего элемента И второй группь, выход второго элемента НЕ подключен к первому входу первого элемента И первой группы и к первым входам элементов И второй группы, кроме последнего элемента И данной группы, вторые входы элементов И первой и второй групп подключены к выходам соответственно второго и первого дешифраторов, один вход второго дешифратора подключен к выходу первого элемента НЕ, другие входы второго дешифратора подключены к вьосодам первой и второй групп счетчика адреса, выходаг элементов И первой группы подключены к одним установочным входам соответствующих триггеров, другие установочные входы которых подключены к выходам соответствующих элементов И второй группы, тактовые входы триггеров подключены к установочному входу счетчика адреса, выходы триггеров подключены к одним из входов соответствующих ключей, другие входы которых объединены и являются входом питания устройства, выходы ключей подключены к входам питания соответствующих блоков naijiHTH. На чертеже изображена структурная схема буферного запоминающего устройства. Буферное запоминающее устройство содержит блоки 1 памяти, входные шины 2 данных, выходные шины 3 данных, счетчик 4 адреса, первый дешифратор 5, первый элемент НЕ 6, шину 7 управления, шину 8 установки, второй дешифратор 9, ключи 10, шину 11 питающего напряжения, триггеры 12, элементы И 13 первой группы, элементы И 14 второй группы, второй элемент НЕ 15, выходную шину 16 упра ления, шину 17 логической 1, шину 18 логического О. Устройство работает следующим образом. Перед началом работы сигналам по шине 8 установки счетчик 4 адреса и все триггеры 12, кроме первого, уста навливаются в нулевое состояние. Начальная установка триггеров 12 осуществляется по н Входам триггеров, которые соединены соответственно с шиной 17 логической 1 и шиной 18 логического О. Низкий уровень сигнала на выходе последнего разряда счетчика 4 адреса задает режим записи для блоков 1 памяти. Высокий уровень сигнала на выходе первого триггера 12 разрешает прохоясдение через первый ключ 10 питающего напряжения с шины 11 питающего напряжения к первому из блоков Т памяти. Низкий уровень сигнала на выходах остальных триггеров 12. блокирует прохбждение питающего напряжения навсе блоки 1 памяти, н чиная с второго. С приходом информационной посылки на шины 2 данных в сопровождении сигнала на шине 7 управления осуществляется запись данных в первую ячейку первого блока 1 памяти. Задни фронтом сигнала на шине 7 управлени модифицируется содержимое счетчика адреса, т.е. к его содержимому доба ляется единица. Запись последующих информационных посылок в буферное запоминакщее устройство осуществляется аналогично. После записи в пер вый блок 1 памяти N информационных посылок на первом выходе второго дешифратора 9 появляется сигнал, ко торый через открытый второй элемент И 13 первой группы устанавливает второй триггер 12 в единичное состояние. Высокий уровень сигнала на выходе второго триггера 12 подает через второй ключ 10 питающее напряжение на второй блок 1 памяти. Величина N выбирается такой, чтобы выполнялось соотношение где i-rnai: максимальная частота поступления сигнала на шине 7 управления; t - время, необходимое на вклюt; чение блока 1 памяти; NO количество ячеек блока 1 памяти. Аналогично производится включение в работу остальных блоков памяти с последующей записью в них информационных посылок. При этом моменты включения блоков 1 памяти определяются вторым дешифратором 9, сигналы с выходов которого поочередно через открытые элементы И 13 первой Группы, начиная с второго, устанавливают в единичное состояние триггеры 12. После заполнения буферного запоминающего устройства на выходе последнего разряда счетчика 4 адреса и на выходной шине 16 управления появляется высокий уровень сигнала, свидетельствующий о том, что запись в буфернре запоминающее устройство закон- i чена и устройство готово к выполнению операции чтения. При этом на вход кода операции блоков 1 памяти подается высокий уровень сигнала. При выполнении операции чтения данных на шину 7 управления подается запрос чтения, который воздействуя через первый элемент НЕ 6 на первы дешифра- : тор 5, обеспечивает чтение на вы ходные шины 3 данных информации из первой ячейки первого блока 1 памяти. По окончании чтения задним фронтом сигнала .на шине 7 управления модифицируется содержимое счетчика 4 ад- : реса. Чтение последующих информационных посылок из буферного запоминающего устройства осуществляется аналогично. После того как чтение данных из первого блока 1 памяти закончится и начнется чтение из второго блока 1 памяти, сигналом на втором выходе первого дешифратора 5 через открытый первый элемент И 14 второй группы элементов И первый триггер 12 устанавливается в нулев состояние, что, в свою очередь, отключает питающее напряжение от первого блока 1 памяти. Аналогично, после того как будет закончено чтение информации из последующих блоко 1 памяти, последние отключаются от шины 11 питающего l &пpяжeния. При чтении N информацирнных посылок из последнего . блока 1 памяти на последнем выходе второго дешифратора появляется сигггйл; который через от крытый.первый элемент И 13 первой группы элементов И устанавливает пе вый триггер 12 в единичное состоя 07® вне, что обеспечивает включение в работу первого блока 1 памяти, для последующей записи, информации. Технико-экономические преимущества предлагаемого буферного запоминающего устройства заключаются в существенном снижении его энергопотребления. Это достигается тем, что при работе буферного запоминакицего устройства, накопитель которого выполнен по модульному принципу, питающее напряжение подводится лишь к тем блокам памяти, которые в данный момент участвуют в процессе хранения информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1417040A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163358A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, выходы которых являются информационными выходами устройства, информационные входы блоков памяти являются соответствующими входами устройства, одни адресные входы блоков памяти подключены к выходам первой группы счетчика адреса, другие адресные входы блоков памяти подключены к выходам первого дешифратора, один вход которого подключен к выходу первого элемента НЕ, вход первого элемента НЕ является первым управлякнцим входом устройства и подключен к тактовому входу счетчика адреса, установочный вход которого является вторым ynpjaBляющим входом устройства, другие входы первого дешифратора подключены к . выходам второй группы счтечика адресов, управлянщий выход которого подключен к соответствующим входам блоков памяти и является управляющим выходом устройства, отличающееся тем, что, с целью снижения энергопотребления, онр содержит ключи, триггеры, группы элементов И, второй дешифратор и второй элемент НЕ, вход которого подключен к управляющему выходу счетчика адреса, к первым входам элементов И первой группы, кроме первого элемента И данной группы, и к первому входу последнего элемента И второй группы, выход второго элемента НЕ подключен к первому входу первого элемента И первой группы и к первым входам элементов И второй группы, кроме последнего элемента И данной группы, вторые входы элементов И первой и второй групп подключены к выходам соответственно второго и первого дешифраторов один вход второго дешифратора подключен к выходу первого элемента НЕ, другие входы второго дешифратора подключены к выходам первой и второй групп счетчика адреса, выходл элементов И первой группы подключены к одним установочND ным входам соответствующих триггеров, другие установочные .входы которых 4;а подключены к выходам соответствукшрсс VieMeHTOB И второй группы, тактовые О 1 входы триггеров подключены к уста,новочному входу счетчика адреса, выходы триггеров подключены к одним из входов соответствукицих ключей, другие . входы которых объединены и являются входом питания устройства, выходы ключей подключены к уходам питания соответствующих блоков памяти.

X

LfJLZJLlJ

10

L LlJLiJLZJ

Ч

ffi

I Jf I

гЗ

3m

-t

rr

.Угу;

ГГ1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления блокомпАМяТи | 1978 |

|

SU809345A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство | 1979 |

|

SU771717A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-10-23—Публикация

1983-06-09—Подача