Изобретение относится к вычислительной технике и может быть исползовано для вычисления логарифма двоичных чисел по произвольному основанию.

Цель изобретения - повьшение . быстродействия устройства.

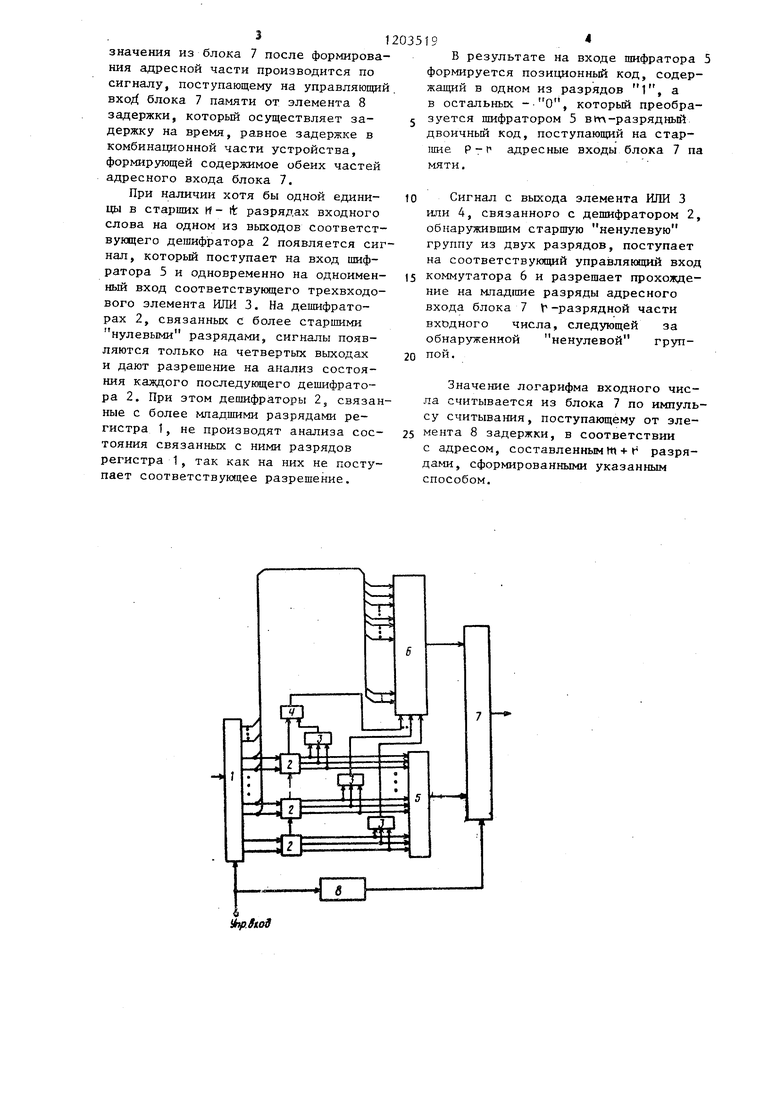

На чертеже показана блок-схема устройства для вычисления логарифм

чисел.

Устройство содержит входной регистр 1 , дешифраторы 2, трехвходовы элементы ИЛИ 3, двухвходовой элемент ИЛИ 4, шифратор 5, коммутатор 6, блок 7 постоянной памйти и элемент 8 задержки.

Устройство реализует алгоритм вычисления логарифмов двоичных; чисел при произвольном основании логарифма в соответствии с выражением

y--eo jo. 1

используя следующее преобразование

г.Х-7 --7--К хе г гад,,.

где

Ч--Ь,Зг

- величина, зависящая

от основания логарифма J

X -h -разрядное двоичное число, максималное значение которого равно 2 -1; у- двоичное Р -разрядное число, , 2 -V,

Число разрядов р выходной величины у определяется следующим соотншением:

Ш1Л в двоичной форме представления

чисел

,и

.o.

Отсюда

К,, + 1.

р- чцсло разрядов - должна быть целой величиной, поэтому

Р- Ео гСКа-КпИ)1,

дер t наибольшее ближайшее к А целое.

Величина KJ нредставляется в двоичной форме f -разрядным числом,. Г Збза , Ко С . Логарифмы чисел,

Л -

20351;:)2

имеющих одну старшую единицу в- соседних разрядах, отличаются один от другого на величину KQ. Минимальное число слов, имеющих различное зна- .

;; чение логарифма в пределах от 1 до Kg, определяется И разрядами. Начиная с h -го разряда, число слов, заключенных меж;л,у |-м и ((-)-1)-м разрядами, будет б ольше 2, т.е.

0 с увеличением номера разряда все

большему количеству слов будет соответствовать одно и то же значение логарифма, так как этих значений не больше 2. Используя это свойство

15 и учитывая, что максимальное число различных значений логарифмов определяется величиной 2 , можно сделать вывод о том, что в блоке 7 постоянной памяти должно храниться не

20 более 2 р -разрядных слов, при этом можно выделить группы слов, имеющих одинаковые значения логарифма.

Устройство работает следующим

25 образом.

На вход входного регистра 1 поступает двоичное и -разрядное число, которое записывается по импульсу, поступающему с управляющего

30 входа устройства на управляющий вход регистра 1. Затем информация с выходов регистра 1 парами разрядов поступает на входы дешифраторов 2 и одновременно на информацион22 ные входы коммутатора 6. Каждьй .дешифратор 2 анализирует соответствующие два разряда регистра 1 , начиная со старших, только в случае отсутствия единиц в анализируемых

40 разрядах предьщущего дешифратора. Таким образом анализируются на наличие единицы наибольшего веса - старших разрядов исходного числа.

Число дешифратора соответствует

h-r

В случае отсутствия в указанных разрядах единицы на выходе первого дешифратора 2 появляется сигнал, который через двухвходовой элемент ИЛИ 4 поступает на один из управляюш 1х входов коммутатора 6 и тем cat ibiM дает разрешение на прохождение через коммутатор 6 содержимого t младших разрядов входного слова. Эти п разрядов определ:яют младшие

разряды адреса блока памяти. Каждому значению адреса поставлено в соответствие значение логарифма исходного числа. Считьтание этого

3

значения из блока 7 после формирования адресной части производится по сигналу, поступающему на управляющий Bxorf блока 7 памяти от элемента 8 задержки, который осуществляет за- держку на время, равное задержке в комбинационной части устройства, формирующей содержимое обеих частей адресного входа блока 7.

При наличии хотя бы одной едини- цы в старших W - (t разрядах входного слова на одном из выходов соответствующего дешифратора 2 появляется сигнал, который поступает на вход шифратора 5 и одновременно на одноимен- ный вход соответствующего трехвходо- вого элемента ИЛИ 3. На дешифраторах 2, связанных с более старшими нулевыми разрядами, сигналы появляются только на четвертых выходах и дают разрешение на анализ состояния каждого последующего дешифратора 2. При этом дешифраторы 2, связанные с более младшими разрядами регистра 1, не производят анализа сое- тояния связанных с ними разрядов регистра 1, так как на них не поступает соответствующее разрешение.

19.

В результате на входе шифратора формируется позиционный код, содержащий в одном из разрядов 1, а в остальных - О, который преобразуется шифратором 5 вт-разрядный двоичный код, поступающий на старине р-г адресные входы блока 7 па мяти.

Сигнал с выхода элемента ИЛИ 3 или 4, связанного с дешифратором 2, обнаружившим старшую ненулевую группу из двух разрядов, поступает на соответствуюпщй управляющий вход коммутатора 6 и разрешает прохождение на младгаие разряды адресного входа блока 7 V-разрядной части входного числа, следующей за обнаруженной ненулевой группой.

Значение логарифма входного числа считывается из блока 7 по импульсу считывания, поступающему от элемента 8 задержки, в соответствии с адресом, составленнымW+И разрядами, сформированными указанным способом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Запоминающее устройство | 1984 |

|

SU1185394A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Генератор периодических псевдослучайных двоичных последовательностей сложной структуры | 2018 |

|

RU2690765C1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

/hp.fto9

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления логарифма числа | 1979 |

|

SU860067A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-07—Публикация

1984-04-13—Подача