Изобретение относится к измери тельной технике и может быть использовано в регистрирующих приборах непрерывной записи, например осциллографах с памятью, регистраторах аварийных процессов и т.д.

Цел ь изобретения - одновременное повьштение точности регистрации, снижение требований к точности цифро- аналогового преобразователя и упрощение.

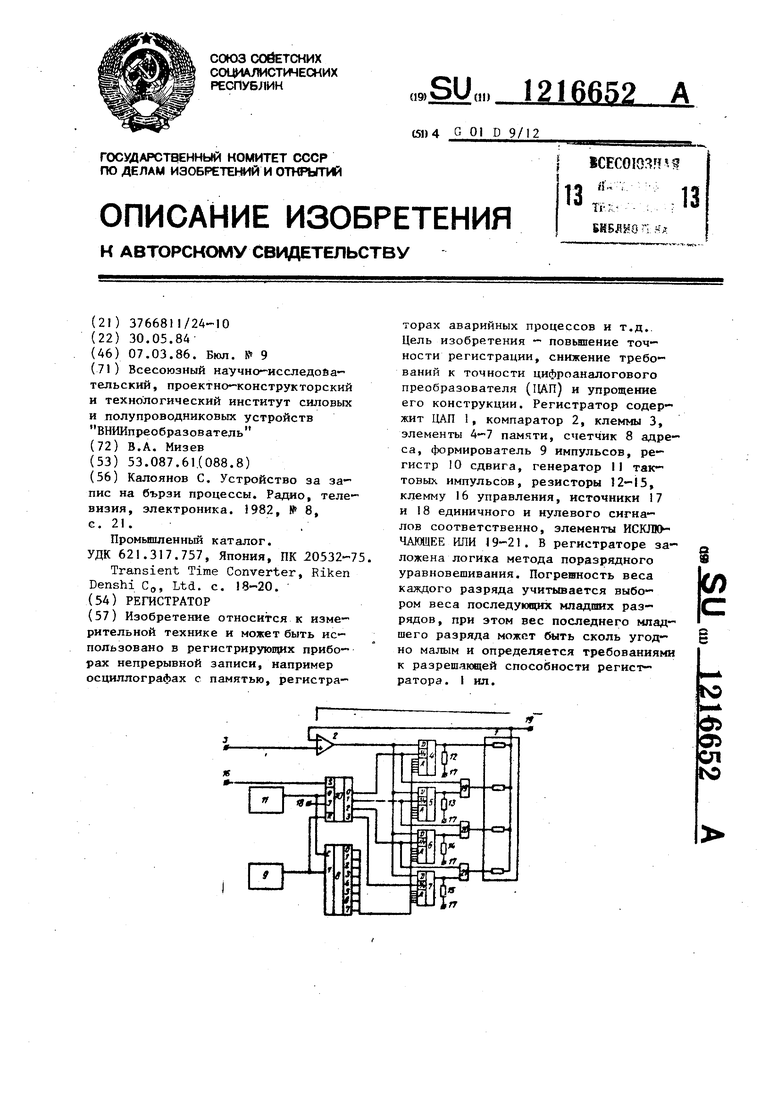

На чертеже изображен предлагаемый регистратор.

Регистратор содержит цифроанало - говый преобразователь (ЦАЦ) , компаратор 2, один вход которого соединен с входной клеммой 3, а второй вход компаратора 2 - с выходом ЦАП 1, элементы 4-7 памяти, счетчик 8 адреса, выходы которого со- единены с адрёснь мн входами элемен- . тов 4-7 памяти, формирователь 9 itM пульсов, регистр 10 сдвига выход формирователя 9 импульсов соединен с входом разрешения счетчика 8 адреса и входом установки в единицу регистра Ш сдвига, генератор 1) тактовых импульсов, выход которого соединен с тактовь ми входами форм№ роватеяя 9 импульсов, счетчика 8 адреса и регистра 10 сдвига, вход старшего разряда ЦДЛ 1 подключен к вьосоду соответствующего элемента 4 памяти, резисторы 52-15, входную 16 управления, соединеннуи с входом установки в ноль регист ра 0 сдвига, асточник Г/ единично- го сигнала и источник 18 нулевого сигнала, элементы ИСКШОЧАЩЕЕ ИЛИ J 92f. I

Входы элементов 4-7 памяти соединены вместе й подключены к выходу компаратора 2, первый вызсод регист ра 10 сдвига подключен к входу Запись-чтение элемента А памяти старшего разряда, остальные выходы регистра 10 сдвига подключены к соответствующим входам Запись-чте- . ние .элементов 5-7 памяти младших разрядов, выходы элементов 5-7 памяти через злементы ИСКЛЮЧАЩЕЕ ИЛИ 19 2.1 подключены к соответствующим разрядам ЦДЛ , оставшийся вход каяр дого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19-21 соединен с входом Запись-чтение элементов 6, 5 и 4 памяти предыдущего старшего разряда соответствен-- но, выходы элементов 4-7 памяти че-

16652

рез резисторы 12-15 соединены с источником 17 единичного сигнала, -вход регистра 10 сдвига соединен с источником 18 нулевого сигнала,

5 выход ЦАП I подключен к выходной клемме 19.

Предлагаемый регистратор работает следующим образом.

В режиме записи на входную клем10 му 3 подается регистрируемый сигнал, а на клемму управления-сигнал Лог. О.

Формирователь 9 импульсов сигналом I устанавливает выходы

(5 регистра сдвига в 1 и открывает вход разрешения счетчика 8 .адреса. При этом сигнал генератора такто- вьвс импульсов I 1 устанавливает на выходе счетчика 8 адреса код ад20 реса, который поступает на адресные входы элементов 4-7 памяти. Сигнал 1 с выходов регистра 10 сдвига поступает на вход Запись- чтение элементов 4-7 памяти, пе-

25 реводит их в режим Запись. На выходах зажимах элементов памяти устанавливается I через резисторы 12-15 источником 17 единичного сигнала. На вход ЦАП 1 поступает

30 код 1000, его выходное напряжение сравнивается с входным аналоговым сигналом компаратором 2, результат сравнения подается tia элементы 5-7 памяти и запоминается в них. По

окончания сигнала f на выходе формирователя 9 импульсов, регистр 10 сдвига разблокируется и с приходом очередного сигнала генератора JI тактовых импульсов на первом выходе регистра 10 сдвига появляется

О

подаваемый на его

вход источником 18 нулевого сигнала.

Сигнал О с первого выхода ре- гнстра 10 сдвига переводит элемент 4 памяти в режим Чтение и на его выходе появляется результат сравне- ния веса старшего разряда ЦАП 1 с

величиной аналогового сигнала на клемме 3. Далее ИСКЛЮЧАЩЕЕ ИЛИ 19 переводится сигналом О в режим повторителя и 1 с выхода элеента 5 памяти поступает на вход ЦАП 1. Выходное напряжение ЦАП I вновь сравнивается с аналоговым сигналом компаратором 2, результат сравнения с его выхода подается на элементы 4-7 памяти (элемент 4 па-

мяти переведен в режим - Чтение и не воспринимает входной сигнал). Очередной сигнал генератора I 1 тактовых импульсов записывает О на второй выход регистра Ю сдвига, при этом элемент 5 памяти переводится -в режим чтение, а ИСКЛЮЧАК ЩЕЕ ИЛИ 20 в Повторитель. Результат сравнения двух старших разрядов ЦАП 1 сохраняется в элементах 4 и 5 памяти, 1 с выхода элемента 6 памяти через ИСКЛЮЧАЮЩЕЕ ИЛИ 20 поступает на вход третьего разряда ЦАП 1, а на первый и второй разряды подают содержимое элементов 4 и 5 памяти.

Выходной сигнал на выходе ЦАП I сравнивается с аналоговым сигналом компаратором 3, результат сравнения запоминается в элементе 6 памяти. Последующие разряды ЦАП I последовательно cpaвнивa oтcя с аналоговым сигналом, а результаты заносятся в элементы памяти младших разрядов. После того, как все выходы регистра 10 сдвига установлены в О, преобразование завершено. В элементах 4-7 памяти хранится код числа, уравновешивающего весами разрядов ДАП I входной аналоговый сигнал.

Новый цикл преобразования наступает после подачи очередного сигнала 1 формирователем 9 импульсов на вход разрешения счетчика 8 адресов, который увеличивает код адреса на единицу. В процессе записи происходит циклическое изменение содержимого счетчика адреса 8 от О до переполнения, при этом также циклически сменяется информация в ячейках элементов 4-7 памяти. Прекращение регистрации сигнала и его воспроизведение происходит после подучи 1 на клемму 16 управления, при этом выходы регистра 10 сдвига блокруются в состоянии О.

Сигналы О с выходов регистра . переводят элементы 4-7 памяти в режим Чтение, а элементы ИСКПЮЧАКЬ ЩЕЕ ИЛИ 19-21 в режим Повторителя Сигналы формирователя 9 импульсов и генератора 11 тактовых импульсов поочередно в том же порядке, что и при записи, производят смену кодов адреса на выходе счетчика 8 адреса, в результате чего на выходах элементов 4-7 памяти поочередно устанйв

16652

ливаются коды аналоговых сигналов, хранимые в элементах 4-7 памяти. ЦАП 1 по кодам с выходов элементов 4-7 памяти формирует значения

5 аналоговой величины, воспроизводя записанную аналоговую величину во времени. Поскольку ЦАП 1 участвует в аналого-цифровом, а потом он же и в цифроаналоговом преобразова)0 НИИ, то, в общем случае, конкретная величина веса каждого разряда не имеет существенного значения, а только важно ее постоянство в течение времени между записью и воспро-

15 изведением. Однако поскольку в предлагаемом регистраторе заложена логика метода поразрядного уравновешивания, то необходимым условием нормальной работы является требова-

20 ние, чтобы вес каждого разряда был не больше, чем сумма веса последующих за ним младших разрядов с учетом возможных разбросов веса старшего и младших разрядов.

25

Таким образом, погрешность веса каждого разряда учитывается выбором веса последующих младших разрядов , при этом вес последнего младше-

,Q го разр5зда может быть сколь угодно малым, и определяется требованиями к разрешающей способности регистратора.

35

Формула изобретения

Регистратор, содержащий компаратор, первый вход которого соединен с входной клеммой, а второй - с выходом цифроанапогового преобразователя, элементы памяти, адресные входы которых соединены с выходами счетчика адреса, вход Разрешение которого соединен с входом установки в 1 регистра сдвига и с выхо- дом формирователя импульсов, генератор тактовых импульсов,- соединенный с тактовыми входами счетчика адресг: и регистра сдвига, входная . клемма управления соединена с вхо-

дом установки в О регистра сдвига.

резисторы, источник единичного сигнала, источник нулевого сигнала, отличающийся тем, что, с целью повьш1ения точности регист- рации, в него введены элементы НСЮВО- ЧАЮЩЕЕ ИЛИ, причем входа элементов памяти соединены вмест- и подключены к выходу компаратора, второй

51216652 6

вход которого соединен с выходнойпрямую с первым входом цифроаналоклеммой, выходы регистра сдвигагового преобразователя, а выходы осподключены к входам Запись-чтение тальных элементов памяти череа втоэлементов памяти и, кроме младшегорые входы элементов ИСКЛЮЧАЙТЕ ИЛИ

разряда, к первь№1 входам элементов5 соединены с остальными входаИСКЛЮЧАИ ЩЕ ИЛИ, выход элемента па-ми цифроаналогового преобразомяти старшего разряда соединен навателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для ввода аналоговой информации | 1985 |

|

SU1260966A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

Изобретение относится к измерительной технике и может быть использовано в регистрирующих приборах непрерывной записи, например осциллографах с памятью, регистраторах аварийных процессов и т.д.. Цель изобретения - повьшение точности регистрации, снижение требований к точности цифроаналогового преобразователя (ЦАП) и упрощение его конструкции. Регистратор содержит ЦАП 1, компаратор 2, клеммы 3, элементы 4-7 памяти, счетчик 8 адреса, формирователь 9 импульсов, регистр 10 сдвига, генератор II тактовых импульсов, резисторы 12-15, клемму I6 управления, источники 17 и 18 единичного и нулевого сигналов соответственно, элементы ИСКПКН ЧАЮЩЕЕ ИЛИ 19-21. В регистраторе заложена логика метода поразрядного уравновешивания. Погрешность веса каждого разряда учитывается выбором веса последующих младших разрядов, при этом вес последнего младшего разряда может быть сколь угодно малым и определяется требованиями к разрешающей способности регистратора. I ил.

| Калоянов С | |||

| Устройство за за- пис на бързи процессы | |||

| Радио, теле- визия, электроника | |||

| Способ соединения двух двигателей постоянного тока снабженных контактными кольцами и компаудными обмотками для получения синхронного их вращения | 1918 |

|

SU982A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Промьшшенный каталог | |||

| ПОРТСИГАР С ПРИСПОСОБЛЕНИЕМ ДЛЯ СКРУЧИВАНИЯ ПАПИРОС | 1922 |

|

SU621A1 |

| Transient Time Converter, Riken Denshi GO, Ltd | |||

| c | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1986-03-07—Публикация

1984-05-30—Подача