1

Изобретение относится к области запоминающих устройств и предназначено для использования в системах обработки цифровой информации.

Цель изобретения - упрощение устройства и повышение его быстродействия.

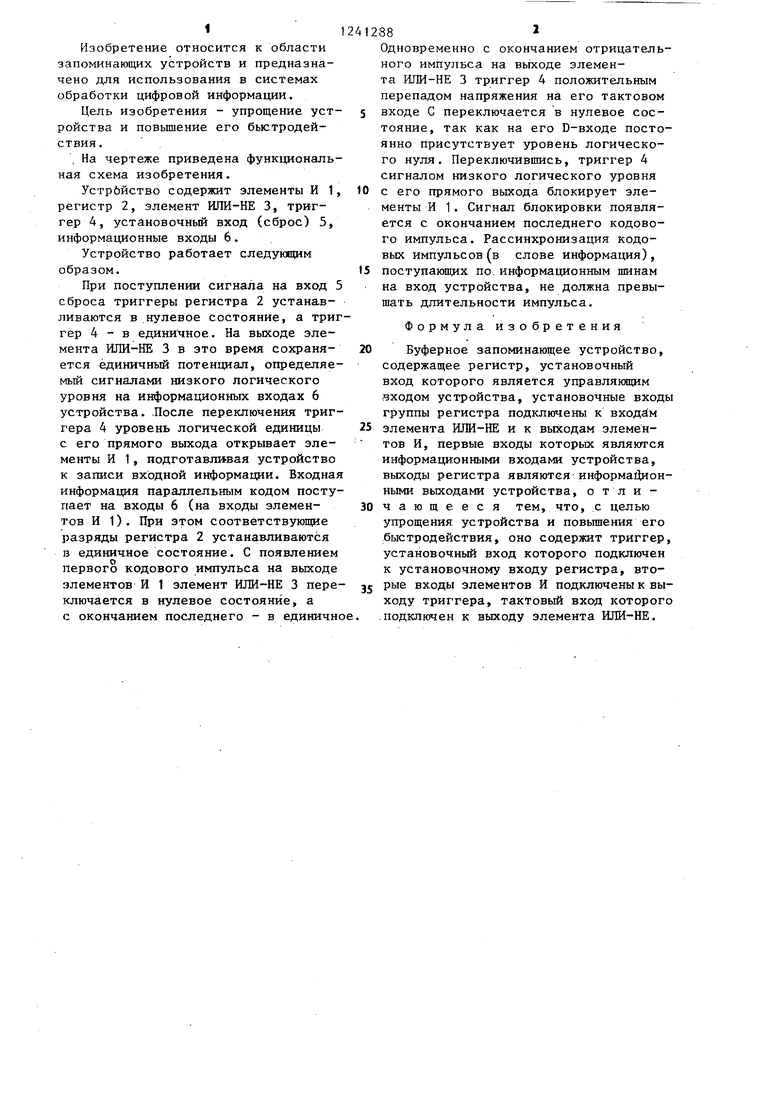

, На чертеже приведена функциональная схема изобретения.

Устрбйство содержит элементы И 1, регистр 2, элемент ИЛИ-НЕ 3, триггер 4, установочный вход (сброс) 5, информационные входы 6.

Устройство работает следующим образом.

При поступлении сигнала на вход 5 сброса триггеры регистра 2 устанавливаются в нулевое состояние, а триггер 4 - в единичное. На выходе элемента ИЛИ-НЕ 3 в это время сохраняется единичный потенциал, определяемый сигналами низкого логического уровня на информационных входах 6 устройства. .После переключения триггера 4 уровень логической единицы с его прямого выхода открывает элементы И 1, подготавливая устройство к записи входной информации. Входная информация параллельным кодом поступает на входы 6 (на входы элементов И 1). При этом соответствующие разряды регистра 2 устанавливаются в единичное состояние. С появлением первого кодового импульса на выходе элементов И 1 элемент ИЛИ-НЕ 3 переключается в нулевое состояние, а с окончанием последнего - в единичное

12412882

Одновременно с окончанием отрицательного импульса на выходе элемента ИЛИ-НЕ 3 триггер 4 положительным перепадом напряжения на его тактовом

5 входе С переключается в нулевое состояние, так как на его D-входе постоянно присутствует зфовень логического нуля. Переключившись, триггер 4 сигналом низкого логического уровня

10 с его прямого выхода блокирует элементы И 1. Сигнал блокировки появляется с окончанием последнего кодового импульса. Рассинхронизация кодовых импульсов (в слове информация),

5 поступающих по. информационным щинам на вход устройства, не должна превы- щать длительности импульса.

20

25

30

35

Формула изобретения

Буферное запоминающее устройство, содержащее регистр, установочный вход которого является управлякяцим зходом устройства, установочные входы группы регистра подключены к входим элемента ИЛИ-НЕ и к выходам элементов И, первые входы которых являются информационными входами устройства, выходы регистра являются информа11ион- ными выходами устройства, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, оно содержит триггер, установочный вход которого подключен к установочному входу регистра, вторые входы элементов И подключены к выходу триггера, тактовый вход которого подключен к ВЫХ.ОДУ элемента ИЛИ-НЕ.

Формула изобретения

Буферное запоминающее устройство, содержащее регистр, установочный вход которого является управлякяцим зходом устройства, установочные входы группы регистра подключены к входим элемента ИЛИ-НЕ и к выходам элементов И, первые входы которых являются информационными входами устройства, выходы регистра являются информа11ион- ными выходами устройства, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, оно содержит триггер, установочный вход которого подключен к установочному входу регистра, вторые входы элементов И подключены к выходу триггера, тактовый вход которого подключен к ВЫХ.ОДУ элемента ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1988 |

|

SU1550562A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для контроля дешифраторов | 1985 |

|

SU1298924A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1397968A1 |

| Цифровой коррелятор | 1982 |

|

SU1045233A1 |

| Устройство для мажоритарного выбора сигналов | 1984 |

|

SU1238278A1 |

| Буферное запоминающее устройство | 1980 |

|

SU881855A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1042017A1 |

Изобретение предназначено для использования в системах обработки цифровой информации. Цель изобретения состоит в упрощении устройства. Буферное запоминающее устройство содержит регистр, установочный вход которого подключен кустановочному входу триггера и является установочным входом устройства, группа установочных входов регистра подключена к выходам элементов И, первые входы которых являются информационными входами устройства, вторые входы зле- ментов И объединены и подключены к выходу триггера, тактовый вход (вход, по которому триггер изменяет свое первоначальное состояние) которого подключен к выходу элемента ИЛИ-НЕ, входы которого подключены к выходам элементов И. 1 ил. с 9 (Л С

| СПОСОБ ОБРАБОТКИ ЭЛЕКТРОКАРДИОСИГНАЛА В ДИНАМИКЕ ДЛЯ ДИАГНОЗА ИНФАРКТА МИОКАРДА | 2001 |

|

RU2217045C2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1977 |

|

SU651412A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-17—Подача