И

. Изобретение относится к автоматике и вычислительной технике. I Цель изобретения - повышение быстродействия регистра.

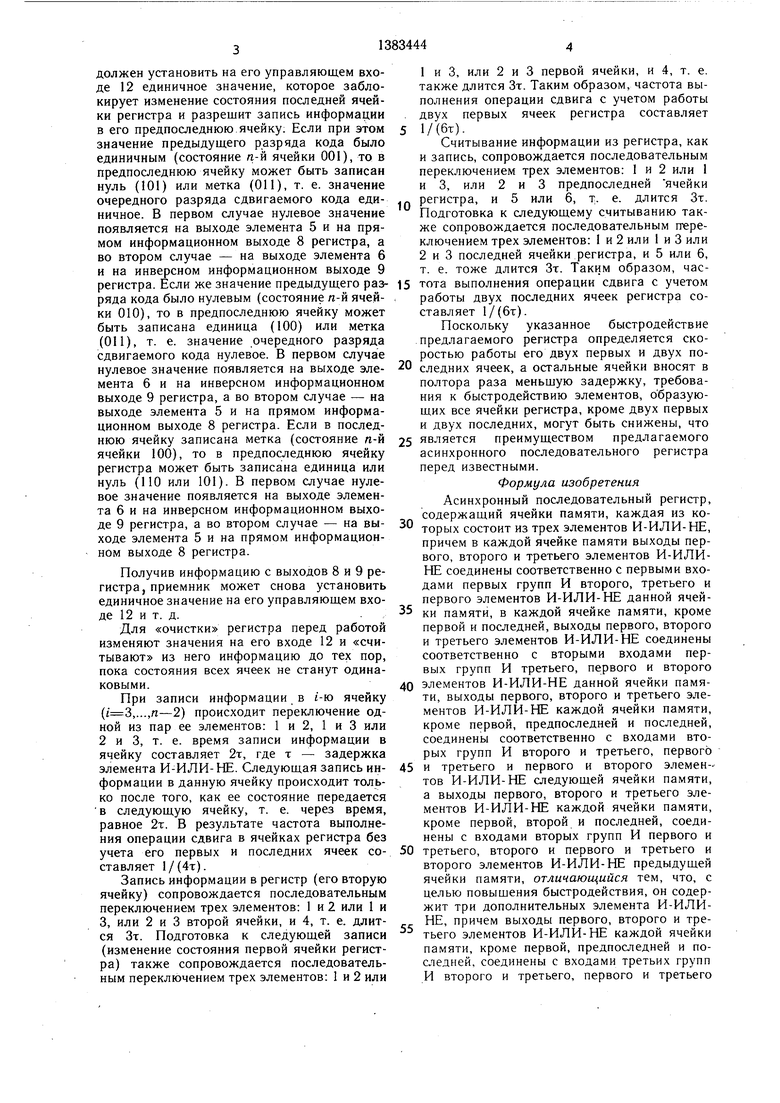

На чертеже приведена схема регистра.

Регистр состоит из п ячеек памяти, каждая из которых содержит три элемента И-ИЛИ-НЕ 1-3, и трех дополнительных Элементов И-ИЛИ-НЕ 4-6, выходы которых (;оединены с управляющим 7, прямым 8 и инверсным 9 информационными выходами

Регистра. Входы элемента 4 соединены с вы- одами элементов 1-3 первой и второй , чеек, входы которых соединены с прямым 10 и инверсным 11 информационными входами 1|)егистра. Входы элементов 5 и 6 соединены с выходами элементов 1-3 «-Й и (п-1)-й $ч.еек (последней и предпоследней соответ- { твенно), входы которых соединены с управ- яющим входом 12 регистра. Выходы эле- ijieHTOB 1-3 каждой ячейки регистра соеди- с входами элементов 2, 3, 1 и 3, 1,2 той е ячейки. Выходы элементов 1-3 /-и , 2,...,п-2) и п-й ячеек регистра сое- 1инены с входами элементов 2, 3, 1 и 3, 1,2 t /-f 1)-и и (j- 1) -и ячеек соответственно. Выходы элементов 1-Зг -й ячейки (,...,п-1) Соединены с входами каждого из элемен- toB (г-1)-й ячейки. Выходы элементов 1-3 15торой и (i-1)-й ячеек соединены с входами Элементов 1-3 первой и п-й ячеек соответственно.

: Асинхронный последовательный регистр работает следующим образом.

: Каждая г-я ячейка (, 3,...,п-1) имеет tpH устойчивых состояния (значения выходов ее элементов 1-3):101 - в ячейке записан нуль, ПО - в ячейке записана еди- Иица, 011 - значение разряда сдвигаемого кода, записанного в ячейку, совпадает Со значением предыдущего разряда, т. е. В ячейку записана метка. Благодаря блокирующим связям с выходов элементов 1-3 последующей (/+1)-й ячейки с входами элементов 1-3 данной изменение ее состояния Становится возможным только после того, как состояния данной и последующей ячеек одинаковы. Перепись информации из предыдущей (г-1)-й ячейки в данную возможна только после того, как информация, записанная ранее в данную ячейку, переписывается в последующую ячейку.

При записи очередного состояния в i-ю ячейку она переходит из одного из указанных состояний в другое через транзитные состояния 100, 010 или 001. Поскольку /-я ячейка Изменяет свое состояние при подаче соответствующего количества единичных значений на входы ее элементов 1-3, то она воспринимает только устойчивые состояния соседних с ней (i-1)-й и (/-+-)-и ячеек, а их транзитные состояния не воспринимает, г. е. последние не нарушают правильного функционирования регистра.

0

Первая и последняя п-я ячейки регистра имеют устойчивые состояния (значения выходов элементов 1-3), отличные от таковых у всех остальных его ячеек, а именно 100 - в ячейке записана метка, 010 - в ячейке записан нуль, 001 - в ячейке записана единица, а транзитные состояния 110, 101 и 011. Когда на обоих информационных входах 10 и 11 регистра имеются нулевые значения, т. е. информация на этих входах отсутствует, состояние второй ячейки регистра переписывается в его первую ячейку, причем значения выходов одноименных элементов этих ячеек становятся противоположными. В результате на одном из входов каждой группы И элемента 4 появляется нулевое значение, а на выходе этого элемента и управляющем выходе 7 регистра - единичное значение. При этом изменение состояния второй ячейки регистра блокируется нулевыми значениями на его входах 10 и И.

0 Приняв единичное значение с выхода 7 регистра, источник информации может подать очередной разряд сдвигаемого кода на его входы 10 и 11, т. е. установить на одном из них единичное значение. При этом состоя ние второй ячейки регистра изменяется следующим образом. При единичном значении на входе 10 во вторую ячейку записывается единица (ПО), если в первой ячейке записана метка (100) или нуль (010), а если в первой ячейке записана единиQ ца (001, то во вторую ячейку записывается метка (011). При единичном значении на входе 11 во вторую ячейку записывается нуль (101), если в первой ячейке записана метка (100) или единица (001), а если в первой ячейке записан нуль (010), то

с ВО вторую ячейку записывается метка (011). В результате на входах одной из групп И элемента 4 появляются единичные значения, а на выходе этого элемента и управляющем выходе 7 регистра - нулевое значение. При этом изменение состояния первой

0 ячейки регистра блокируется единичным значением на его входе 10 или 11.

Приняв нулевое значение с выхода 7 регистра, источник информации может снова установить на входах 10 и 11 регистра нулевые значения, т. е. снять информацию с этих входов и т. д.

Когда на управляющем входе 12 регистра имеется нулевое значение, изменение состояния предпоследней ячейки регистра заблокировано и разрешена перепись ее состояния в его последнюю ячейку, причем значения выходов одноименных элементов этих ячеек становятся противоположными. В результате на одном из входов каждой группы И элементов 5 и 6 появляется нулевое значение, а на выходах этих элементов и на 5 информационных выходах 8 и 9 регистра - единичные значения, т. е. информация на этих выходах отсутствует. Для того, чтобы считать информацию из регистра, приемник

5

0

должен установить на его управляющем входе 12 единичное значение, которое заблокирует изменение состояния последней ячейки регистра и разрешит запись информации в его предпоследнюю ячейку. Если при этом значение предыдущего разряда кода было единичным (состояние п-й ячейки 001), то в предпоследнюю ячейку может быть записан нуль (101) или метка (011), т. е. значение очередного разряда сдвигаемого кода единичное. В первом случае нулевое значение появляется на выходе элемента 5 и на прямом информационном выходе 8 регистра, а во втором случае - на выходе элемента 6 и на инверсном информационном выходе 9 регистра. Если же значение предыдущего разряда кода было нулевым (состояние л-й ячейки 010), то в предпоследнюю ячейку может быть записана единица (100) или метка (Oil), т. е. значение очередного разряда сдвигаемого кода нулевое. В первом случае нулевое значение появляется на выходе элемента 6 и на инверсном информационном выходе 9 регистра, а во втором случае - на выходе элемента 5 и на прямом информационном выходе 8 регистра. Если в последнюю ячейку записана метка (состояние «-и ячейки 100), то в предпоследнюю ячейку регистра может быть записана единица или нуль (ПО или 101). В первом случае нулевое значение появляется на выходе элемента 6 и на инверсном информационном выходе 9 регистра, а во втором случае - на выходе элемента 5 и на прямом информационном выходе 8 регистра.

Получив информацию с выходов 8 и 9 регистра, приемник может снова установить единичное значение на его управляющем входе 12 и т. д.

Для «очистки регистра перед работой изменяют значения на его входе 12 и «считывают из него информацию до тех пор, пока состояния всех ячеек не станут одинаковыми.

При записи информации в г -ю ячейку (/ 3п-2) происходит переключение одной из пар ее элементов: 1 и 2, 1 и 3 или 2 и 3, т. е. время записи информации в ячейку составляет 2т, где т - задержка элемента И-ИЛИ-НЕ. Следующая запись информации в данную ячейку происходит только после того, как ее состояние передается в следующую ячейку, т. е. через время, равное 2т. В результате частота выполнения операции сдвига в ячейках регистра без учета его первых и последних ячеек составляет 1/(4т).

Запись информации в регистр (его вторую ячейку) сопровождается последовательным переключением трех элементов: 1 и 2 или 1 и 3, или 2 и 3 второй ячейки, и 4, т. е. длится 3т. Подготовка к следующей записи (изменение состояния первой ячейки регистра) также сопровождается последовательным переключением трех элементов: 1 и 2 или

1и 3, или 2 и 3 первой ячейки, и 4, т. е. также длится 3т. Таким образом, частота выполнения операции сдвига с учетом работы

. двух первых ячеек регистра составляет

1/(6т).

Считывание информации из регистра, как и запись, сопровождается последовательным переключением трех элементов: 1 и 2 или 1 и 3, или 2 и 3 предпоследней ячейки

,. регистра, и 5 или б, т. е. длится 3т. Подготовка к следующему считыванию также сопровождается последовательным переключением трех элементов: 1 и 2 или 1 и 3 или

2и 3 последней ячейки регистра, и 5 или 6, т. е. тоже длится 3т. Таким образом, час5 тота выполнения операции сдвига с учетом работы двух последних ячеек регистра составляет 1/(бт).

Поскольку указанное быстродействие предлагаемого регистра определяется скоростью работы его двух первых и двух по0 следних ячеек, а остальные ячейки вносят в полтора раза меньщую задержку, требования к быстродействию элементов, о бразую- щих все ячейки регистра, кроме двух первых и двух последних, могут быть снижены, что

5 является преимуществом предлагаемого асинхронного последовательного регистра перед известными.

Формула изобретения Асинхронный последовательный регистр, содержащий ячейки памяти, каждая из ко торых состоит из трех элементов И-ИЛИ-НЕ, причем в каждой ячейке памяти выходы первого, второго и третьего элементов И-ИЛИ- НЕ соединены соответственно с первыми входами первых групп И второго, третьего и первого элементов И-ИЛИ-НЕ данной ячей5 ки памяти, в каждой ячейке памяти, кроме первой и последней, выходы первого, второго и третьего элементов И-ИЛИ-НЕ соединены соответственно с вторыми входами первых групп И третьего, первого и второго

0 элементов И-ИЛИ-НЕ данной ячейки памяти, выходы первого, второго и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, предпоследней и последней, соединены соответственно с входами вторых групп И второго и третьего, первого

5 и третьего и первого и второго элементов И-ИЛИ-НЕ следующей ячейки памяти, а выходы первого, второго и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, второй и последней, соединены с входами вторых групп И первого и

0 третьего, второго и первого и третьего и второго элементов И-ИЛИ-НЕ предыдущей ячейки памяти, отличающийся тем, что, с целью повыщения быстродействия, он содержит три дополнительных элемента И-ИЛИ- НЕ, причем выходы первого, второго и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, предпоследней и последней, соединены с входами третьих групп И второго и третьего, первого и третьего

и первого и второго элементов И-ИЛИ-НЕ последующей ячейки памяти, выходы первого, второго и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, второй и последней, соединены с входами третьих групп И первого и второго, второго и третьего и третьего и первого эле- м(нтов И-ИЛИ-НЕ предыдущей ячейки па мяти соответственно, выходы первого, второго; и третьего элементов И-ИЛИ-НЕ каждой

выходы первого, второго и третьего элеме - тов И-ИЛИ-НЕ второй (предпоследней) ячейки памяти соединены со вторыми входами вторых и третьих групп И первого, второго и третьего элементов И-ИЛИ-НЕ первой (последней) ячейки памяти и первой, второй и третьей групп И первого (второго и третьего) дополнительного элемента И-ИЛИ.НЕ, выходы первого, второго и третьего элементов И-ИЛИ-НЕ предпоследней

я4ейки памяти, кроме первой и последней, 10 ячейки памяти соединены соответственно с со|единены с входами второй группы третье-вторыми входами вторых и третьих групп И

го|, первого и второго элементов И-ИЛИ-НЕ первого, второго и третьего элементов ИИЛИ-НЕ последней ячейки памяти и первой, второй и третьей групп И второго и третьего дополнительных элементов И-ИЛИ-НЕ, выходы первого, второго и третьего дополнительных элементов И-ИЛИ-НЕ являются соответственно управлйющим, прямым и инверсным информационными выходами регистра, прямой информационный вход котовфтых групп И третьего, первого и второго 20 Рого соединен с вторыми входами первых эфментов И-ИЛИ-НЕ даппой ячейки памятигрупп И первого и третьего и четвертой

группы И третьего элементов И-ИЛИ-НЕ первой ячейки и вторых групп И первого и третьего и третьей группы И третьего элементов И-ИЛИ-НЕ второй ячейки, инверсяцейки, а также с первыми входами первой, 25 ный информационный вход - с вторыми вхо- В1|орой и третьей групп И первого допол-дами четвертых групп И первого и вто рого и первой группы И второго эле

ментов И-ИЛИ-НЕ первой ячейки и третьих групп И первого и второго и второй группы И второго элементов И-ИЛИ-НЕ второй

д4нной ячейки памяти соответственно и с вхо- д4ми третьей группы второго, третьего и первого элементов И-ИЛИ-НЕ данной ячейки п4мяти соответственно, выходы первого, вто- рс|го и третьего элементов И-ИЛИ-НЕ пер- вс|й ячейки памяти соединены соответствен- н0 с первыми входами вторых групп И Bijoporo, третьего и первого и третьих и чети входами вторых групп И второго и третьего, третьих групп И первого и третьего и В1|орой группы И первого и третьей груп- niji И второго элементов И-ИЛИ-НЕ второй

Н1|тельного элемента И-ИЛИ-НЕ, выходы пе|рвого, второго и третьего элементов И- И|ПИ-НЕ последней ячейки памяти соедине- нф соответственно с первыми входами вторфх групп И второго, третьего и первого 30 ячейки, а управляющий вход - с вторыми

третьих и четвертых групп И третьего, пе|рвого и второго элементов И-ИЛИ-НЕ дг|нной ячейки памяти и входами вторых rpiynn И второго и третьего, третьих групп И: первого и третьего и второй группы И

входами первых и четвертых групп И всех элементов И-ИЛИ-НЕ последней ячейки и вторых и третьих групп И первого, второго и третьего элементов И-ИЛИ-НЕ предпоследней ячейки, выходы которых соединены с

первого и третьей группы И второго эле-35 третьими входами третьей группы И второго мантов И-ИЛИ-Ж предпоследней ячейки па-и второй группы И третьего, первой и , а также с первыми входами первой,третьей групп И третьего и первой и вто- и третьей групп И второго и третье-рой групп И второго дополнительных эле- га дополнительных элементов И-ИЛИ-НЕ,кентов И-ИЛИ-НЕ.

выходы первого, второго и третьего элеме - тов И-ИЛИ-НЕ второй (предпоследней) ячейки памяти соединены со вторыми входами вторых и третьих групп И первого, второго и третьего элементов И-ИЛИ-НЕ первой (последней) ячейки памяти и первой, второй и третьей групп И первого (второго и третьего) дополнительного элемента И-ИЛИ.НЕ, выходы первого, второго и третьего элементов И-ИЛИ-НЕ предпоследней

ячейки памяти соединены соответственно с вторыми входами вторых и третьих групп И

ячейки, а управляющий вход - с вторыми

входами первых и четвертых групп И всех элементов И-ИЛИ-НЕ последней ячейки и вторых и третьих групп И первого, второго и третьего элементов И-ИЛИ-НЕ предпоследней ячейки, выходы которых соединены с

третьими входами третьей группы И второго и второй группы И третьего, первой и третьей групп И третьего и первой и вто- рой групп И второго дополнительных эле- кентов И-ИЛИ-НЕ.

е /2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1987 |

|

SU1499406A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Асинхронный последовательный регистр | 1985 |

|

SU1372361A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| Устройство программного управления | 1991 |

|

SU1781671A1 |

| Регистр сдвига | 1987 |

|

SU1439682A1 |

Изобретение относится к вычислительной технике. С целью повышения быстродействия в регистр, содержаш,ий ячейки памяти, каждая из которых построена по схеме трехстабильного триггера из трех элементов И-ИЛИ-НЕ, выходы которых соединены с входами элементов И-ИЛИ-НЕ предыдуш,ей и последуюшей ячеек, введены три дополнительных элемента И-ИЛИ-НЕ, входы первого из которых соединены с выходами элементов И-ИЛИ-НЕ двух первых ячеек, а выход является управляющим выходом регистра, выходы двух упругих дополнительных элементов И-ИЛИ-НЕ соединены с выходами элементов И-ИЛИ-НЕ двух последних ячеек, а выходы дополнительных элементов И- ИЛИ-НЕ являются прямыми и инверсными информационными выходами регистра. 1 ил.

Ячейка п

Ячейка (п-и

Ячейка 1

Ячейка 2

Ячейка 1

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-03-23—Публикация

1986-04-07—Подача