Изобретение относится к вьтисли- тельной технике и может быть использовано для построения: надежных, запоминающих устройств.

Цель изобретения - повьЕиение надежности устройства.

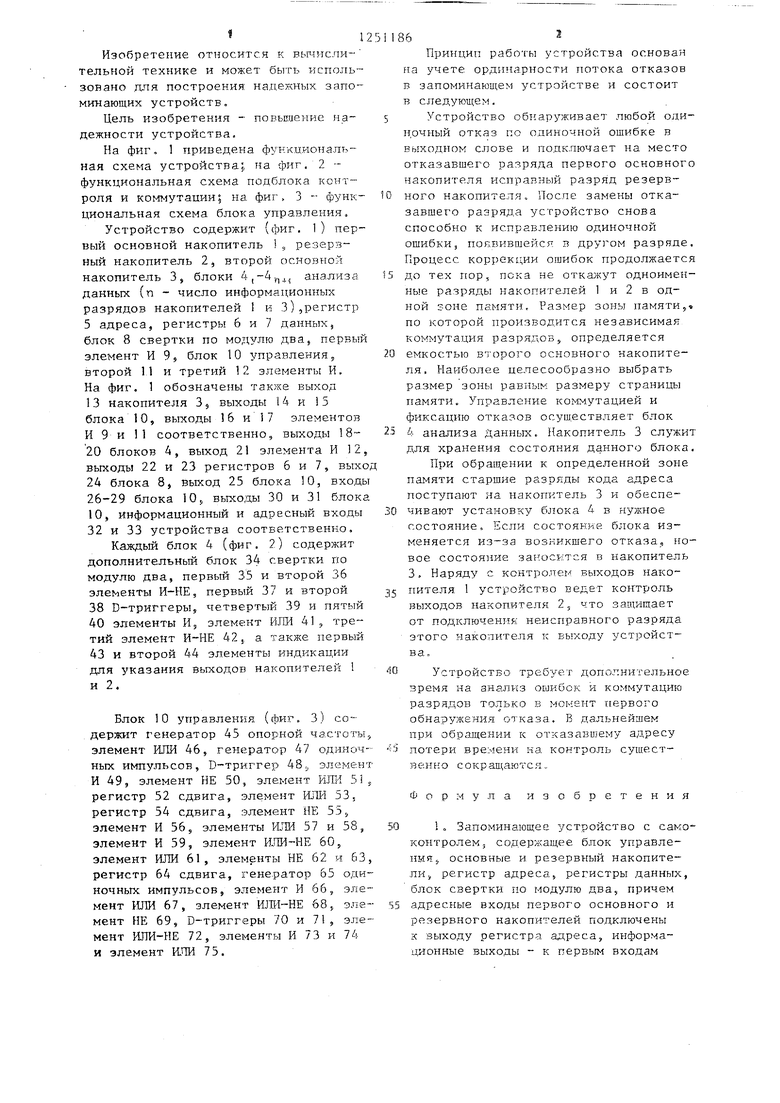

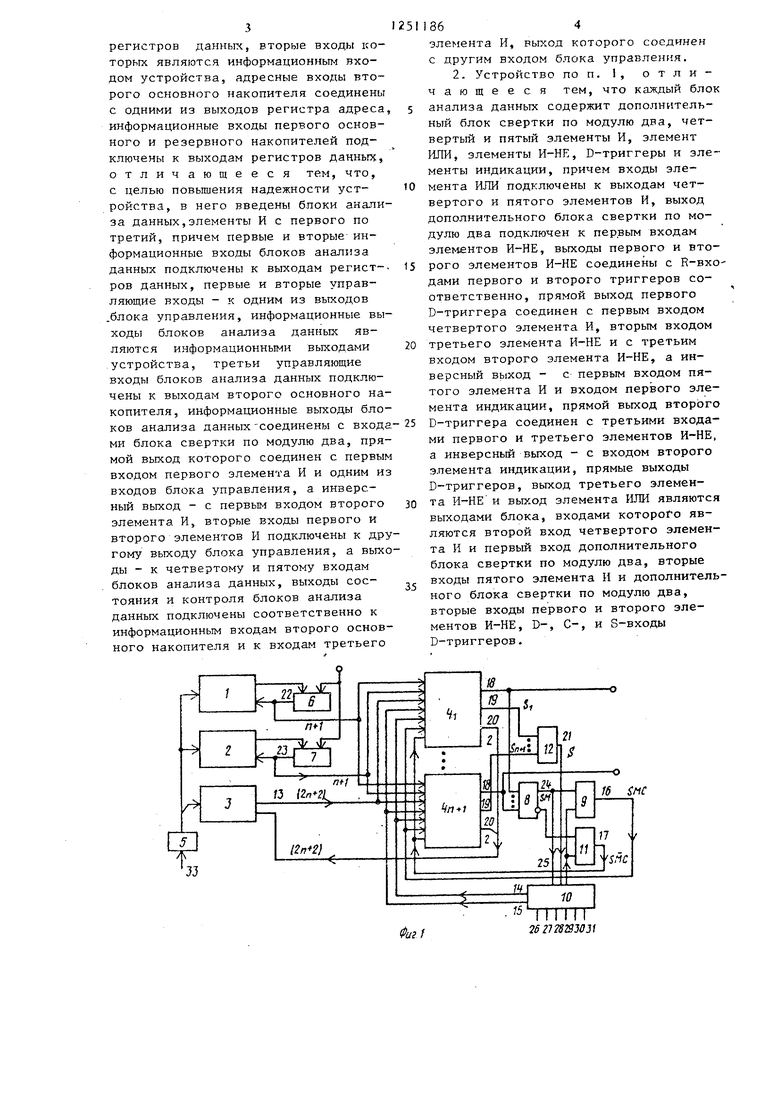

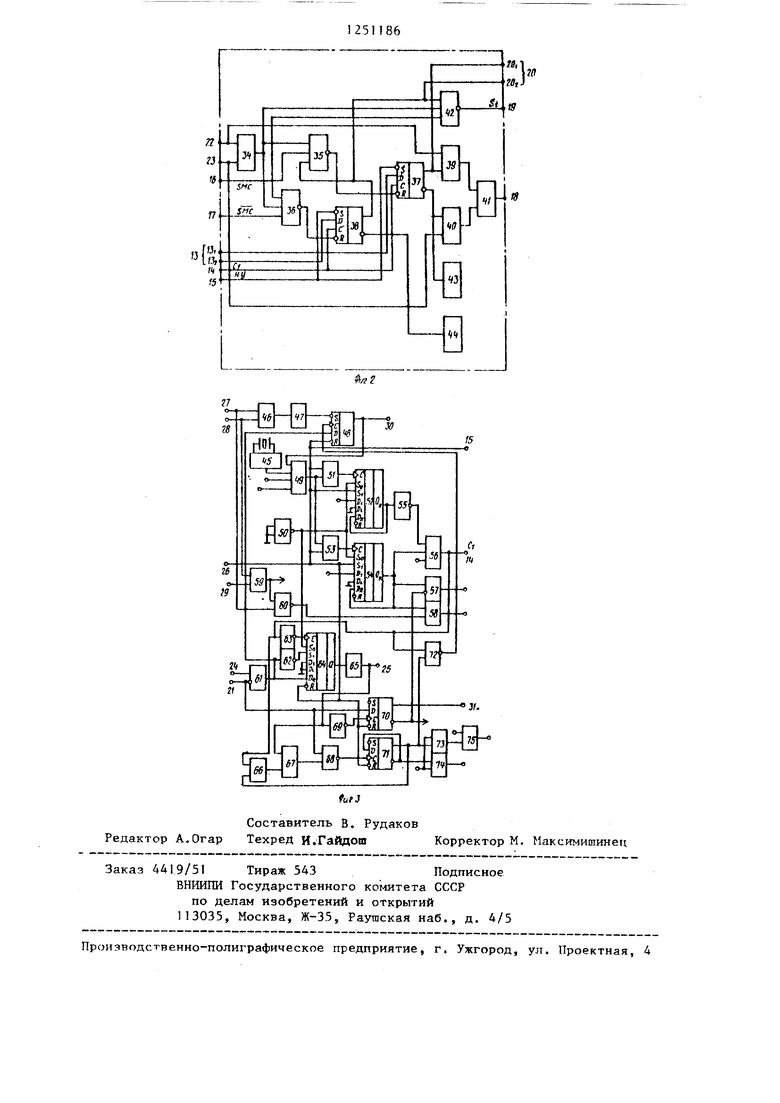

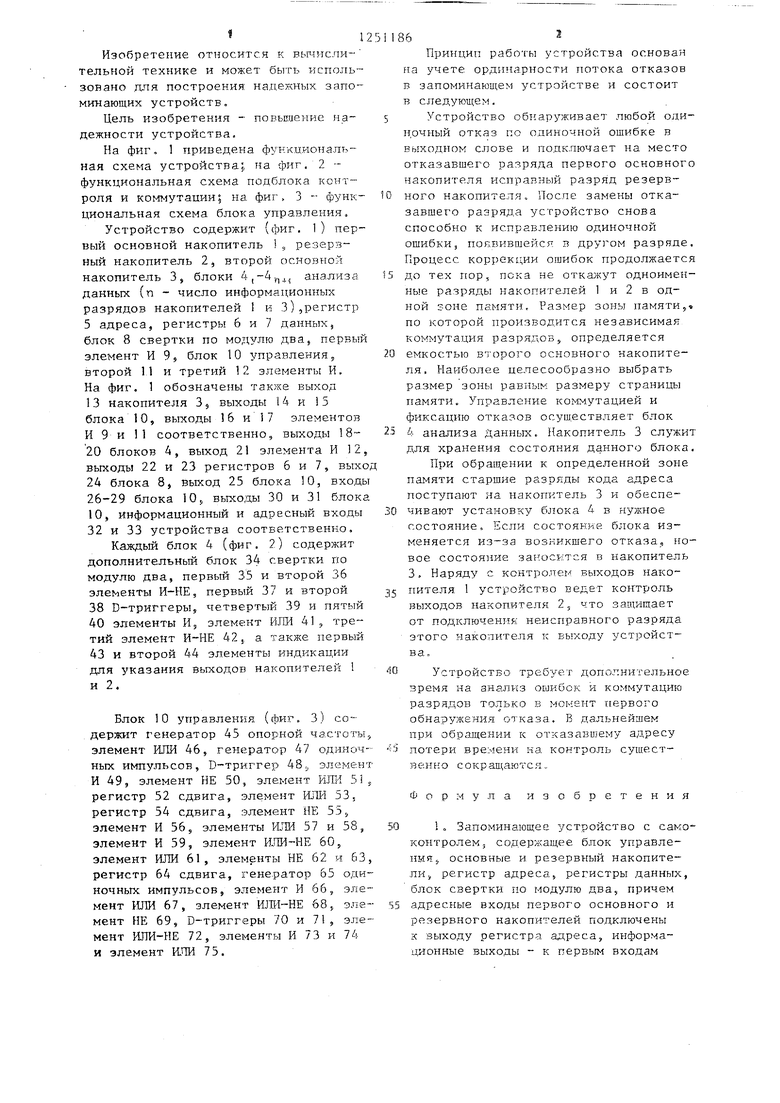

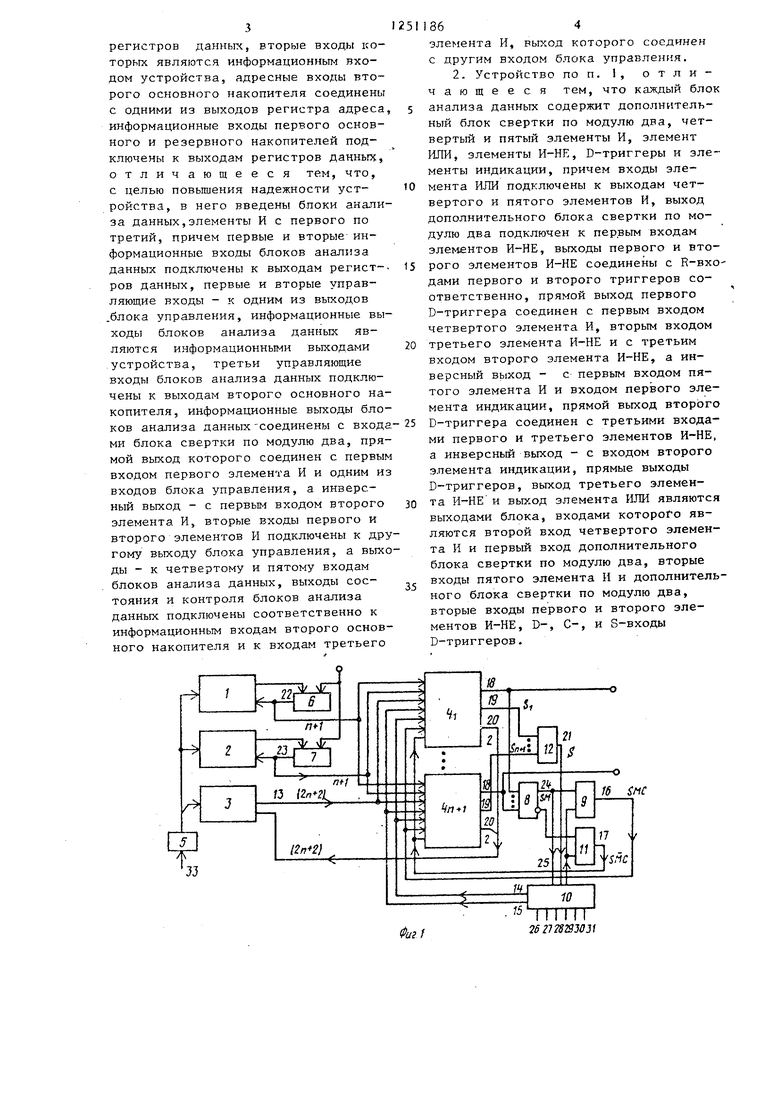

На фиг, 1 приведена функциональная схема устройства;, на фиг, 2 - функциональная схема подблока контроля и коммутации; на фиг, 3 - функциональная схема блока управления.

Устройство содержит {фиг, 1) первый основной накопитель ,, резервный накопитель 2, второй основной накопитель 3, блоки 4,-4у,. анализа данных {п - число информационных разрядов накопителей и З),регистр 5 адреса, регистры 6 и 7 данных, блок 8 свертки по модулю два, первый элемент И 9, блок 10 управления, второй 11 и третий 12 элементы И, На фиг. 1 обозначены также выход 13 накопителя 3, выходы 14 и i 5 блока 10, выходы 16 и 17 элементов И 9 и 11 соответственно, выходы 18- 20 блоков 4, выход 21 элемента И 12, выходы 22 и 23 регистров 6 и 7, выхо 24 блока В, выход 25 блока 10, входы 26-29 блока 10,, выходы 30 и 31 блока 10, информационный и адресный входы 32 и 33 устройства соответственно, Калсдый блок 4 (фиг, 2) содержит дополнительный блок 34 свертки по модулю два, первый 35 и второй 36 элементы И-НЕ, первый 37 и второй 38 В-триггеры, четвертый 39 и пятый 40 элементы И, элемент ИЛИ 41,, третий элемент 42, а также первый 43 и второй 44 элементы кгндикации для указания выходов накопителей и 2.

Блок 10 управлен$1Я (фи, 3) содержит генератор 45 опорной частоты, элемент ИЛИ 46, генератор 47 одиноч- ных импульсов, D-триггер 48,, элемент И 49, элемент НЕ 50, элемент liJE-l 51; регистр 52 сдвига, элемент ИЛИ 53, регистр 54 сдвига, элемент НЕ 55j элемент И 56, элементы ИЛИ 57 и 58, элемент И 59, элемент И.ПИ-НЕ 60, элемент ИЛИ 61, элементы НЕ 62 и 63 регистр 64 сдвига, генератор 65 о,цн- ночных импульсов, элемент И 66, элемент ИЛИ 67, элемент ШШ-НЕ 68, эле- мент НЕ 69, D-триггеры 70 и 71, элемент ИЛИ-НЕ 72, элементы И 73 и 74 и элемент ШШ 75.

Принцип работы устройства основан на учете ординарности потока отказов в запоминающем устройстве и состоит в следующем.

Устройство обнаруживает любой оди нрчный отказ по одиночной ошибке в выходном слове и подключает на место отказавшего разряда первого основног накопителя исправный разряд резервного накопителя. После замены отказавшего разряда устройство снова способно к исправлению одиночной ошибки, появившейся в дру)ом разряде Г1роцесс коррекции ошибок продолжаетс до тех пор, пока не откажут одноименные разряды накопителей 1 и 2 в одной soHB памяти. Размер зоны памяти,, по которой производится независимая коммутация разрядов, определяется емкостью второго основного накопителя. Наиболее целесообразно выбрать разм€;р зоны равным размеру страницы памяти. Управление коммутацией и фиксацию отказов осуществляет блок 4 анализа данных. Накопитель 3 служи для хранения состояния данного блока

При обращении к определенной зоне памяти старшие разряды кода адреса поступают на накопитель 3 и обеспечивают установку блока 4 в нужное состояние. Если состояние блока Изменяется из-за возникшего отказа, новое состояние заносится в накопитель 3. Наряду с контроле. выходов накопителя 1 устройство ведет коцтроль выходов накопителя 2, что защищает от подключения неисправного разряда этого накопителя к выходу устройства.

Устройство требует дополнительное время на анализ ошибок и коммутацию разрядов только в момент -первого обнаружения отказа. В дальнейшем при обращении к отказавшему адресу потери времени ка контроль существенно сокращаются.

Формула изобретения

1 о Запоминающее устройство с самоконтролем, содержащее блок управления основные и резервный накопители, регистр адреса, регистры данных, блок свертки по модулю два, причем адресные входы первого основного и резервного накопителей подключены к выходу регистра адреса, информационные выходы - к первьгм входам

3

регистров данных, вторые входы которых являются информационным входом устройства, адресные входы второго основного накопителя соединены с одними из выходов регистра адреса информационные входы первого основного и резервного накопителей подключены к выходам регистров данные, отличающееся тем, что, с целью повьшения надежности уст- ройства, в него введены блоки анализа данных,элементы И с первого по третий, причем первые и вторые информационные входы блоков анализа данных подключены к выходам регистров данных, первые и вторые управляющие входы - к одним из выходов .блока управления, информационные выходы блоков анализа данных являются информационными выходами .устройства, третьи управляющие входы блоков анализа данных подключены к выходам второго основного накопителя, информационные выходы блоков анализа данных соединены с входа ми блока свертки по модулю два, прямой выход которого соединен с первым входом первого элемента И и одним из входов блока управления, а инверсный выход - с первьм входом второго элемента И, вторые входы первого и второго элементов И подключены к другому выходу блока управления, а выходы - к четвертому и пятому входам блоков анализа данных, выходы сое- тояния и контроля блоков анализа данных подключены соответственно к информационным входам второго основного накопителя и к входам третьего

1864

элемента И, выход которого соединен с другим входом блока управления.

2. Устройство по п. 1, отличающееся тем, что каждый бло анализа данных содержит дополнительный блок свертки по модулю два, четвертый и пятый элементы И, элемент ИЛИ, элементы И-НЕ, D-триггеры и элементы индикации, причем входы элемента ИЛИ подключены к выходам четвертого и пятого элементов И, выход дополнительного блока свертки по модулю два подключен к первым входам элементов И-НЕ, выходы первого и второго элементов И-НЕ соединены с R-вхо дами первого и второго триггеров соответственно, прямой выход первого D-триггера соединен с первым входом четвертого элемента И, вторым входом третьего элемента И-НЕ и с третьим входом второго элемента И-НЕ, а инверсный вь1ход - с первым входом пятого элемента И и входом первого элемента индикации, прямой выход второго D-триггера соединен с третьими входами первого и третьего элементов И-НЕ, а инверсный выход - с входом второго элемента индикации, прямые выходы D-триггеров, выход третьего элемента И-НЕ и выход элемента ИЛИ являются выходами блока, входами которого являются второй вход четвертого элемента И и первый вход дополнительного блока свертки по модулю два, вторые входы пятого элемента И и дополнительного блока свертки по модулю два, вторые входы первого и второго элементов И-НЕ, D-, С-, и S-входы D-триггеров.

Фиг.

25 27 262330 Л

П

a

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU972601A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения надежных запоминающих устройств. Цель изобретения - повьппение надежности устройства. Устройство содержит основные и резервный накопители, блоки анализа данных по числу информационных разрядов основных накопителей, регистры данных, регистр адреса, блок свертки по модулю два, блок управления и элементы И. Принцип работы устройства основан на учете ординарности потока отказов в запоми- накяцем устройстве. Устройство обнаруживает любой одиночный отказ по одиночной ошибке в выходном слове и подключает на место отказавшего разряда первого основного накопителя исправный разряд резервного накопителя. После замены отказавшего разряда устройство снова способно к исправлению одиночной ошибки, появившейся в другом разряде, 1 з.п. ф-лы, 3 ил. § СП С

5

fufJ

Составитель В. Рудаков Редактор А.Огар Техред И.Гайдош

Заказ 4419/51 Тираж 543Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор М, Максимишинец

| Резервированное запоминающее устройство | 1978 |

|

SU720539A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1984-09-13—Подача