1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам,, и может быть использовано в составе специализированных цифровых вычислительных ManjHH и в устройствах обработки с предварительной выборкой информации из запоминающего устройства.

Цель изобретения - повышение надежности устройства.

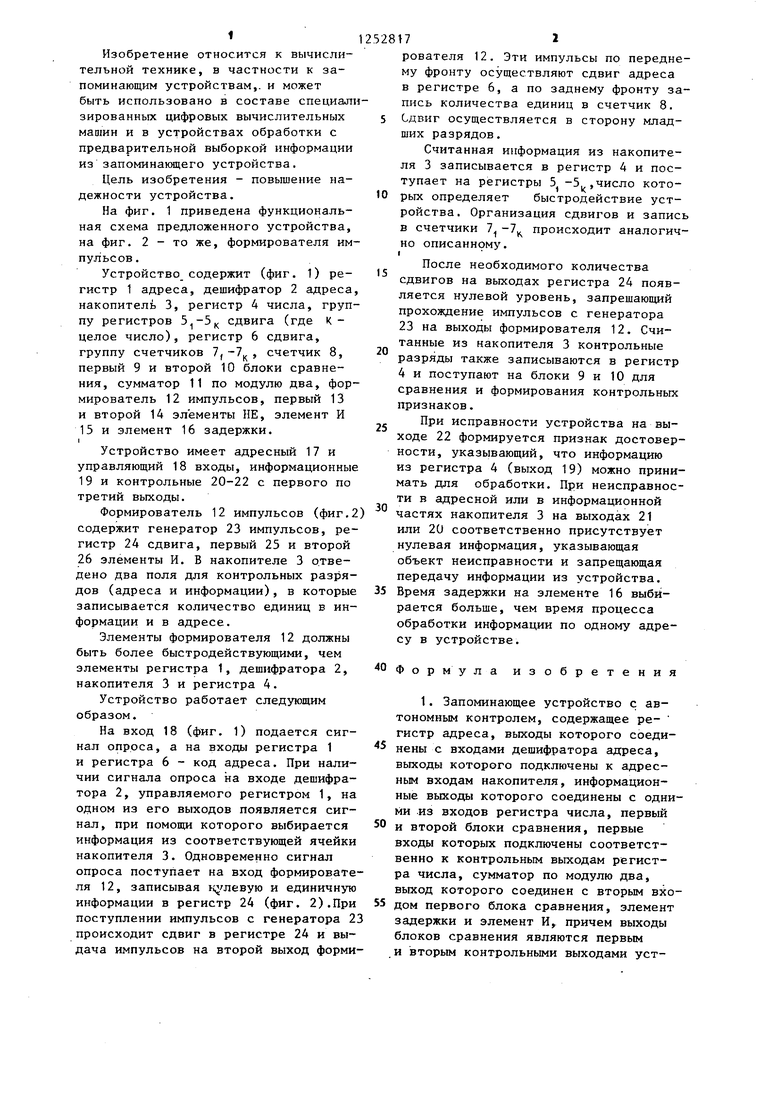

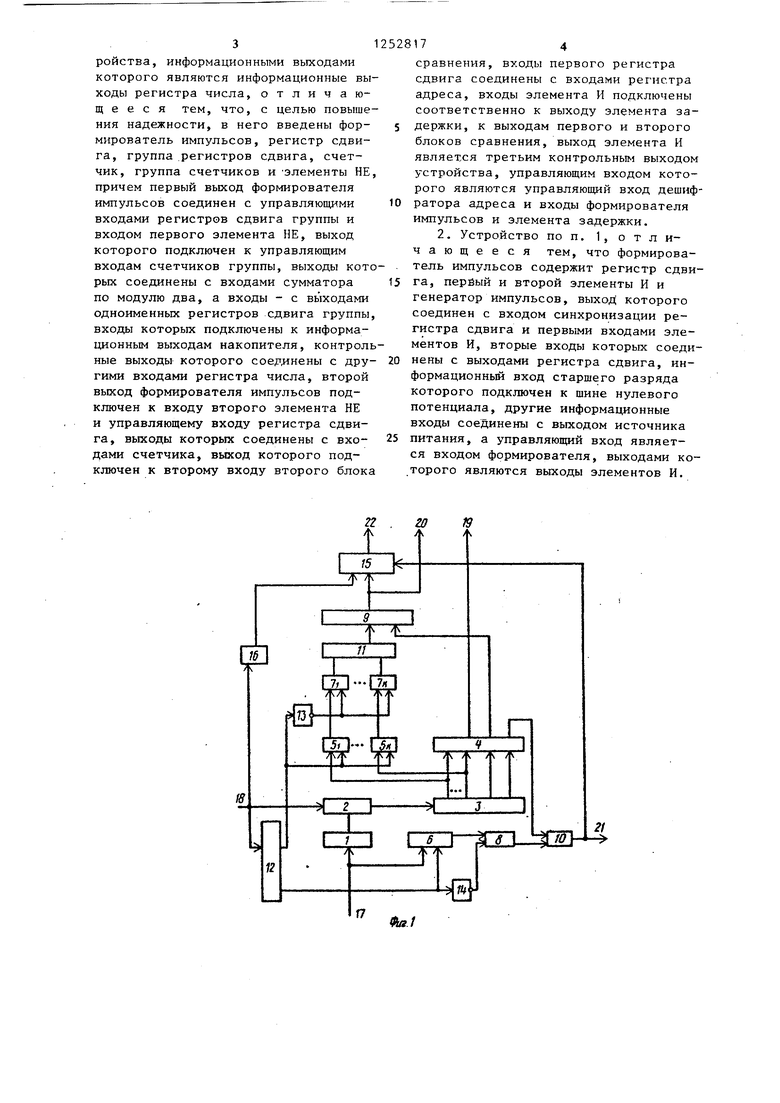

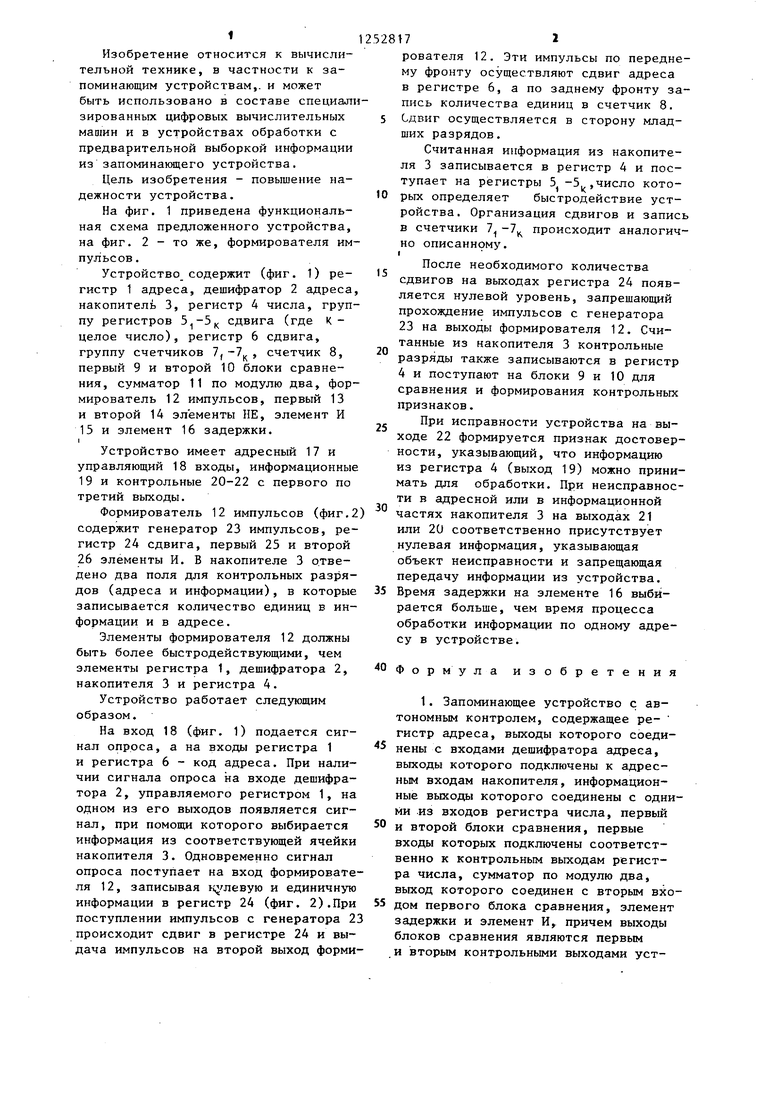

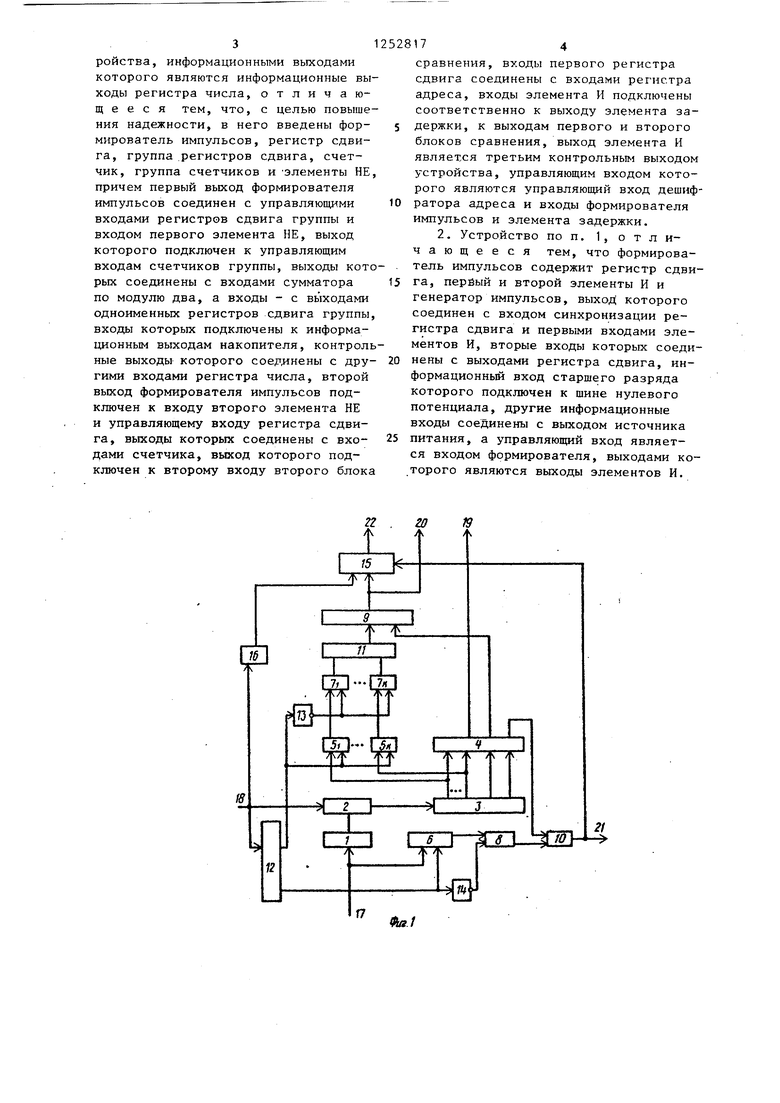

На фиг. 1 приведена функциональная схема предложенного устройства, на фиг. 2 - то же, формирователя импульсов.

Устройство содержит (фиг. 1) ре- гистр 1 адреса, дешифратор 2 адреса, накопитель 3, регистр 4 числа, группу регистров сдвига (где К- целое число), регистр 6 сдвига, группу счетчиков 7,-7| , счетчик 8, первый 9 и второй 10 блоки сравнения, сумматор 11 по модулю два, формирователь 12 импульсов, первый 13 и второй 14 элементы НЕ, элемент И

15 и элемент 16 задержки. I

Устройство имеет адресный 17 и управляющий 18 входы, информационные 19 и контрольные 20-22 с первого по третий выходы.

Формирователь 12 импульсов (фиг.2 содержит генератор 23 импульсов, регистр 24 сдвига, первый 25 и второй 26 элементы И. В накопителе 3 отведено два поля для контрольных разрядов (адреса и информации), в которые записывается количество единиц в информации и в адресе.

Элементы формирователя 12 должны быть более быстродействующими, чем элементы регистра 1, дешифратора 2, накопителя 3 и регистра 4.

Устройство работает следующим образом.

На вход 18 (фиг. 1) подается сигнал опроса, а на входы регистра 1 и регистра 6 - код адреса. При наличии сигнала опроса на входе дешифратора 2, управляемого регистром 1, на одном из его выходов появляется сигнал, при помощи которого выбирается информация из соответствующей ячейки накопителя 3. Одновременно сигнал опроса поступает на вход формирователя 12, записывая шевую и единичную информации в регистр 24 (фиг. 2).При поступлении импульсов с генератора 2 происходит сдвиг в регистре 24 и выдача импульсов на второй выход форми

мг

рователя 12. Эти импульсы по переднему фронту осуществляют сдвиг адреса в регистре 6, а по заднему фронту запись количества единиц в счетчик 8. Сдвиг осуществляется в сторону младших разрядов.

Считанная информация из накопителя 3 записывается в регистр 4 и поступает на регистры 5 -5,число которых определяет быстродействие устройства. Организация сдвигов и запись в счетчики происходит аналогично описанному. I

После необходимого количества сдвигов на выходах регистра 24 появляется нулевой уровень, запрешающий прохождение импульсов с генератора 23 на выходы формирователя 12. Считанные из накопителя 3 контрольные разряды также записываются в регистр 4 и поступают на блоки 9 и 10 для сравнения и формирования контрольных признаков.

При исправности устройства на выходе 22 формируется признак достоверности, указывающий, что информацию из регистра 4 (выход 19) можно принимать для обработки. При неисправности в адресной или в информационной частях накопителя 3 на выходах 21 или 20 соответственно присутствует нулевая информация, указывающая объект неисправности и запрещающая передачу информации из устройства. Время задержки на элементе 16 выбирается больше, чем время процесса обработки информации по одному адресу в устройстве.

Формула изобретения

1. Запоминающее устройство с автономным контролем, содержащее регистр адреса, выходы которого соединены с входами дешифратора адреса, выходы которого подключены к адресным входам накопителя, информационные выходы которого соединены с одними из входов регистра числа, первый и второй блоки сравнения, первые входы которых подключены соответственно к контрольным вьжодам регистра числа, сумматор по модулю два, выход которого соединен с вторым входом первого блока сравнения, элемент задержки и элемент И, причем выходы блоков сравнения являются первым и вторым контрольньти выходами уст3

ройства, информационными выходами которого являются информационные выходы регистра числа, отличающееся тем, что, с целью повышения надежности, в него введены фор- мнрователь импульсов, регистр сдвига, группа регистров сдвига, счетчик, группа счетчиков и элементы НЕ причем первый выход формирователя импульсов соединен с управляющими входами регистров сдвига группы и входом первого элемента НЕ, выход которого подключен к управляющим входам счетчиков группы, выходы кот рых соединены с входами сумматора по модулю два, а входы - с выходами одноименных регистров сдвига группы входы которых подключены к информационным выходам накопителя, контролные выходы которого с дру гими входами регистра числа, второй выход формирователя импульсов подключен к входу второго элемента НЕ и управляющему входу регистра сдвига, выходы которых соединены с вхо- дами счетчика, выход которого подключен к второму входу второго блок

сравнения, входы первого регистра сдвига соединены с входами регистра адреса, входы элемента И подключены соответственно к выходу элемента задержки, к выходам первого и второго блоков сравнения, выход элемента И является третьим контрольным выходом устройства, управляющим входом которого являются управляющий вход дешифратора адреса и входы формирователя импульсов и элемента задержки.

2. Устройство по п. 1, отличающееся тем, что формирователь импульсов содержит регистр сдвига, пербый и второй элементы И и генератор импульсов, выход которого соединен с входом синхронизации регистра сдвига и первыми входами элементов И, вторые входы которых соединены с выходами регистра сдвига, ин- формационньй вход старшего разряда которого подключен к шине нулевого потенциала, другие информационные входы соединены с выходом источника питания, а управляющий вход является входом формирователя, выходами которого являются выходы элементов И,

22

го

ю

23

Jloz. T

2

.2

Редактор О.Головач

Заказ 4625/51Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

25

2

-

Составитель Т.Зайцева

Техред Q.Сопке Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1985 |

|

SU1257709A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Устройство для управления полупровод-НиКОВыМ НАКОпиТЕлЕМ | 1979 |

|

SU842811A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено в составе специализированных ЦВМ с пре;;варительной выборкой информации из запоминающего устройства. Целью изобретения является повышение надежности устройства.Устройство содержит накопитель, регистр адреса, дешифратор адреса, регистр числа, блоки сравнения, сумматор по модулю два, группу регистров сдвига, группу счетчиков, формирователь, импульсов, счетчик, регистр 6 сдвига, элементы НЕ, элемент И, элемент задержки. Самоконтроль устройства осуществляется путем сравнения считанных из накопителя контрольных разрядов и формирования на контрольных выходах устройства признаков, указывающих на исправность или неисправность информационной и адресной частей накопителя. 1 з.п. ф-лы, 2 ил. § СО

| Запоминающее устройство с автономным контролем | 1973 |

|

SU467409A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-23—Публикация

1985-02-20—Подача