to

о

а

Изобретение относится к цифровым системзм автоматики и вычислительной техники и может быть использовано дл диагностирования неисправностей отдельных модулей этих систем.

Цель изобретения - уменьшение объема используемой памяти и расширение функциональных возможностей за счет одн6вреь енной обработки нескольких выходньгх сигналов диагнбстируемой системы.

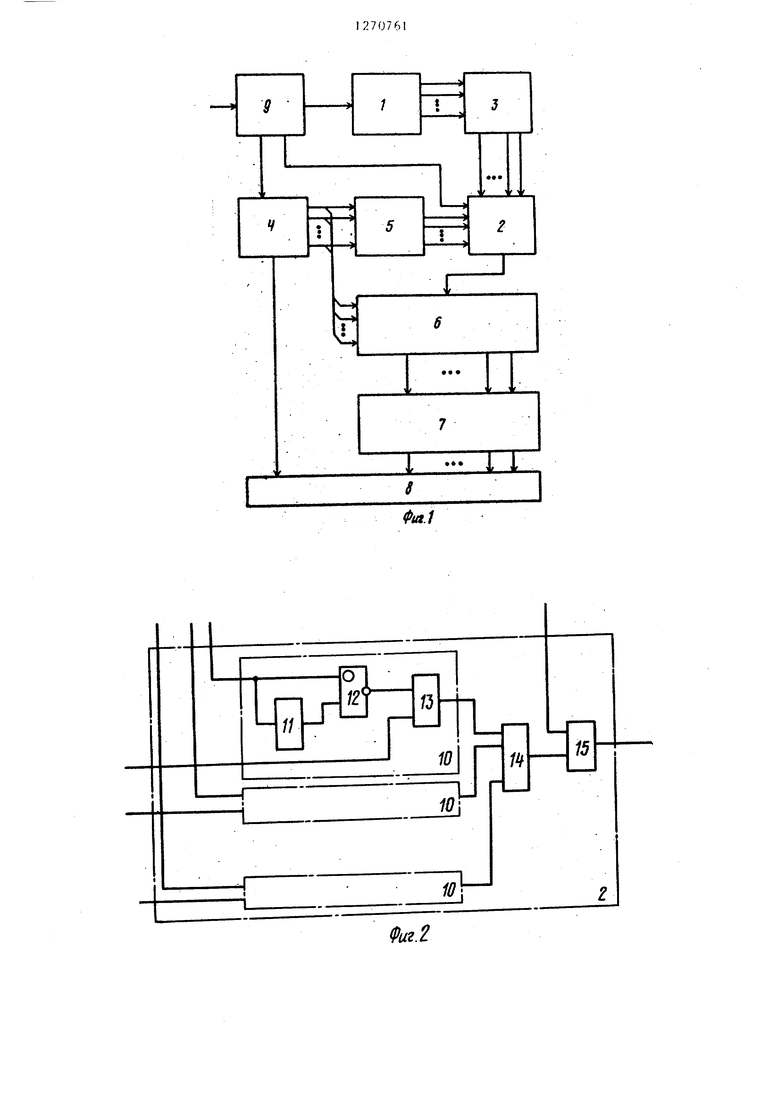

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока вьщеления признака неисправности; на фиг. 3 - 5 - функциональные схемы блока синхронизации, блока формирования адреса эталонных признаков, блока счетчиков приближений .

Устройство (фиг. 1) содержит блок 1 памяти тестов, блок 2 вьщеления признака неисправности, диагностируемзло систему 3, блок 4 формирования адреса эталонных признаков, блок 5 памяти эталонных признаков, блок 6 памяти активизируемых модулей блок 7 счетчиков приближений, блок 8 индикации, блок 9 синхронизации.

Блок выделения признака неисправности (фиг. 2) содержит п узлов 10 вьщеления признака неисправности, каждый узел 10 содержит элемент 11 задержки, элемент 12 сложения по модулю два с инверсным выходом, элемент И 13, блок выделения признака неисправности также содержит элемент ИЛИ 14 и элемент И 15. Блок синхронизации (фиг. 3) содержит элемент ИЛИ 16, одновибратор 17, элемент 18 задержки, удвоитель 19 частоты. Блок формирования адреса эталонных признаков (фиг. 4) содержит счетчик 20 и дешифратор 21.,

Блок счетчиков приближений (фиг. 5) содержит п счетчиков 22 и п дешифраторов 23. .

В основу работы устройства положено использование тестов, построенных методом активизации путей. Этот метод заключается в том, что тестовые наборы генерируются парами. Каждая пара тестовых наборов имеет одинаковые значения на всех входах диагностируемой системы, креме одного, на котором значения на наборах пары противоположны (переключение) Смысл активации путей состоит в том-, что

значения на входах подбираются такими, чтобы обеспечить продвижение переключения с входа диагностируемой системы на ее выход. При наличии неисправности на таком активизированном пути переключения на соответствующем выходе не произойдет

Блок 1 памяти тестов содержит двоичные тестовые наборы, подаваемые на входы диагностируемой системы 3. Блок 5 памяти эталонных признаков для каждой пары тестовых наборов содержит информацию, имеется ли .на каждом из выходов исправной диагностируемой системы 3 переключение 1-0 или 0-1. При наличии такого переключения в разряде выходного слова, соответствуищем одному из выходов диагностируемой системы 3, находится 1 , в противном случае 0.

Блок 6 памяти активизируемых модулей для каждой пары тестовых наборов содержит информацию о модулях диагностируемой системы, активизируемых данной парой наборов. Активизируемым счй- ается модуль, в котором на данной паре тестовых наборов хотя бы на одной линии (связи) происходит переключение 1-0 или 0-1, проявляющееся на одном из. выходов диагностируемой системы 3. Если модуль активизируется на данной паре тестовых наборов, то в разряде выходного слова, соответствующем данному модулю, находится 1 в противном случае О.Таким образрм, блоки 1, 5 и 6 могут быть реализованы на перепрограммируемых ПЗУ. Объем блока 1 памяти тестов равен (N х 2Nf,, где Ng - число входов диагностируемой .системы, N - число пар тестовых наборов. Объем блока 5 памяти эталонных признаков равен (N« х ), где N число выходов диагностируемой системы. ОбЬем блока 6 памяти активизируемых модухюй равен (N х |Х N(), где Nj - число модулей в диагностируемой системе.

Если на активизируемом пути в некотором модуле имеется константная неисправность О шга 1, то ожидаемого переключения на соответствующем выходе диагностируемой системы 3 не произойдет, т.е. путь не будет активизирован. Это указьгаает на наличие неисправности в одном из модулей, находящихся на активизируемсж пути.

3

Устройство работает следующим образом.

По сигналу блока 9 синхронизации из блока 1 памяти тестов в диагностируемую систему 3 вьщается пара тестовых наборов. Затем по другому сигналу блока 9 синхронизации на выходах блока 4 формирования адреса эталонных признаков формируется адрес эталонной реакции на данную пару тестовьк наборов. Из блока 5 памяти эталонных признаков по этому адресу извлекается эталонный двоичный вектор наличия переключений на выходах диагностируемой системы 3, который поступает на входы блока 2 выделения признака неисправности. На другую группу входов этого блока с выходов диагностируемой системы 3 поступают реальные выходные сигналы.В блоке выделения признака неисправности (фиг. 2) элемент 11 задержки обеспечивает задержку, равную временному интервалу между двумя тестовыми наборами каждой пары .Поскольку вход каждого такого элемента подключен к одному из выходов диагностируемой системы, реакции этого выхода на пару тестовых наборов одновременно поступят на входы элемента 12 сложения по модулю 2, на инверсном выходе которого образуется логическая 1 при отсутствии переключения на выходе диагностируемой системы на данной паре тестовых наборов и логический О - при наличии такого переключения. Если в исправной диагностируемой системе на данном ее выходе при подаче пары тестовых наборов имеется переключение, то на вход элемента И 13 из блока 5 памяти эталонных признаков поступит логическая 1, что даст на выходе узла 10 выделения признака неисправности логическую 1, свидетельствующую о наличии неисправности на пути активизируемом данной парой тестовых наборов.. Этот признак неисправности проходя через элемент ИЛИ 14, обеспечивающий мультиплексирование таких признаков по всем выходам диагностируемой системы, поступает на вход элемента И 15, Назначение этого элемента - обеспечить.вьодачу признаков неисправности (непереключения выхода) в связи с каждой парой тестовых наборов, но не в связи с последовательными тестовьми наборами соседних

61 . 4

пар. Для этого на второй вход элемента И 15 поступает сигнал (логичео г кая 1) с блока 9 синхронизации, сви-. детельствующий об окончании обработки реакции диагностируемой системы на данную пару тестовых наборов.

Если сигнал с выхода блока вьоделения признака неисправности (фиг. 1) содержит признак неисправности (логическая 1), то по адресу,- сформиро-i ванному в блоке А формирования адреса эталонных признаков, в блоке б памяти активизируемых модулей выбирается двоичное слово, разрядность

которого равна числу модулей в диаг- ностируемой системе 3.Наличие.единицы в разряде этого слова свидетельствует о том, что соответствующий модуль находится на пути, активизируемом данной парой тестовых наборов, Таким образом, на выходы блока памяти активизируемых модулей 6 поступает слово, единичные разряды которого указывают на модули, лежащие на

пути, активизация которого не произошла, т.е. подозреваемые в наличии неисправности.

Блок 7 счетчиков приближений представляет собой поразрядньй сумматор, для каждого из модулей диагностируемой системы 3 указывающий на число неактивизированных путей, проходящих через данный модуль. Возможная структура блока 7 показана на фиг. 5.

5 Образующаяся на выходе блока 7 совокупность десятичных значений представляет собой некоторую функцию состояния диагностируемой системы, которая выдается на блок 8 индикации

0 после окончания проверки диагностируемой системы 3 по сигналу с блока 4 адреса эталонных признаков. .

Наблюдая значение функции состоя ния на блоке 8 индикации, оператор может установить неисправности какого модуля (модулей) эта функция соответствует.

Таким образом, переход к укрупнен-. ной модели неисправности (aктивJИзй- зируемый путь вместо отдельной .неисправности) позволяет диагностировать неисправности произвольной кратности, 5 а укрупнение разбиения диагностируемых систем на модули позволяет сократить объем запоминаемой информации и аппаратурные затраты.

. s

Формула изобретения

1. Устройство для обработки диагностических сигналов, содержащее блок синхронизации, блок формирования адреса эталонных признаков, блок памяти эталонных признаков, блок памяти тестов, .блок счетчиков приближений, блок индикации, пртгчем вход запуска блока синхронизации является входом запуска устройства, первый выход блока синхронизации соединен с входом синхронизации блока формирования адреса эталонных признаков ,группа информационных выходов которого соединена с адресными входами блока памяти эталонных признаков, второй выход блока синхронизации соединен с входом синхронизации блока памяти тестов, информационные выход которого соединены с информационными входами диагностируемой системы, информационные выходы блока счетчиков приближений соединены с группой информационных входов блока индикации, выход конца контроля блока формирования адреса эталонных признаков соединен с управляющим входом блока индикации, отличающееся тем, что, с целью уменьшения объема используемой памяти и расширения функциональных возможностей за счет одновременной обработки нескольких выходных сигналов диагностируемой

системы, устройство содержит блок

„ памяти активизируемых модулей и блок

вьщеления признака неисправности, причем третий вьпсод блока синхронизации соединен с разрешающим входом блока выделения признака неисправности, первая и вторая группы информационных входов блока вьщеления признака неисправности соединены с информационными выходами соответственно диагностируемой систем1я и блока памяти эталонных признаков, вы127076Г

ход блока вьщеления признака неисправности соединен с информационным входом блока памяти активизируемых модулей, адресные входы которого соединены с группой информационных выходов блока формирования адреса эталонных признаков, информационные выходы блока памяти активизируемых модулей соединены с информационными входами блока счетчиков приближений.

2. Устройство по п. 1, отличающееся тем, что блок выделения признака неисправности содержит п узлов вьщеления признака неисправности, где п - число выходов диагностируемой системы, элемент ИЛИ и элемент И, каждый- i-й уяел вьщеле- ния признака неисправности () содержит элемент задержки, элемент сложения по модулю два с инверсией и элемент И, причем вход i-ro элемента задержки подключен к i-му входу первой группы информационных входов блока .вьщеления признака неисправности, выход i-ro элемента задержки соединен с первым входом i-го элемента сложения по модулю два, инверсный выход которого соединен с первым входом i-ro элемента И, второй вход которого подключен к i-му входу второй группы информационных входов блока вьщеления признака неисправности, i-й вход первой группы информационных входов блока выделения признака неисправности подключен к второму входу i-ro элемента сложения по модулю два, вьрсоды с первого по п-й элементов И соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого подключен к входу разрешения блока выделения признака неисправности, выход элемента И является выходом блока вьщеления признака неисправности,Lr

11

Пуск

16

5блон2

18

5$лон1

19

В 6/1 он Ч

Фиг. 15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля логических схем | 1985 |

|

SU1252786A1 |

| Устройство для контроля синхронных цифровых узлов | 1984 |

|

SU1242964A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

Изобретение относится к цифро- 1ВЫМ системам автоматики и вычислительной техники и может быть использовано для диагностирования неисправностей отдельных модулей этих систем. Цель изобретения - уменьшение объема используемой памяти и расширение функциональных возможностей за счет одновременной обработки нескольких выходных сигналов диагностируемой системы. Устройство содержит блок хранения тестов, блок выделения признака неисправности блок формирования адреса эталонных признаков, блок памяти эталонных признаков, блок с памяти активизируемых модулей, блок счетчиков приближений, блок индика(Л ции, блок синхронизации. 1 з.п. ф-лы. 5 ил.

Фи2.5

| Устройство для диагностирования логических узлов | 1979 |

|

SU892447A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки диагностических сигналов | 1975 |

|

SU546895A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-15—Публикация

1985-05-29—Подача