со со

ел

О)

Изобретение относится к вычислительной технике и может быть использовано для построения цифровых интегрирующих машин, предназначенных для реп1ения дифференциальных уравнений.

Цель изобретения - упрощение устройства.

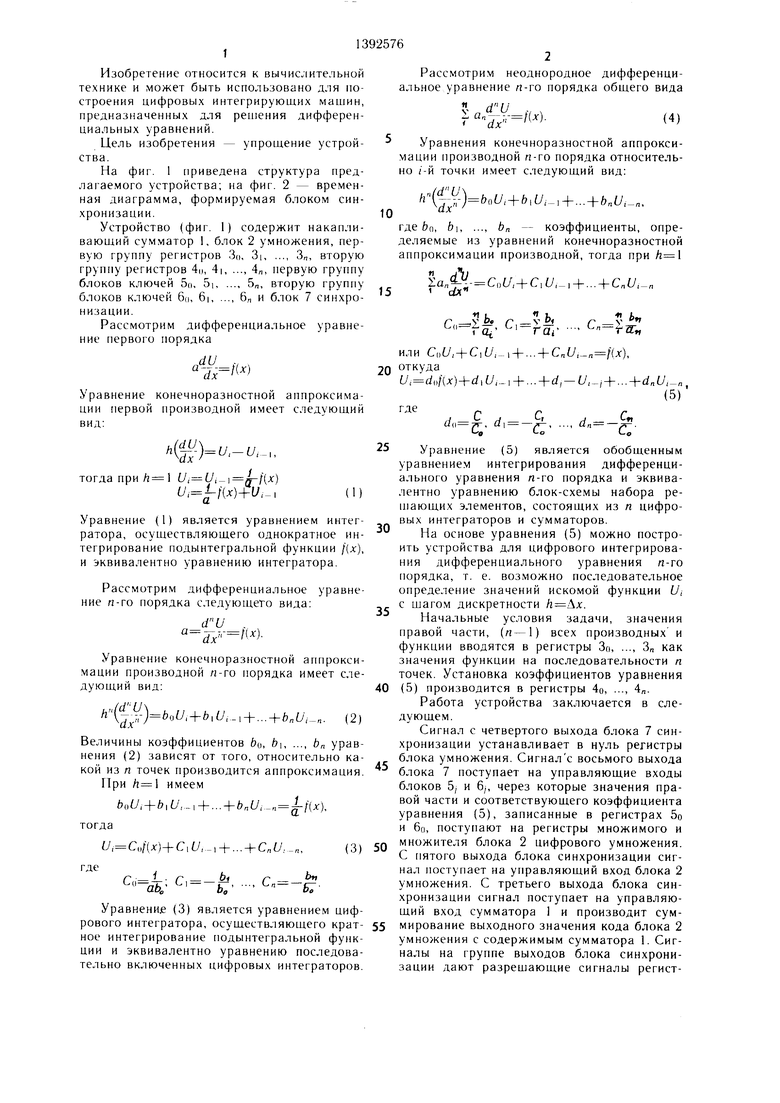

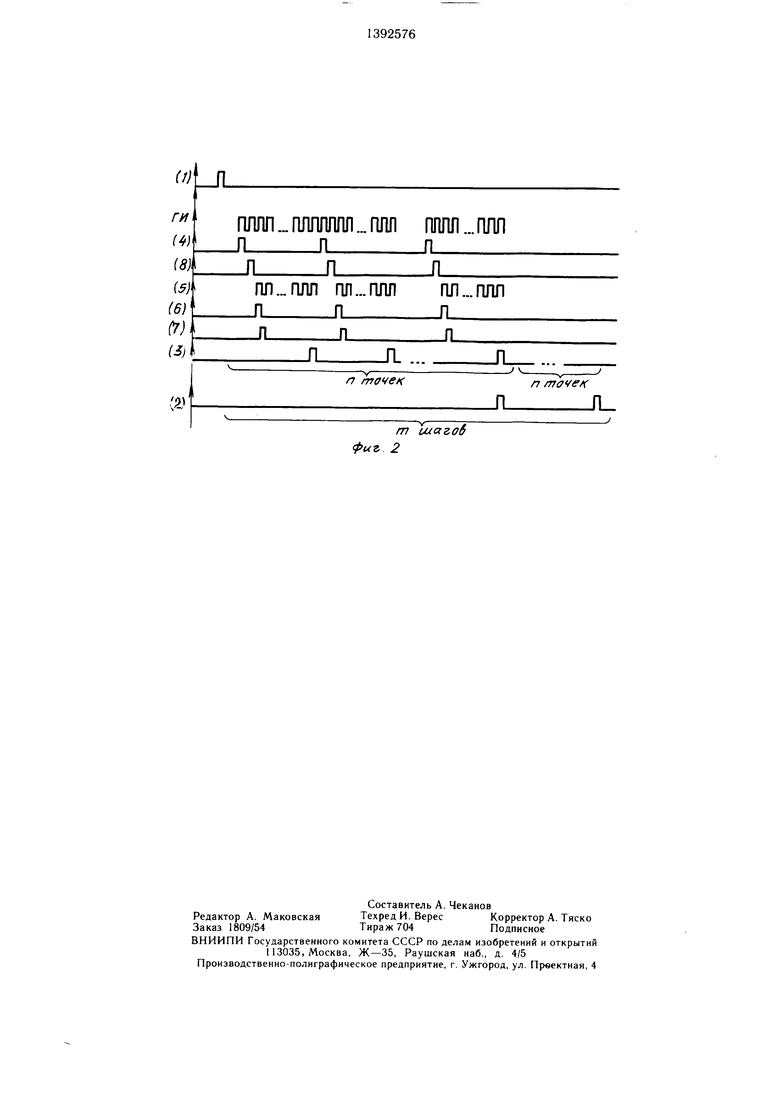

На фиг. 1 приведена структура предлагаемого устройства; на фиг. 2 - временная диаграмма, формируемая блоком синхронизации.

Устройство (фиг. 1) содержит накапливающий сумматор 1, блок 2 умножения, первую группу регистров Зо, 3| 3„, вторую

группу регистров 4и, 4|, ..., 4п, первую группу блоков ключей 5о, 5i, .... 5л, вторую группу блоков ключей бо, 6i, ..., 6„ и блок 7 синхронизации.

Рассмотрим дифференциальное уравнение первого порядка

.

Уравнение конечноразностной аппроксимации первой производной имеет следующий вид:

4f),-c ,-,,

тогда при Ui-U,(x)

(x) + U,(1)

Уравнение (1) является уравнением интегратора, осуществляющего однократное интегрирование подынтегральной функции f(x), и эквивалентно уравнению интегратора.

Рассмотрим дифференциальное уравнение п-го порядка следующего вида:

.

« (Х).

Уравнение конечноразностной аппроксимации производной л-го порядка имеет следующий вид:

f()b,U, + b,U..., + ...+bnU,,n. (2)

Величины коэффициентов Ь(,, Ь, ..., Ьп уравнения (2) зависят от того, относительно какой из п точек производится аппроксимация. При имеем

boL/, + ft|6 ,,, + ... + /b.(y,-.f(x),

тогда

, + ... + С„6 ,,„,

biп

;-, ..., C,i - с-.

DObe

(3) 50

Уравнение (3) является уравнением цифрового интегратора, осуществляющего кратное интегрирование подынтегральной функции и эквивалентно уравнению последовательно включенных цифровых интеграторов.

Рассмотрим неоднородное дифференциальное уравнение п-го порядка общего вида

Н Ч/

г .).

(4)

10

Уравнения конечноразностной аппроксимации производной п-го порядка относительно /-Й точки имеет следующий вид:

h()b,U, + b,U,,,+... + bnU,.,

где Ьп, Ь, ..., Ьп - коэффициенты, определяемые из уравнений конечноразностной аппроксимации производной, тогда при

15

d.- ,

1а„5- - , + С,(;,, + ... + ,. dx

0

5

0

5

0

5

0

5

I L

р ,у о

С -

ч I - bi

Ь.

raw

г -у

- ,

гаг

или C,,t/, + C|ty,--, + ... + ,(x),

откуда

L/,d,,f(x) + di (;,.. i + ...+t/,-t/,--j + ...+d-.ty,n,

(5) где

,

-в

Уравнение

d, С,

с:dn с(5) является обобщенным уравнением интегрирования дифференциального уравнения п-го порядка и эквивалентно уравнению блок-схемы набора решающих элементов, состоящих из п цифровых интеграторов и сумматоров.

На основе уравнения (5) можно построить устройства для цифрового интегрирования дифференциального уравнения п-го порядка, т. е. возможно последовательное определение значений искомой функции L , с щагом дискретности .

Начальные условия задачи, значения правой части, (п-1) всех производных и функции вводятся в регистры Зо, ..., 3„ как значения функции на последовательности п точек. Установка коэффициентов уравнения (5) производится в регистры 4о, ..., 4.

Работа устройства заключается в следующем.

Сигнал с четвертого выхода блока 7 синхронизации устанавливает в нуль регистры блока умножения. Сигнал с восьмого выхода блока 7 поступает на управляющие входы блоков 5, и 6/, через которые значения правой части и соответствующего коэффициента уравнения (5), записанные в регистрах 5о и 6о, поступают на регистры множимого и множителя блока 2 цифрового умножения. С пятого выхода блока синхронизации сигнал поступает на управляющий вход блока 2 умножения. С третьего выхода блока синхронизации сигнал поступает на управляющий вход сумматора 1 и производит суммирование выходного значения кода блока 2 умножения с содержимым сумматора 1. Сигналы на группе выходов блока синхронизации дают разрещающие сигналы регистрам 3, н 4,. Сигнал с шестого выхода блока синхронизации поступает на вход установки нуля регистров 3, устанавливает их в нуль, а сигнал с седьмого выхода блока синхронизации постунает на вход синхронизации регистра 3, и производит запись содержимого регистра 3/+| в регистр 3,. Это необходимо для подготовки схемы для следующего цикла работы, для вычисления значения функции на 1 -и точке.

Циклы умножения коэффициентов уравнения (5) dj, содержащихся в регистре 4,, на значения функции на г -й точке U,, находящиеся в регистре 3/, на блоке 2 умножения и получения суммы (частных) произведений на сумматоре 1 по формуле (5) повторяются и-|-1 раз. Так как в процессе работы проводилась перезапись содержимого /-ГО регистра первого ряда 3, в 3,i, в конце цикла произведена запись содержимого сумматора 1 в регистр Зп, то можно начать цик.1 вычисления значения функции на (-|-1-й точке. Этот цикл работы устройства повторяется для каждых последующих точек интервала интегрирования.

Предлагае.мое устройство осуществляет интегрирование дифференциального уравнения п-го порядка по произвольной независимой неременной на основе конечнораз- ностной аппроксимации производных, что исключает операцию непосредственного интегрирования вычислением площади подынтегральной функции. Отказ от блок-схемы набора рещающих элементов с исключением цифрового интегратора упрощает схему устройства.

Формула изобретения

Устройство для решения дифференциальных уравнений, содержащее накапливающий сумматор и блок синхронизации, причем первый и второй выходы блока синхронизации соединены соответствено с первым и вторым входами сброса накапливающего сумматора, третий выход блока синхронизации соединен с тактовым входом накапливающего сумматора, выходы которого соеди

5

нены с выходами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит блок умножения, две группы регистров по (п+1) регистров в каждой группе, где п - порядок дифферециального управления, и две группы блоков ключей по (п+1) блоку в каждой группе, причем выходы накапливающего сумматора соединены с информационными входами (n+U-i o регистра первой группы, установочные входы первого регистра первой группы соединены с входами подынтегральной функции устройства, входы начальных ус.повий /-и группы устройства соединены с установочными входами ((-|-1)-го (, п) регистра первой группы, выходы Л -го (, п + 1) регистра первой группы соединены с информационными входами (К-1)-го регистра первой группы, выходы K-vo регистра первой группы соединены с информационными входами К-го блока ключей первой группы,

0 выходы блоков ключей первой группы соединены через общую тину с входами первого сомножителя блока умножения, выходы которого соединены с информационными входами накапливающего сумматора, входы коэффициентов уравнения а-й (, п+1) группы устройства соединены с установочными входами а-го регистра второй группы, выходы которого соединены с информационными входами а-го блока ключей второй группы, выходы блоков ключей второй груп0 iibi соединены через общую щину с входами второго сомножителя блока умножения, четвертый и пятый выходы блока синхронизации соединены с входами сброса и синхронизации блока умножения соответственно, щестой выход блока синхронизации соединен с входами сброса регистров первой группы, седьмой выход блока синхронизации соединен с входами синхронизации регистров первой группы, восьмой выход блока синхронизации соединен с первыми управляющими входами блоков ключей первой и второй групп, а-й выход группы блока синхронизации соединен с входом выбора а-го регистра первой группы и вторыми управляющими входами а-х блоков ключей первой и второй групп.

5

5

0

фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования дифференциальных уравнений | 1985 |

|

SU1273962A1 |

| Аналого-цифровое устройство для решения системы дифференциальных уравнений | 1987 |

|

SU1462378A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

| Аналого-цифровое вычислительное устройство | 1988 |

|

SU1501103A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения цифровых интегрирующих машин, предназначенных для решения дифференциальных уравнений. Цель изобретения - упрощение устройства. Устройство содержит накапливающий сумматор I, блок 2 умножения, группы регистров 3 и 4, группы блоков ключей 5, 6 и блок синхронизации. Упрощение устройства достигнуто за счет конечиоразностной аппроксимации производных. 2 ил.

| Каляев А | |||

| В | |||

| Теория цифровых интегрирующих машин и структур | |||

| М.: Советское радио, 1970,,с | |||

| Счетная бухгалтерская линейка | 1922 |

|

SU386A1 |

| Каляев А | |||

| В | |||

| Однородные коммутационные регистровые структуры | |||

| М.: Сов | |||

| радио, 1978, фиг | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-04-30—Публикация

1986-11-11—Подача