(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

| Многоканальный счетчик импульсов | 1983 |

|

SU1170610A1 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

| Делитель частоты следования импульсов | 1981 |

|

SU1003350A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Счетное устройство | 1987 |

|

SU1492473A1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 2014 |

|

RU2538342C1 |

| Устройство для зарядки емкостного накопителя | 1989 |

|

SU1780150A1 |

Изобретение может быть использовано в устройствах автоматики и вычислительной техники и является дополнительным к авт.св. № 1003350. Цель изобретения - повьппение надежности работы устройства. С этой целью в него введены триггер 4, элемент ИЛИ 6и шина 13 сброса. Кроме того, устройство содержит оперативное запоминающее устройство 1, триггеры 2 и 3, сумматор 5 по модулю два, элементы И 7и 8, элемент 9 ЗАПРЕТ, счетчик 10 импульсов, входную шину 11, выходную шину 12. Устройство обеспечивает данное значение коэффициента деления, начиная с момента окончания импульса сброса на шине 13. 2 ил.

ю

СП

05

N

и.г.1

«12

Изобретение относится к импульсной технике, и может быть использовано в устройствах автоматики и вычислительной техники и является усовершенствованием устройства по авт.св, № 1003350-.

Цель изобретения - повышение надежности.

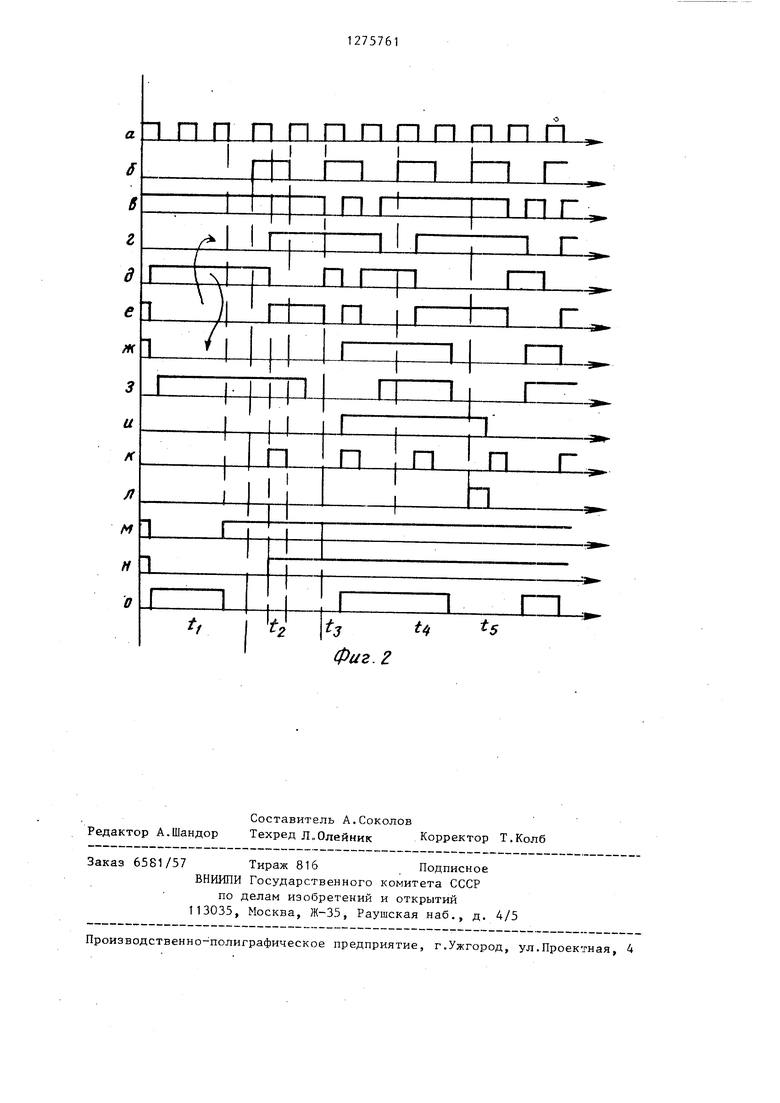

На фиг.1 приведена электрическая функциональная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу,

Делитель частоты следования импульсов содержит запоминающее устрой ство 1, три триггера 2-4, сумматор 5 по модулю два,элемент Ш1И6, два элемента И 7 и 8, элемент ЗАПРЕТ 9, счетчик 10 импульсов, счетный вход которого соединен с входной шкной 11 и с управляющим входом оперативного запоминающего устройства 1, разрядные выходы - с соответствующими входами первого элемента И 7 и с соответствующими адресными входами оперативного запоминающего устройства 1, выход которого соединен с первым входом ,. сумматора 5 по модулю два, сигнальный выход которого соединен с первым входом первого триггера 2, выход переноса - с первым входом второго элемента И 8 и с информационным входом второго триггера 3,. выход которого соединен с вторым входом сумматора 5 по модулю два, счетный вход- с вторым. входом первого триггера 2, с вход1 ой шиной 11 S, с первым входом элемента рАПРЕТ 9 и с вторым входом второго элемента И 8, выход кторого соединен с выходной шиной t2p третий вход с выходом первого элемента И 7 и с вторым входом элемента ЗАПРЕТ 9, выход которого соединен с входом запуска второго и дополнительного триггеров 3 и 4, причем вход сброса дополнительного триггера 4 соединен с входом сброса второго триггера 3, с входом сброса счетчика 10 импульсов и с шиной 13 сброса, которая соединена с первым входом элемента ИЛИ 6, выход которого соединен с информационным входом оперативного запоминающего устройства 1 i, второй вход - с выходом первого триггера 2, третий вход которого соединен с выходом дополнительного триггера 4.

Рассморим работу устройства на примере делителя частоты с коэффициентом деления восемь,-у которого счет57611

чик 10 импульсов имеет только один двоичный разряд, а оперативное запоминающее устройство 1 состоит из двух ячеек. На шину 11 поступает им5 пульсный сигнале частотойf (фиг.2й) .С приходом каждого импульса счетчик 10 изменяет свое состояние (фиг.25). Импульс на выходе устройства 1 , (фиг,2||) соответствует состоянию оп0 рашиваемой ячейки памяти. Этот импульс суммируется в сумматоре 5 с импульсом, поступающим с выхода триггера 3 (фиг.2г), при этом на сигнальном выходе сумматора 5 формируется

15 импульс суммы (фиг.2а), а на выходе переноса сумматора 5 формируется импульс переноса (фиг.2е).

По окончании входного импульса

20 на шине 11 происходит запись суммы в триггер 2 (фиг.2) и импульса переноса в триггер 3 (фиг.2г), а импульс с выхода триггера 2 через элемент 6 (фиг.2с) переписывается в ту же оп25 рашиваемую ячейку устройства 1

(фиг.2,и). Во время записи информации в устройство 1 на его выходе присутствует сигнал логической единицы (фиг.2ь), счетчик 10 в процессе ра30 боты изменяет свое состояние от О до 2 - 1, где п - количество разрядов счетчика 10, при этом происходит последовательный опрос и изменение состояний всех ячеек устройства 1.

3 Элемент 7 из всех состояний счетчика вьщеляет одно, соответствующее значению 2 - 1. При этом сигнал на выходе элемента 7 а. 1. Элемент 9 формирует импульсный сигнал g fAd

40 (фиг.2к) во время паузы между импульсами сигнала f, соответствующими переходу счетчика 10 в состояние О, т.е. импульс g предшествует переходу счетчика 10 в состояние О. Триггер

д 3 сигналом g устанавливается в состояние 1 (фиг.2-г) и с приходом следующих 2 импульсов входного сигнала, за счет работы сумматора 5 и триггеров 2 и 3, код в матрице устройства 1 увеличивается на 1, Так на фиг. 24,0 моментам времени t - t соответствуют состояния ячеек памяти

,,t4

У1 О 1 О 1

У2 О

О

1 Таким образом, за период времени, соответствующий появлению 2 импульсов входного сигнала f, состояние устройства 1 изменяется на 1, а поскольку его емкость равна 2 бит, то число состояний устройства 1 равно 2 , а значит, переход из состояния N 1 в состояние N О будет происходить через 2 периодов переполнения счетчика 10, т.е. через 2 тактов входного сигнала частотой f. Переход устройства 1 из состояния 2 - 1 в состояние О сопровождается сигналом переноса (фиг.2е) совпадающим во времени с моментом перехода счетчика 10 в состояние О Этот импульс выделяется элементом 8 и поступает на шину 12 (фиг.2л). Сле довательно, устройство, содержащее п-разрядный счетчик импульсов, имеет коэффициент деления К 2 . Сигнал сброса (фиг.2м) на шине 13 устанавливает в начальное состояние счетчик 10 (фиг.25), триггер 3 (фиг.2г) и триггер 4 (фиг.2н), который удерживает в нулевом состоянии триггер 2 (фиг.2ж). После прохождения первых 2 им- , пульсов входного сигнала триггер 4 сигналом с выхода элемента 9 перебра сывается в единичное состояние (фиг.2н), и триггер 4 переключается в зависимости от информации на сигнальном выходе сумматора 5 (фиг.2ж,). Сигнал сброса также через элемент 6 записывает 1 в нулевую ячейку устройства 1 (фиг.2о). Это необходимо потому, что опрос ячеек устройства 1 происходит последовательно в течение цикла работы счетчика 10 и указанным способом ликвидируется отставание выходного импульса устройства на один цикл работы счетчика 10. Таким образом, устройство обеспечивает заданное значение коэффициента деления, начиная с момента окончания импульса сброса на шине 13. Формула изобретения Делитель частоты следования импульсов по авт.св. № 1003350, отличающийся тем, что, с целью повышения надежности работы, в него введены дополнительный триггер, элемент ИЛИ и шина сброса, которая соединена с входом сброса счетчика импульсов, с входами сброса второго и дополнительного триггеров, вход запуска последнего из которых подключен к входу запуска второго триггера, и с первым входом элемента ИЛИ, включенного между выходом первого триггера, вход запуска которого соединен с выходом дополнительного триггера и информационным входом оперативного запоминающего устройства.

| Делитель частоты следования импульсов | 1981 |

|

SU1003350A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-07—Публикация

1985-04-05—Подача