13...16 повторителей, блоки 17...20 магистральных элементов, повторители 21...24 синхросигналов и повторители 25...33 управляющих сигнапов. Кроме того, устройство содержит магистрали 34...37 данных, входы 38...41 синхросигналов и управляющие входы 42...50. Режим работы устройства устанавливается подачей сигналов на входы 42...50 и синхросигналов на входы 38...41. В режиме трансляции информации регистры информац)яи с одного из входов (34...37) поступают

I

Изобретение относится к вычисли- тельной технике и может быть использовано в вычислительных системах для обмена данными между запоминаю- пщми устройствами и операционными блоками.

Цель изобретения - повышение надежности устройства.

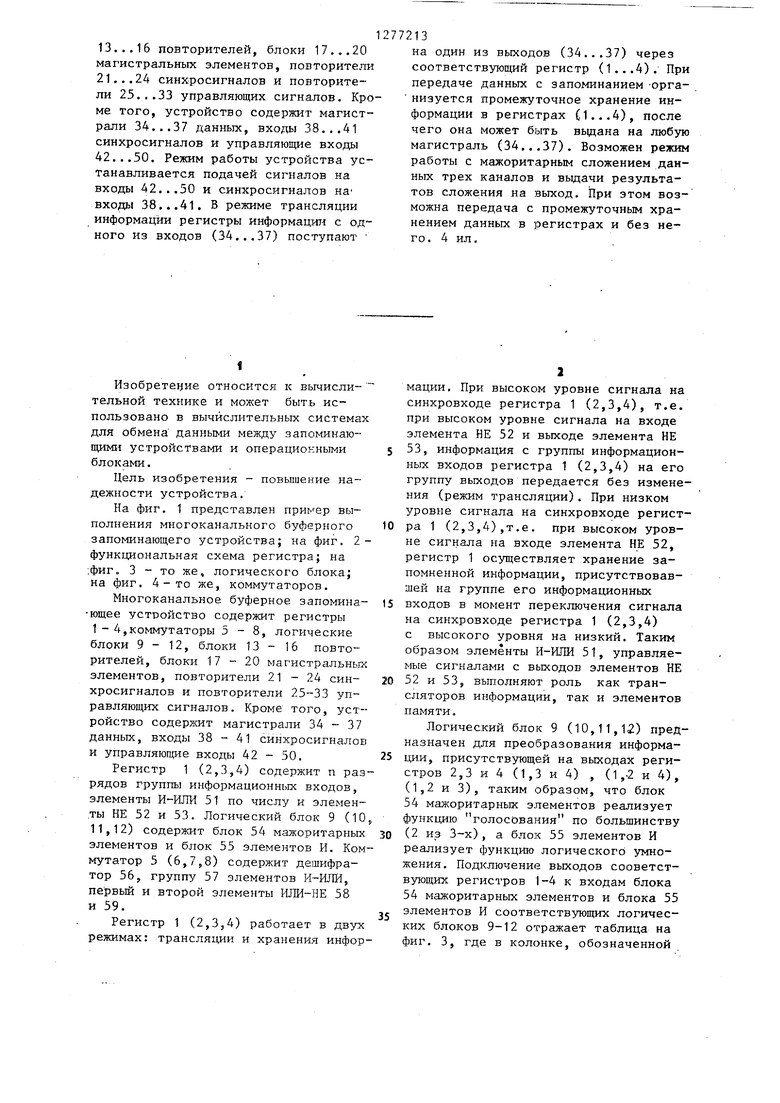

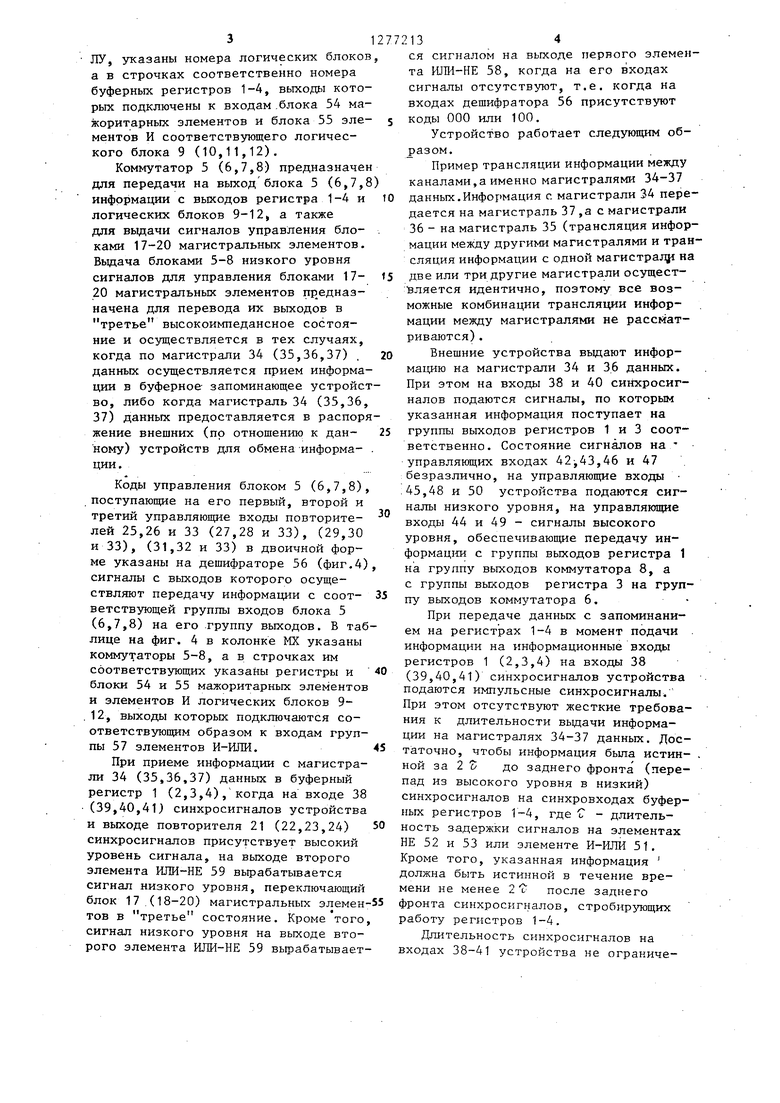

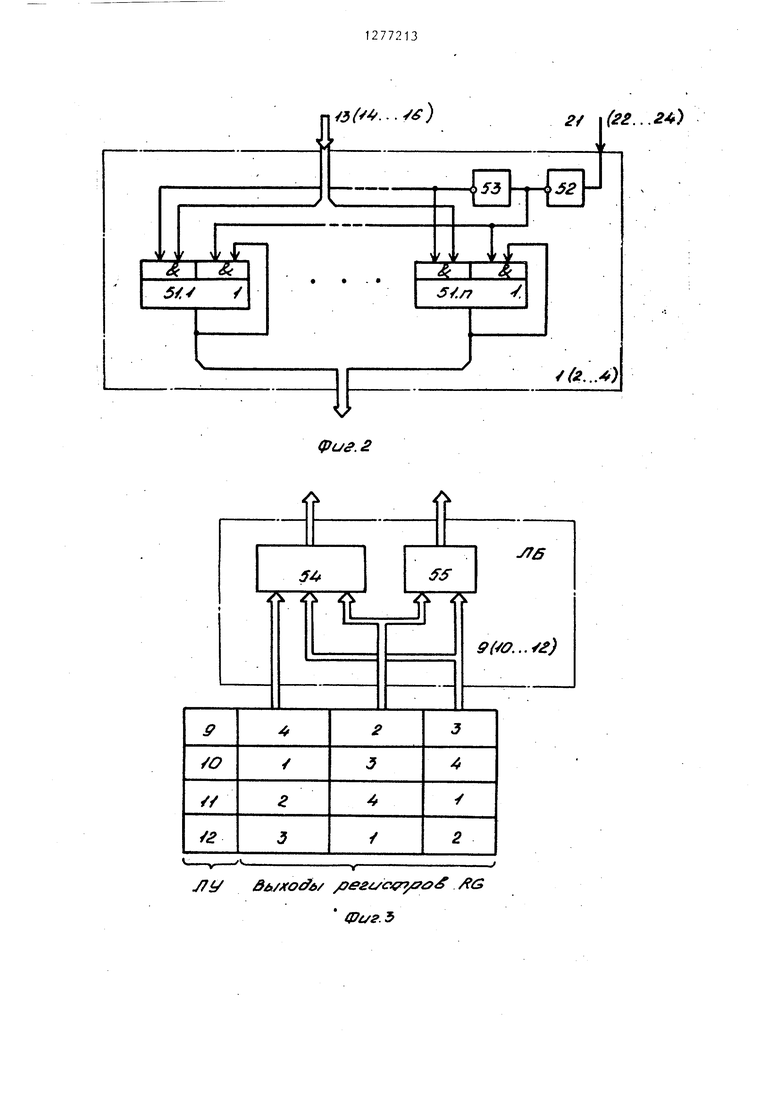

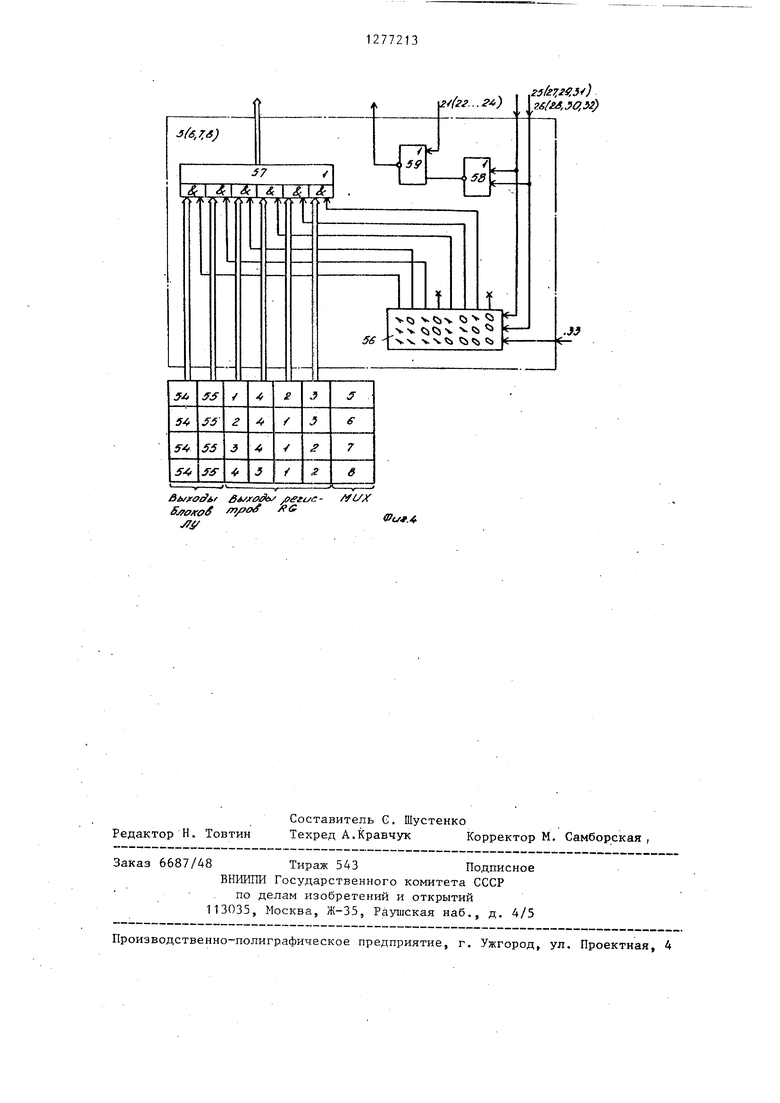

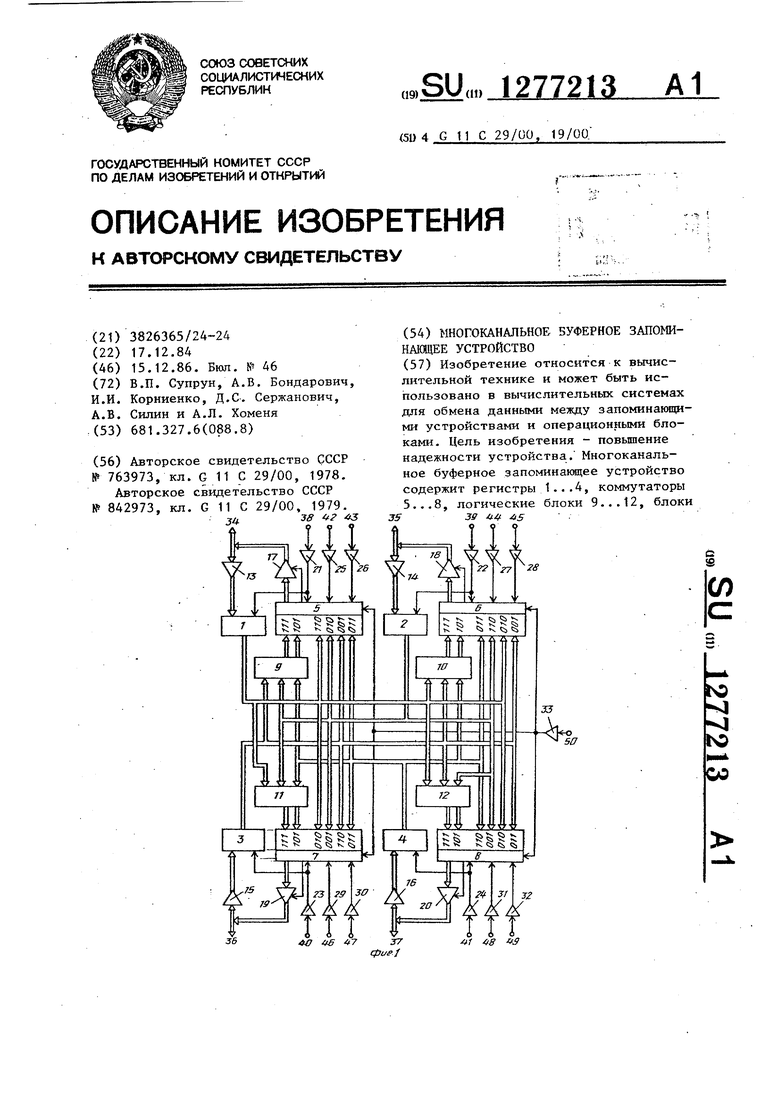

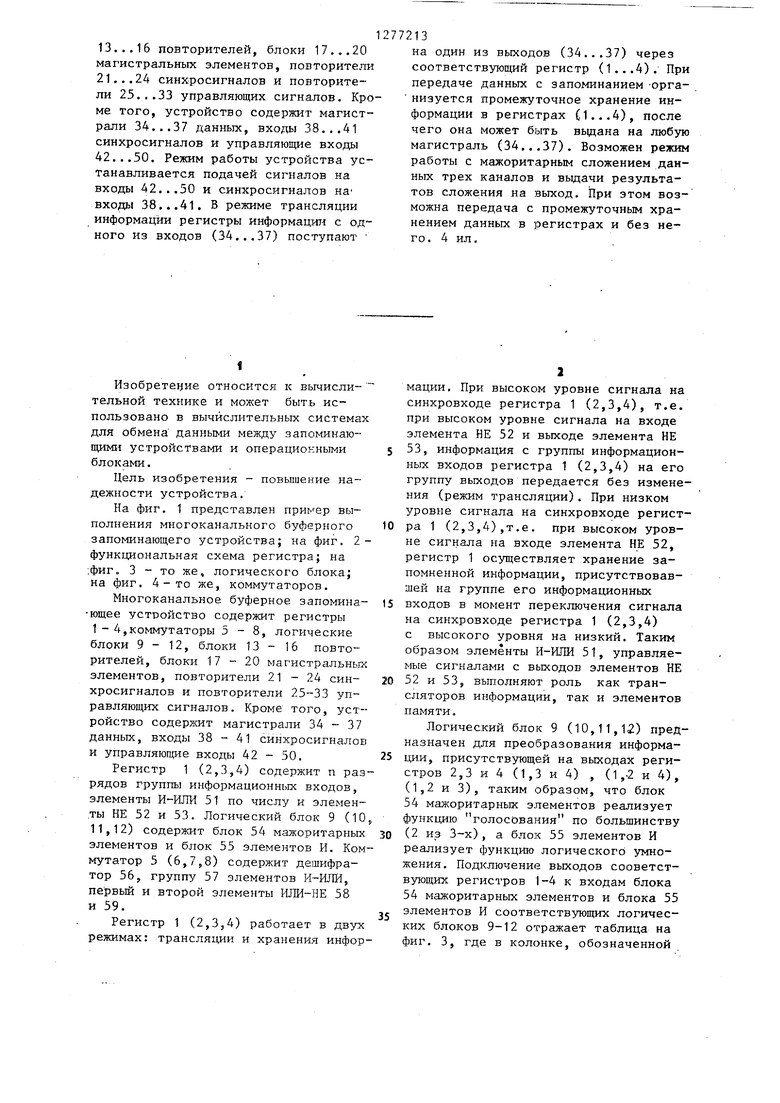

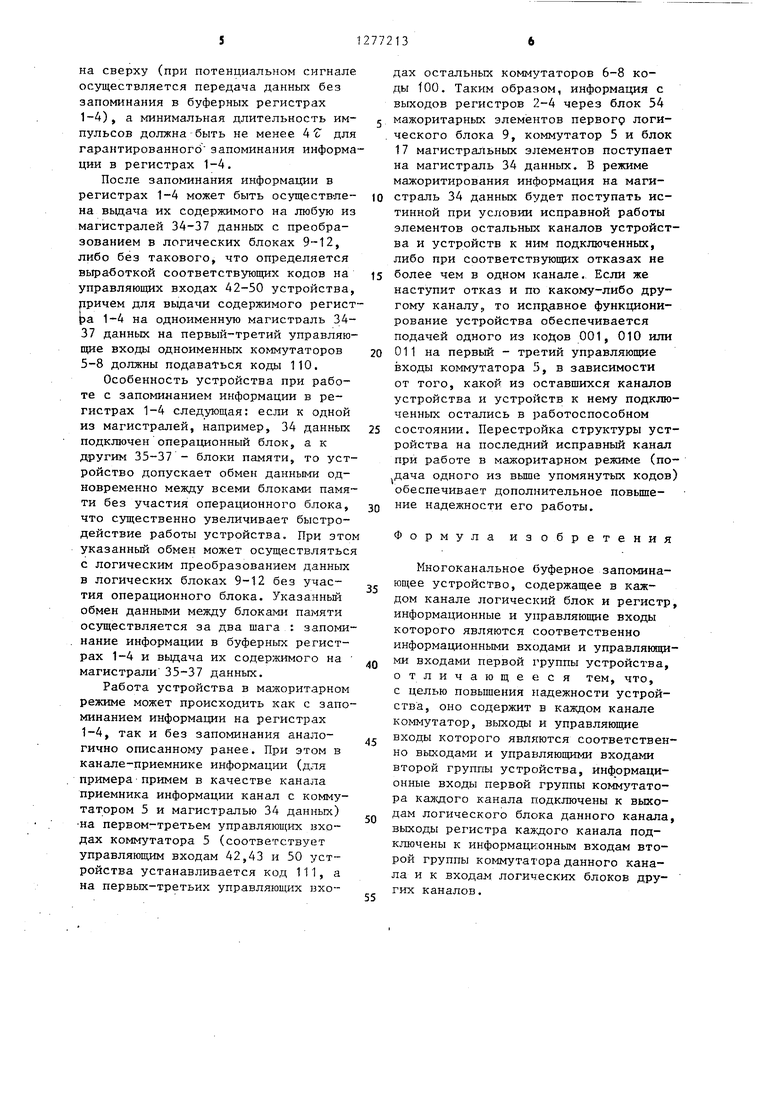

На фиг. 1 представлен пример выполнения многоканального буферного запоминающего устройства; на фиг, 2- функциональная схема регистра; на :фиг. 3 - то же, логического блока; на фиг. 4 - то же, коммутаторов.

Многоканальное буферное запомина- ющее УСТРОЙСТВО содержит регистры 1 - 4,коммутаторы 5-8, логические блоки 9 - 12, блоки 13 - 16 повторителей, блоки 17-20 магистральных элементов, повторители 21-24 син- хросигналов и повторители 25-33 управляющих сигналов. Кроме того, устройство содержит магистрали 34 - 37 данных, входы 38-41 синхросигналов и управляющие входы 42 - 50.

Регистр 1 (2,3,4) содержит п разрядов группы информационных входов, элементы И-ИЛИ 51 по числу и элементы НЕ 52 и 53. Логический блок 9 (10 11,12) содержит блок 54 мажоритарных элементов и блок 55 элементов И. Коммутатор 5 (6,7,8) содержит дешифратор 56, группу 57 элементов И-ИЛИ, первый и второй элементы ИЛИ-НЕ 58 и 59.

Регистр 1 (2,3,4) работает в дву:к режимах: трансляции и хранения инфор

77213

на один из вьгходов (34...37) через соответствующий регистр (1...4). При передаче данных с запоминанием -орга- низуется промежуточное хранение информации в регистрах (1...4), после чего она может быть вьщана на любую магистраль (34...37). Возможен режим работы с мажоритарным сложением данных трех каналов и вьщачи результатов сложения на выход. При этом возможна передача с промежуточньм хранением данных в регистрах и без него . 4 ил .

нации. При высоком уровне сигнала на синхровходе регистра 1 (2,3,4), т.е. при высоком уровне сигнала на входе элемента НЕ 52 и выходе элемента НЕ 53, информация с группы информационных входов регистра 1 (2,3,4) на его группу выходов передается без изменения (режим трансляции). При низком уровне сигнала на синхровходе регистра 1 (2,3,4),т.е. при высоком уровне сигнала на входе элемента НЕ 52, регистр 1 осуществляет хранение запомненной информации, присутствовавшей на группе его информационных входов в момент переключения сигнала на синхровходе регистра 1 (2,3,4) с высокого уровня на низкий. Таким образом элементы И-РШИ 51, управляемые сигналами с выходов элементов НЕ 52 и 53, выполняют роль как трансляторов информации, так и элементов памяти.

Логический блок 9 (10,11,12) предназначен для преобразования информации, присутствующей на выходах регистров 2,3 и 4 (1,3 и 4) , (1,-2 и 4), (1,2 и 3), таким образом, что блок 54 мажоритарных элементов реализует функцию голосования по большинству (2 из 3-х), а блок 55 элементов И реализует функцию логического умножения. Подключение выходов сооветст- вующих регистров 1-4 к входам блока 54 мажоритарных элементов и блока 55 элементов И соответствующих логических блоков 9-12 отражает таблица на фиг. 3, где в колонке, обозначенной

3

ЛУ, указаны номера логических блоков а в строчках соответственно номера буферных регистров 1-4, выходы которых подключены к входам .блока 54 мажоритарных элементов и блока 55 эле- ментов И соответствующего логического блока 9 (10,11,12),

Коммутатор 5 (6,7,8) предназначен для передачи на выход блока 5 (6,7,8 информации с выходов регистра 1-4 и логических блоков 9-12, а также для вьщачи сигналов управления бло- ками 17-20 магистральных элементов. Вьздача блоками 5-8 низкого уровня сигналов для управления блоками 17- 20 магистральных элементов пр едназ- начена для перевода их выходов в третье высокоимпедансное состояние и осуществляется в тех случаях, когда по магистрали 34 (35,36,37) . данных осуществляется прием информации в буферное запоминающее устройство, либо когда магистраль 34 (35,36, 37) данных предоставляется в распоряжение внешних (по отнощению к дан- ному) устройств для обмена информа- ции.

Коды управления блоком 5 (6,7,8), поступающие на его первый, второй и

третий управляющие входы повторите- лей 25,26 и 33 (27,28 и 33), (29,30 и 33), (31,32 и 33) в двоичной форме указаны на дешифраторе 56 (фиг,4) сигналы с выходов которого осуществляют передачу информации с соот- ветствующей группы входов блока 5 (6,7,8) на его группу выходов. В таблице на фиг. 4 в колонке MX указаны коммутаторы 5-8, а в строчках им соответствующих указаны регистры и блоки 54 и 55 мажоритарных элементов и элементов И логических блоков 9- .12, выходы которых подключаются соответствующим образом к входам группы 57 элементов И-ИЛИ.

При приеме информации с магистрали 34 (35,36,37) данных в буферный регистр 1 (2,3,4), когда на входе 38 (39,40,41) синхросигналов устройства и выходе повторителя 21 (22,23,24) синхросигналов присутствует высокий уровень сигнала, на выходе второго элемента ИЛИ-НЕ 59 вырабатывается сигнал низкого уровня, переключающий блок 17.(18-20) магистральных элементов в третье состояние. Кроме того, сигнал низкого уровня на выходе второго элемента ИЛИ-ИЕ 59 вырабатывает2134

ся сигналом на выходе первого элемента ИЛИ-НЕ 58, когда на его входах сигналы отсутствуют, т.е, когда на входах дешифратора 56 присутствуют коды 000 или 100,

Устройство работает следующим образом.

Пример трансляции информации между каналами,а именно магистралями 34-37 даивых.Информация с магистрали 34 передается на магистраль 37 ,а с магистрали 36 - на магистраль 35 (трансляция информации меясду другими магистралями и трасляция информации с одной магистрал} н две или три другие магистрали осуществляется идентично, поэтому все возможные комбинации трансляции информации между магистралями не рассматриваются) .

Внешние устройства выдают информацию на магистрали 34 и 36 данных. При этом на входы 38 и 40 синхросигналов подаются сигналы, по которым указанная информация поступает на группы выходов регистров 1 и 3 соответственно. Состояние сигналов на управляющих входах ,46 и 47 безразлично, на управляющие входы ,45,48 и 50 устройства подаются сигналы низкого уровня, на управляющие входы 44 и 49 - сигналы высокого уровня, обеспечивающие передачу ин- формащл с группы выходов регистра 1 на группу выходов коммутатора 8, а с группы выходов регистра 3 на группу выходов коммутатора 6. При передаче данных с запоминанием на регистрах 1-4 в момент подачи информации на информационные входы регистров 1 (2,3,4) на входы 38 (39,40,41) синхросигналов устройства подаются импульсные синхросигналы. При этом отсутствуют жесткие требования к длительности вьщачи информации на магистралях 34-37 данных. Достаточно, чтобы информация была истинной за 2 с; до заднего фронта (перепад из высокого уровня в низкий) синхросигналов на синхровходах буферных регистров 1-4, где С - длительность задержки сигналов на элементах НЕ 52 и 53 или элементе И-ИЛИ 51, Кроме того, указанная информация должна быть истинной в течение времени не менее 2 1) после заднего фронта синхросигналов, стробирующих работу регистров 1-4,

Длительность синхросигналов на входах 38-41 устройства не ограничена сверху (при потенциальном сигнале осуществляется передача данных без запоминания в буферных регистрах 1-4), а минимальная длительность им- пульсов должна быть не менее 4 € для гарантированного запоминания информации в регистрах 1-4.

После запоминания информации в регистрах 1-4 может быть осуществле- на вьщача их содержимого на любую из магистралей 34-37 данных с преобразованием в логических блоках 9-12, либо без такового, что определяется выработкой соответствующих кодов на управляющих входах 42-50 устройства, рричем для вьщачи содержимого регистра 1-4 на одноименную магистраль 34- 37 данных на первый-третий управляю- пще входы одноименных коммутаторов 5-8 должны подаваться коды 110.

Особенность устройства при работе с запоминанием информации в регистрах 1-4 следующая: если к одной из магистралей, например, 34 данных подключен операционный блок, а к другим 35-37 - блоки памяти, то устройство допускает обмен данныки одновременно между всеми блоками памяти без участия операционного блока, что существенно увеличивает быстродействие работы устройства. При этом указанный обмен может осуществляться с логическим преобразованием данных в логических блоках 9-12 без участия операционного блока. Указанньй обмен данными между блоками памяти осуществляется за два шага : запоми- . нание информации в буферных регистрах 1-4 и выдача их содержимого на магистрали 35-37 данных.

Работа устройства в мажоритарном режиме может происходить как с запоминанием информации на регистрах 1-4, так и без запоминания аналогично описанному ранее. При этом в канале-приемнике информации (для примерапримем в качестве канала приемника информации канал с коммутатором 5 и магистралью 34 данных) на первом-третьем управляющих входах коммутатора 5 (соответствует управляющим входам 42,43 и 50 устройства устанавливается код 111, а на первых-третьих управляющих вхо-

g

5 0

5 о

5

дах остальных коммутаторов 6-8 коды too. Таким образом, информация с выходов регистров 2-4 через блок 54 мажоритарных элементов первогр логического блока 9, коммутатор 5 и блок 17 магистральных элементов поступает на магистраль 34 данных. В режиме мажоритирования информация на магистраль 34 данных будет поступать истинной при условии исправной работы элементов остальных каналов устройства и устройств к ним подключенных, либо при соответствующих отказах не более чем в одном канале. Если же наступит отказ и по какому-либо другому каналу., то исп1 авное функционирование устройства обеспечивается подачей одного из кодов 001, 010 или 011 на первьй - третий управляющие входы коммутатора 5, в зависимости от того, какой из оставшихся каналов устройства и устройств к нему подключенных остались в работоспособном состоянии. Перестройка структуры устройства на последний исправный канал при работе в мажоритарном режиме (подача одного из вьше упомянутых кодов) обеспечивает дополнительное повьщ1е- ние надежности его работы.

Формула изобретения

Многоканальное буферное запоминающее устройство, содержащее в каждом канале логический блок и регистр, информационные и управляющие входы которого являются соответственно информационными входами и управляющими входами первой группы устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит в каждом канале коммутатор, выходы и управляющие входы которого являются соответственно выходами и управляющими входами второй группы устройства, информационные входы первой группы коммутатора калщого канала подключены к выходам логического блока данного канала, выходы регистра каясдого канала подключены к информационным входам второй группы коммутатора данного канала и к входам логических блоков дру- гих каналов.

фи.2

У ffA/xod A/ cpf/г.Ъ

jfej.f)

& ; & , & ft ft t И t ft t ff Т И t

D

f

Л5jf

S ff

fS

s

Bi /xotfitf ff /jrae e /fftifC- /fi/X / ff

Редактор H. Товтин

Составитель G. Шустенко

Техред А.Кравчук Корректор М. Самборская ,

Заказ 6687/48 Тираж 543Подписное

ВНИШТИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

г(гг...г4)

Z5fe7,2ff.}) .f,yO,K)

VC5 v«:,-v u w CiCj V 0 4v vv«i

t.39

Puf.4

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Система для контроля электрических параметров логических блоков | 1988 |

|

SU1725230A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для подключения абонентов к магистрали | 1991 |

|

SU1833880A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для обмена данными между запоминающими устройствами и операционными блоками. Цель изобретения - повышение надежности устройства. Многоканальное буферное запоминакнцее устройство содержит регистры 1.. .4, коммутаторы 5...8, логические блоки 9... 12, блоки 3ff «« 5 (Л 1 8 f3

| Буферное запоминающее устройство с автономным контролем | 1978 |

|

SU763973A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU842973A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-15—Публикация

1984-12-17—Подача