10

f5

20

25

Изобретение относится к вычислительной технике и может быть приме- нено для разработки схем памяти.

Цель изобретения - повышение быстродействия устройства.

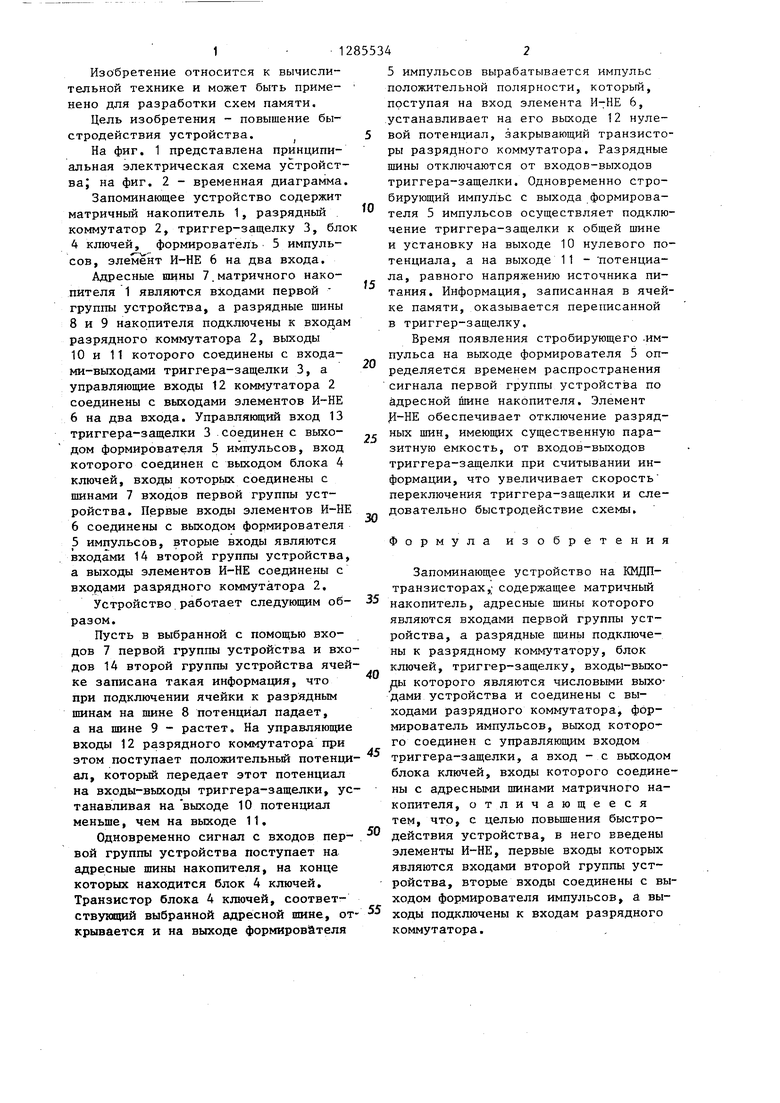

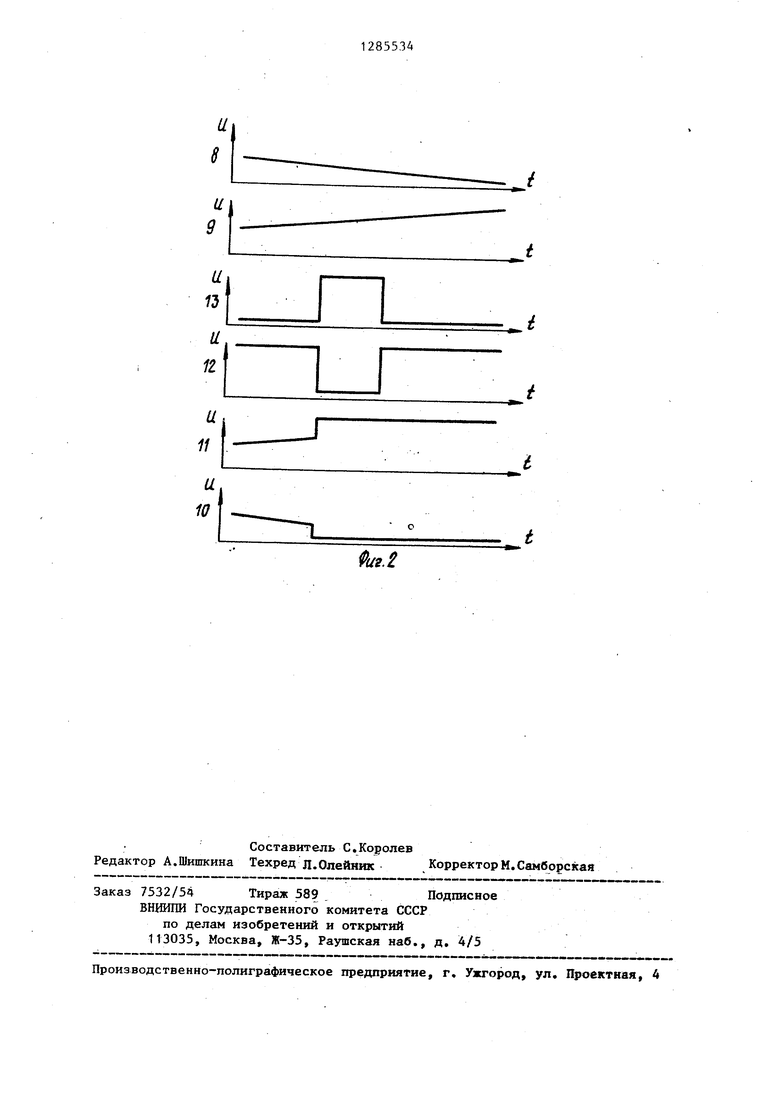

На фиг. 1 представлена принципиальная электрическая схема устройства; на фиг, 2 - временная диаграмма.

Запоминающее устройство содержит матричный накопитель 1, разрядный коммутатор 2, триггер-защелку 3, блок

4ключей, формирователь 5 импульсов, элемент И-НЕ 6 на два входа.

Адресные шины 7.матричного накопителя 1 являются входами первой группы устройства, а разрядные шины 8 и 9 накопителя подключены к разрядного коммутатора 2, выходы 10 и 11 которого соединены с входами-выходами триггера-защелки 3, а управляющие входы 12 коммутатора 2 соединены с выходами элементов И-НЕ 6 на два входа. Управляющий вход 13 триггера-защелки 3 соединен с выходом формирователя 5 импульсов, вход которого соединен с выходом блока 4 ключей, входы которых соединены с пшнами 7 входов первой группы устройства. Первые входы элементов И-НЕ 6 соединены с выходом формирователя

5импульсов, вторые входы являются входами 14 второй группы устройства, а выходы элементов И-НЕ соединены с входами разрядного коммутатора 2.

Устройство работает следующим образом.

Пусть в выбранной с помощью входов 7 первой группы устройства и входов 14 второй группы устройства ячейке записана такая информация, что при подключении ячейки к разрядным шинам на пшне 8 потенциал падает, а на щине 9 - растет. На управляющие входы 12 разрядного коммутатора при этом поступает положительньм потенциал, который передает этот потенциал на входы-выходы триггера-защелки, устанавливая на выходе 10 потенциал меньше, чем на выходе 11,

Одновременно сигнал с входов первой группы устройства поступает на адресные шины накопителя, на конце которых находится блок 4 ключей. Транзистор блока 4 ключей, соответствующий выбранной адресной шине, от- крывается и на выходе формирователя

12855342

5 импульсов вырабатывается импульс положительной полярности, который,

30

35

40

45

50

поступая на вход элемента И-НЕ 6, устанавливает на его выходе 12 нуле вой потенциал, закрывающий транзист ры разрядного коммутатора. Разрядны шины отключаются от входов-выходов триггера-защелки. Одновременно стро бирующий импульс с выхода формирова теля 5 импульсов осуществляет подкл чение триггера-защелки к общей шине и установку на выходе 10 нулевого п тенциала, а на выходе 11 - потенциа ла, равного напряжению источника пи тания. Информация, записанная в яче ке памяти, оказывается переписанной в триггер-защелку.

Время появления стробирующего .им пульса на выходе формирователя 5 оп ределяется временем распространения сигнала первой группы устройства по адресной шине накопителя. Элемент обеспечивает отключение разряд ных шин, имеющих существенную паразитную емкость, от входов-выходов триггера-защелки при считывании информации, что увеличивает скорость переключения триггера-защелки и сле довательно быстродействие схемы.

Формула изобретени

Запоминающее устройство на КМДП- транзисторах,; содержащее матричный накопитель, адресные шины которого являются входами первой группы устройства, а разрядные шины подключены к разрядному коммутатору, блок ключей, триггер-защелку, входы-выхо ды которого являются числовыми выхо дами устройства и соединены с выходами разрядного коммутатора, формирователь импульсов, выход которого соединен с управляющим входом триггера-защелки, а вход - с выходо блока ключей, входы которого соедин ны с адресными шинами матричного на копителя, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него введены элементы И-НЕ, первые входы которых являются входами второй группы устройства, вторые входы соединены с в ходом формирователя импульсов, а вы ходы подключены к входам разрядного коммутатора.

5

0

5

0

5

0

5

0

поступая на вход элемента И-НЕ 6, устанавливает на его выходе 12 нулевой потенциал, закрывающий транзисторы разрядного коммутатора. Разрядные шины отключаются от входов-выходов триггера-защелки. Одновременно стро- бирующий импульс с выхода формирователя 5 импульсов осуществляет подключение триггера-защелки к общей шине и установку на выходе 10 нулевого потенциала, а на выходе 11 - потенциала, равного напряжению источника питания. Информация, записанная в ячейке памяти, оказывается переписанной в триггер-защелку.

Время появления стробирующего .импульса на выходе формирователя 5 определяется временем распространения сигнала первой группы устройства по адресной шине накопителя. Элемент обеспечивает отключение разрядных шин, имеющих существенную паразитную емкость, от входов-выходов триггера-защелки при считывании информации, что увеличивает скорость переключения триггера-защелки и следовательно быстродействие схемы.

Формула изобретения

Запоминающее устройство на КМДП- транзисторах,; содержащее матричный накопитель, адресные шины которого являются входами первой группы устройства, а разрядные шины подключены к разрядному коммутатору, блок ключей, триггер-защелку, входы-выходы которого являются числовыми выходами устройства и соединены с выходами разрядного коммутатора, формирователь импульсов, выход которого соединен с управляющим входом триггера-защелки, а вход - с выходом блока ключей, входы которого соединены с адресными шинами матричного накопителя, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него введены элементы И-НЕ, первые входы которых являются входами второй группы устройства, вторые входы соединены с выходом формирователя импульсов, а выходы подключены к входам разрядного коммутатора.

LL, f3

и

/2

и

11

и

10

Составитель С.Королев Редактор А.Шишкина Техред л.Олейник КорректорМ.Самборская

Заказ 7532/54 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113033, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1809466A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1300565A1 |

Изобретение относится к вычислительной технике и может быть применено для разработки схем памяти. Целью изобретения является повьше- ние быстродействия. Поставленная цель достигается тем, что в устройство введены элементы И-НЕ 6 с соответствующими связями. В, режиме выборки элемент И-НЕ 6 выключает разрядные коммутаторы 2 после того, как на входах-выходах триггера 3 появится информация. Таким образом, триггер 3 оказывается отключенным от разрядных шин 8, 9 матричного накопителя 1 и не перезаряжает большие паразитные емкости этих шин, что приводит к повьшений быстродействия. 2 ил. (Л С tc сх СП ел оо 1

| IEEE Journal of Solid-State Circuits, 1977, № 5, p | |||

| Складная пожарная (штурмовая) лестница | 1923 |

|

SU499A1 |

| Там же, p | |||

| АППАРАТ ДЛЯ РАЗРЕЗАНИЯ ПЕРЕДВИГАЮЩЕЙСЯ НА ПОДВИЖНОМ СТОЛЕ ТОРФЯНОЙ ПОЛОСЫ ПРИ ПОМОЩИ НОЖЕЙ, УКРЕПЛЕННЫХ НА ПОВЕРХНОСТИ БАРАБАНА | 1922 |

|

SU602A1 |

| Запоминающее устройство | 1982 |

|

SU1109804A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1987-01-23—Публикация

1985-03-29—Подача