Изобретение относится к вычислительной технике, а именно к полупроводниковым заноминакянлм устройствам с самоконтролем.

Цель изобретения - повышение достоверности контроля и информационной емкости устройства.

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - структурная схема предпочтительного варианта выполнения блока модульной памяти; на фиг. 3 - фиг. 8 - соответственно наиболее предпочтительный вариант выполнения соединения информационных входов устройства с входами соответственно блоков свертки по модулю два первой группы и блоков кодирования по коду Бергера первой группы, схемы подключения выходов блоков кодирования по коду Бергера первой или второй группы к входам блоков свертки по модулю два соответственно третьей или четвертой и пятой или шестой групп, функциональные схемы блока обнаружения ошибок и блока определения типа ошибок.

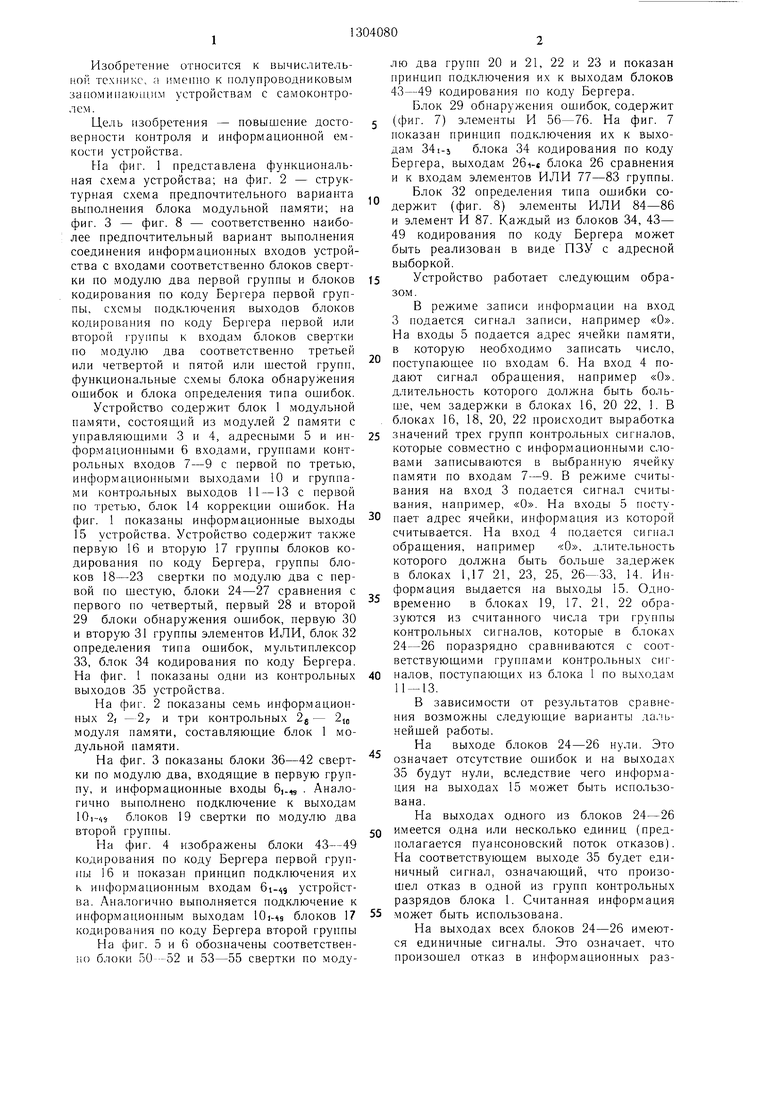

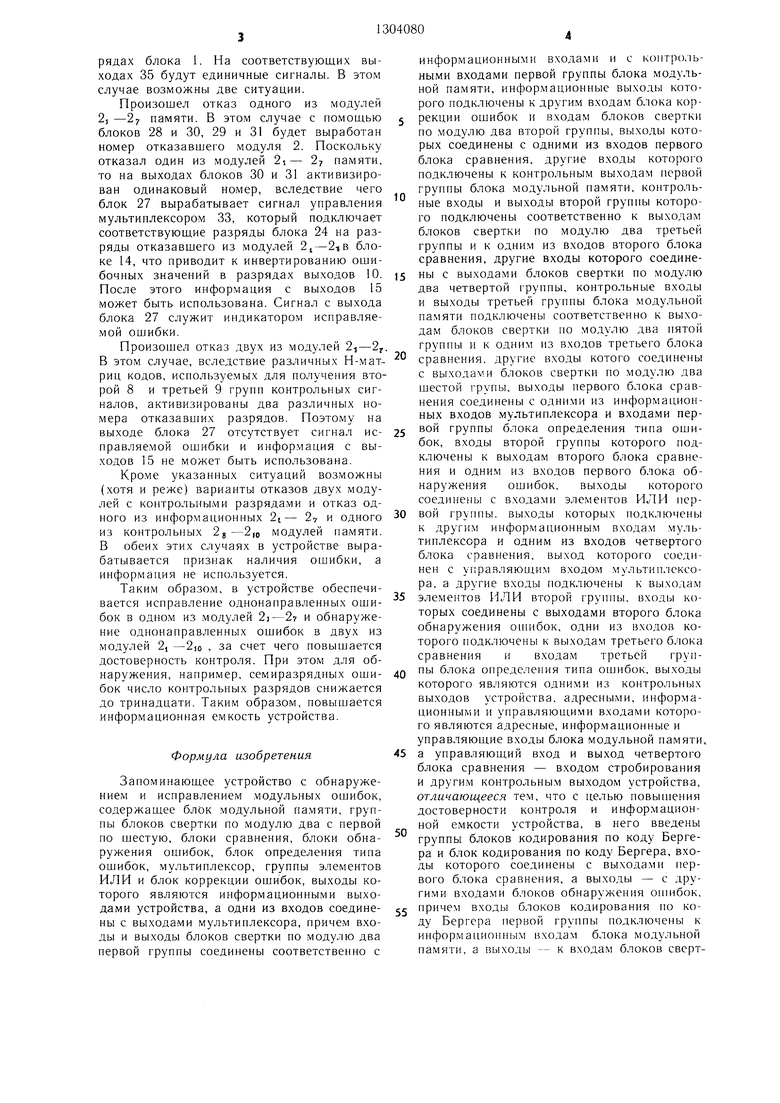

Устройство содержит блок 1 модульной памяти, состоящий из модулей 2 памяти с управляюн ими 3 и 4, адресными 5 и ин- формационпыми 6 входа.ми, группами контрольных входов 7-9 с первой по третью, информационными выходами 10 и группами контрольных выходов 11 -13 с первой по третью, блок 14 коррекции ошибок. На фиг. 1 показаны информационные выходы 15 устройства. Устройство содержит также первую 16 и вторую 17 группы блоков кодирования по коду Бергера, группы блоков 18-23 свертки по модулю два с первой по шестую, блоки 24-27 сравнения с первого по четвертый, первый 28 и второй 29 блоки обнаружения ошибок, первую 30 и вторую 31 группы элементов ИЛИ, блок 32 определения типа ошибок, мультиплексор 33, блок 34 кодирования по коду Бергера. На фиг. 1 показаны одни из контрольных выходов 35 устройства.

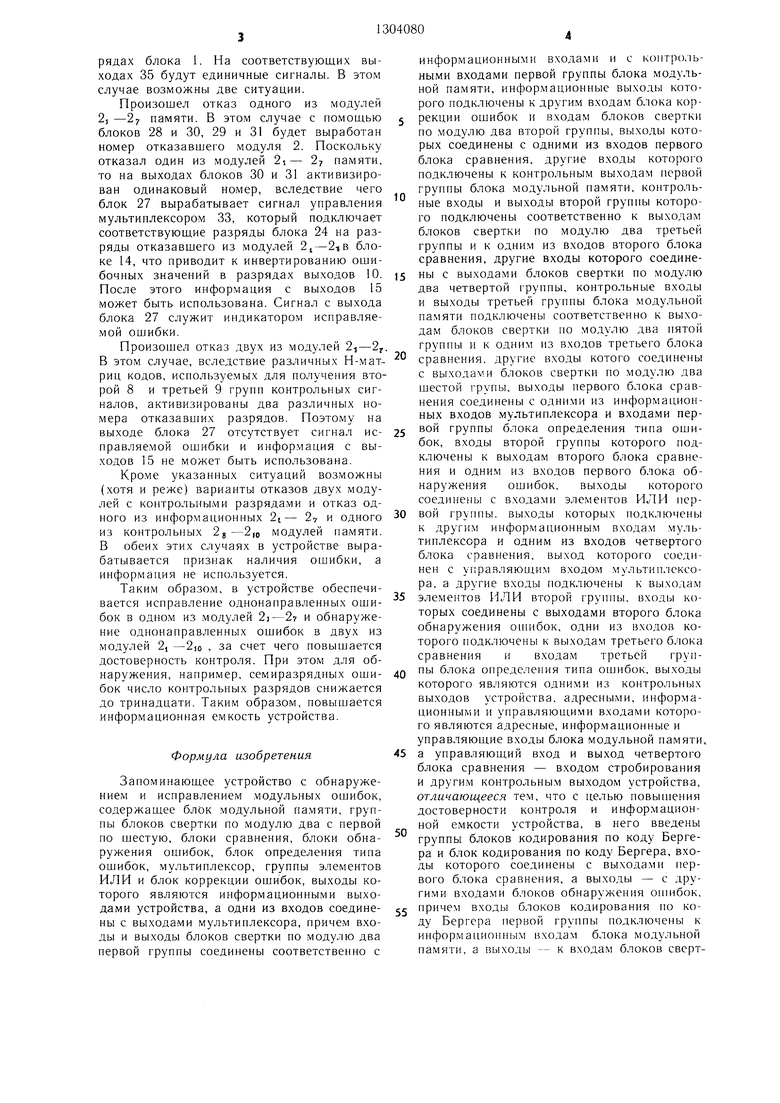

На фиг. 2 показаны семь информационных 2) -27 и три контрольных 2g - 2,5 модуля памяти, составляюш,ие блок 1 модульной памяти.

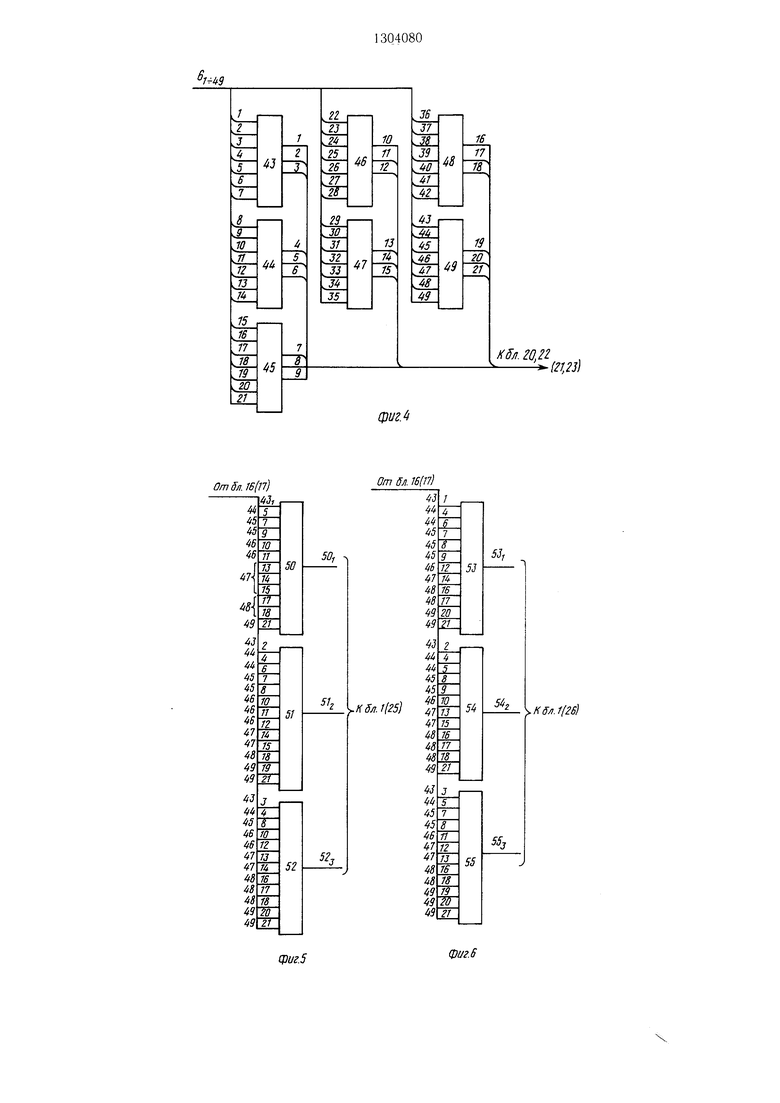

На фиг. 3 показаны блоки 36-42 свертки по модулю два, входящие в первую группу, и информационные входы 6,. . Аналогично выполнено подключение к выходам 10i-,s блоков 19 свертки по модулю два второй группы.

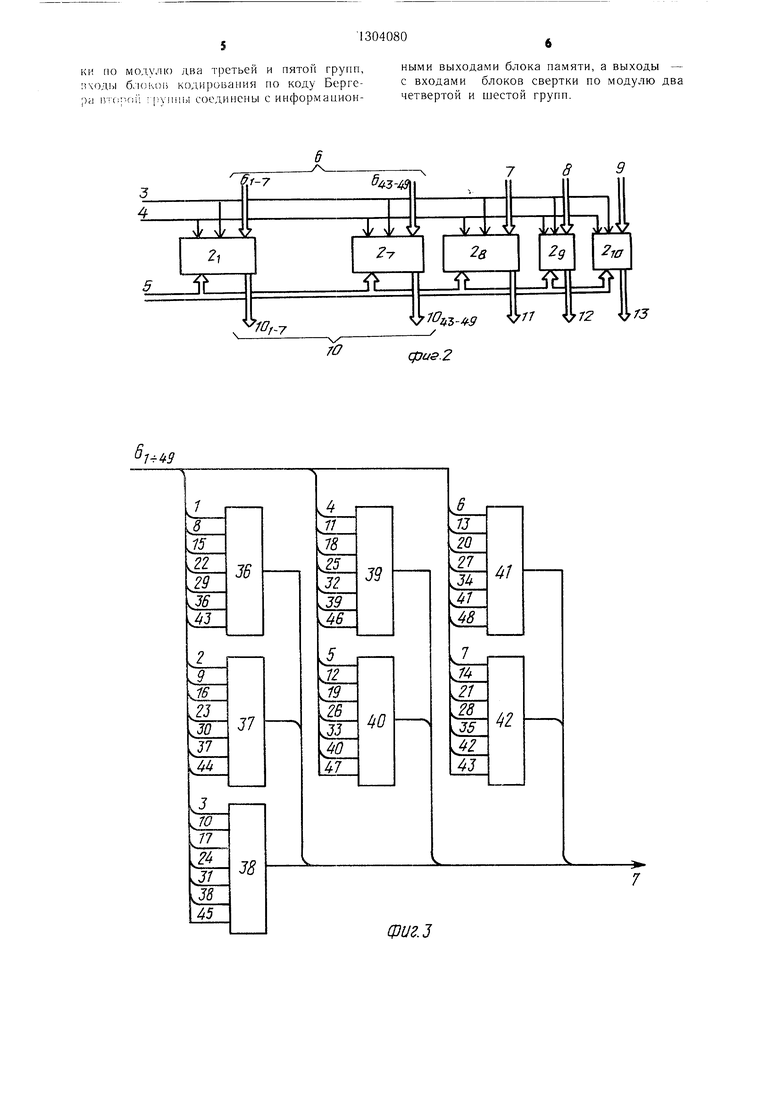

На фиг. 4 изображены блоки 43-49 кодирования по коду Бергера первой груп- 16 и показан принцип подключения их к ипформационн1 1м входам устройства. Аналогично выполняется подключение к информационным выходам блоков 17 кодирования по коду Бергера второй группы На фиг. 5 и 6 обозначены соответственно блоки 50-52 и 53-55 свертки по модулю два групп 20 и 21, 22 и 23 и показан принцип подключения их к выходам блоков 43-49 кодирования по коду Бергера.

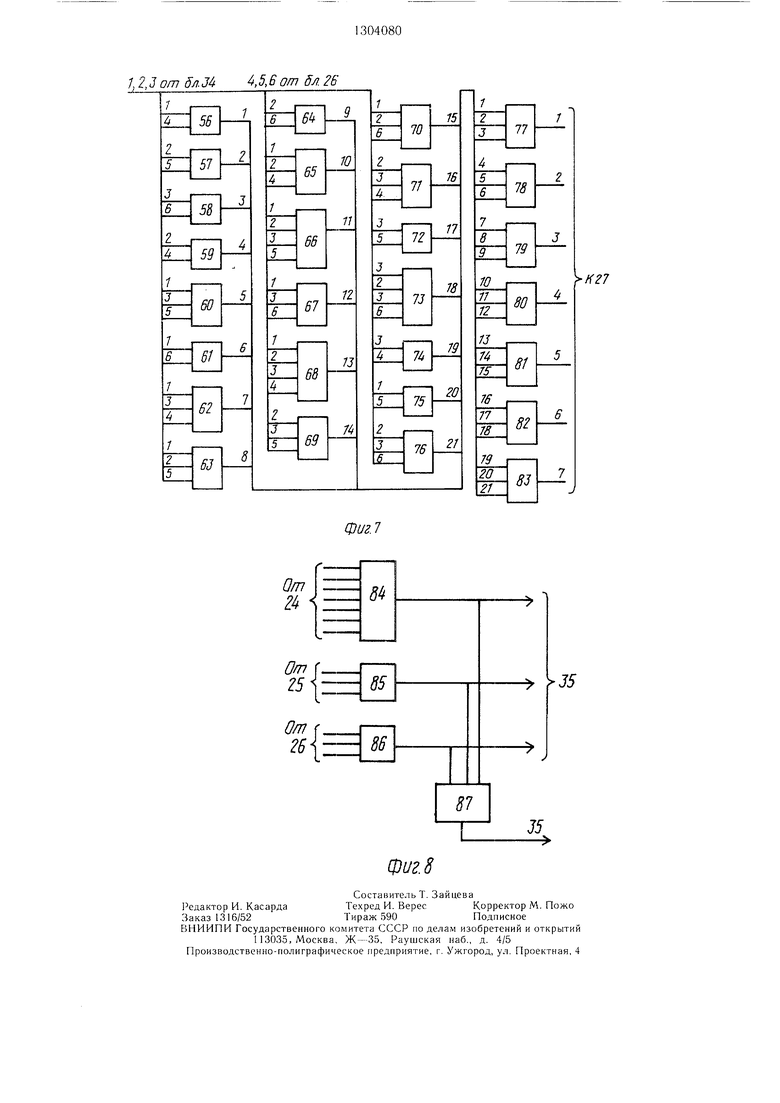

Блок 29 обнаружения ошибок, содержит

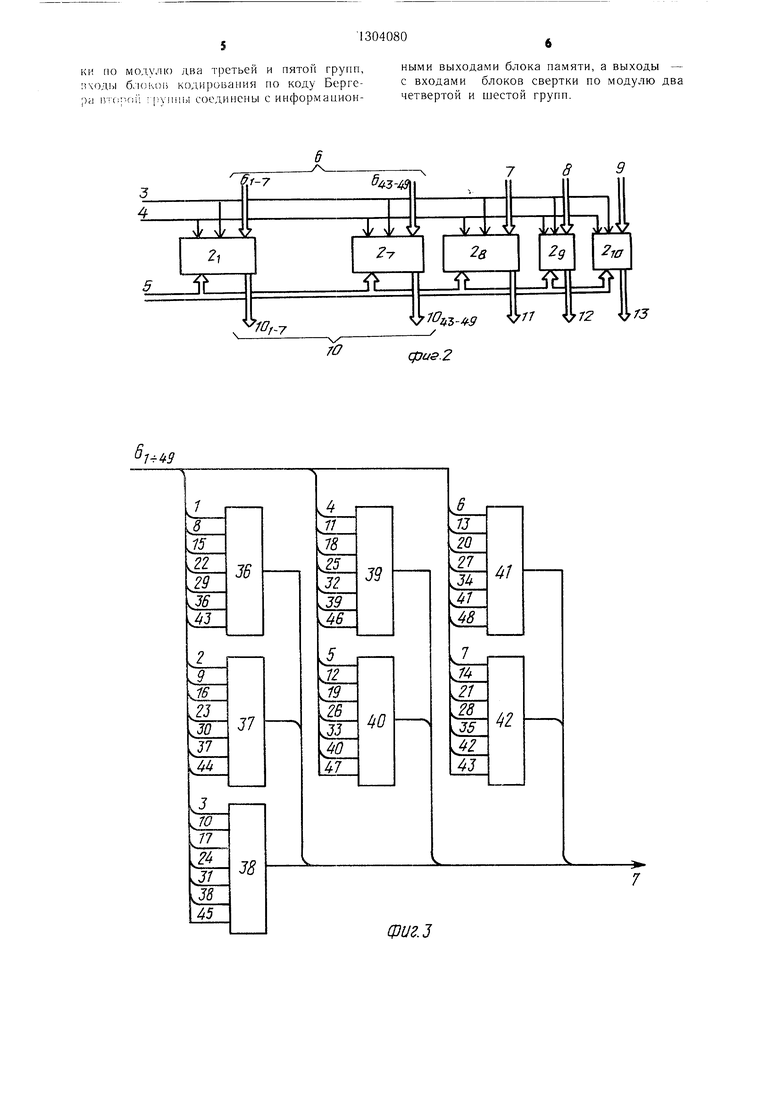

(фиг. 7) элементы И 56-76. На фиг. 7 показан принцип подключения их к выходам 341-3 блока 34 кодирования по коду Бергера, выходам 26i-( блока 26 сравнения и к входам элементов ИЛИ 77-83 группы. Блок 32 определения типа ошибки содержит (фиг. 8) элементы ИЛИ 84-86 и элемент И 87. Каждый из блоков 34, 43- 49 кодирования по коду Бергера может быть реализован в виде ПЗУ с адресной выборкой.

5 Устройство работает следующим образом.

В режиме записи информации на вход 3 подается сигнал записи, например «О. На входы 5 подается адрес ячейки памяти, в которую необходимо записать число,

° поступающее по входам 6. На вход 4 подают сигнал обращения, например «О, длительность которого должна быть больше, чем задержки в блоках 16, 20 22, 1. В . блоках 16, 18, 20, 22 происходит выработка

5 значений трех групп контрольных сигналов, которые совместно с информационными словами записываются в выбранную ячейку памяти по входам 7-9. В режиме считывания на вход 3 подается сигнал считывания, например, «О. На входы 5 посту0 пает адрес ячейки, информация из которой считывается. На вход 4 подается сигнал обращения, например «О, длительность которого должна быть больше задержек в блоках 1,17 21, 23, 25, 26-33, 14. Информация выдается на выходы 15. Одновременно в блоках 19, 17, 21, 22 образуются из считанного числа три группы контрольных сигналов, которые в блоках 24-26 поразрядно сравниваются с соответствующими группами контрольных сиг0 налов, поступающих из блока 1 по вы.ходам 11 - 13.

В зависимости от результатов сравнения возможны следующие варианты да. нейщей работы.

На выходе блоков 24-26 нули. Это означает отсутствие ошибок и на выходах 35 будут нули, вследствие чего информация на выходах 15 может быть использована.

На выходах одного из блоков 24-26

0 имеется одна или несколько единиц (предполагается пуансоновский поток отказов). На соответствующем выходе 35 будет единичный сигнал, означающий, что произошел отказ в одной из групп контрольных разрядов блока 1. Считанная информация

5 может быть использована.

На выходах всех блоков 24-26 имеются единичные сигналы. Это означает, что произошел отказ в информационных разрядах блока 1. На соответствующих выходах 35 будут единичные сигналы. В этом случае возможны две ситуации.

Произошел отказ одного из модулей 2) -2; памяти. В этом случае с помощью блоков 28 и 30, 29 и 31 будет выработан номер отказавшего модуля 2. Поскольку отказал один из модулей 2i- 2 памяти, то на выходах блоков 30 и 31 активизирован одинаковый номер, вследствие чего блок 27 вырабатывает сигнал управления мультиплексором 33, который подключает соответствующие разряды блока 24 на разряды отказавшего из модулей в блоке 14, что приводит к инвертированию ошибочных значений в разрядах выходов 10. После этого информация с выходов 15 может быть использована. Сигнал с выхода блока 27 служит индикатором исправляемой ошибки.

Произошел отказ двух из модулей 2,-2. В этом случае, вследствие различных Н-мат- риц кодов, используемых для получения второй 8 и третьей 9 групп контрольных сигналов, активизированы два различных номера отказавших разрядов. Поэтому на выходе блока 27 отсутствует сигнал исправляемой ошибки и информация с выходов 15 не может быть использована.

Кро.ме указанных ситуаций возможны (хотя и реже) варианты отказов двух модулей с контрольными разрядами и отказ одного из информационных 2t- 2 и одного из контрольных 2i-2,0 модулей памяти. В обеих этих случаях в устройстве вырабатывается признак наличия ошибки, а информация не используется.

Таким образом, в устройстве обеспечивается исправление однонаправленных ошибок в одном из .модулей 2i-2 и обнаружение однонаправленных ошибок в двух из модулей 2i -2)0 , за счет чего повышается достоверность контроля. При этом для обнаружения, например, семиразрядных ошибок число контрольных разрядов снижается до тринадцати. Таким образом, повышается информационная емкость устройства.

Формула изобретения

Запоминающее устройство с обнаружением и исправлением модульных ошибок, содержащее блок модульной памяти, группы блоков свертки по модулю два с первой по шестую, блоки сравнения, блоки обнаружения ошибок, блок определения типа ошибок, мультиплексор, группы элементов ИЛИ и блок коррекции ошибок, выходы которого являются информационными выходами устройства, а одни из входов соединены с выходами мультиплексора, причем входы и выходы блоков свертки по .модулю два первой группы соединены соответственно с

0

информационными входами и с контро.-1ь- ными входами первой группы блока модульной памяти, информационные выходы которого подключены к другим входам блока кор- 5 рекции ошибок и входам блоков свертки по модулю два второй группы, выходы которых соединены с одними из входов первого блока сравнения, другие входы которого подключены к контрольным выходам первой группы блока модульной памяти, контрольные входы и выходы второй грунпы которого подключены соответственно к выходам боТоков свертки по модулю два третьей группы и к одним из входов второго блока сравнения, другие входы которого соедине5 ны с выходами блоков свертки по модулю два четвертой группы, контрольные входы и выходы третьей группы блока модульной памяти подключены соответственно к выходам блоков свертки по модулю два нятой группы и к одним из входов третьего блока

сравнения, другие входы котого соединены с выходами блоков свертки по модулю два шестой групы, выходы первого блока сравнения соединены с одними из информационных входов мультиплексора и входами пер5 вой группы блока определения типа ошибок, входы второй группы которого подключены к выходам второго блока сравнения и одним из входов первого блока обнаружения ошибок, выходы которого соединены с входами элементов ИЛИ пер0 вой группы, выходы которых подключены к другим информационны.м входам мультиплексора и одним из входов четвертого блока сравнения, выход которого соединен с управляющим входом мультиплексора, а другие входы подключены к выходам

элементов ИЛИ второй группы, входы которых соединены с выходами второго блока обнаружения оншбок, одни из входов которого подключены к выходам третьего блока сравнения и входам третьей груп0 пы блока определения типа ошибок, выходы которого являются одними из контрольных выходов устройства, адресными, информационными и управляющими входами которого являются адресные, информационные и управляюшие входы блока модульной памяти,

5 а управляющий вход и выход четверто|-о блока сравнения - входом стробирования и другим контрольным выходом устройства, отличающееся тем, что с целью новьцнения достоверности контроля и информационной емкости устройства, в него введены группы блоков кодирования по коду Бергера и блок кодирования по коду Бергера, входы которого соединены с выходами первого блока сравнения, а выходы - с другими входами блоков обнаружения ошибок,

2 причем входы блоков кодирования по коду Бергера первой группы подключены к информационным входам блока модульной памяти, а выходы - к входам блоков свертки по модулю два третьей и пятой групп, d. ioisoij кодирования по коду Бергеру i; -o:-oii ; jiyiiiii) соединены с информационными выходами блока памяти, а выходы - с входами блоков свертки по модулю два четвертой и шеетой групп.

7

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1986 |

|

SU1322377A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1305781A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1985 |

|

SU1302328A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

Изобретение относится к вычислительной технике, .а именно к полунроводнико- вым заноминающим устройствам. Целью изобретения является повышение достоверности контроля и повышение информационной емкости устройства. Устройство содержит блок 1 модульной памяти, состоявши из модулей 2 памяти, с тремя группами контрольных входов 7-9 и выходов 11 -13, блок 14 коррекции ошибок, две группы блоJ 4 ш ков 16 и 1/ кодирования но коду Бергера, шесть групп блоков 18--23 свертки по модулю два, четыре блока 24-27 сравнения, два блока 28 и 29 обнаружения опгибок, две группы элементов ИЛИ 30 и 31, блок 32 определения типа ошибок, мультинлексор 33, блок 34 кодирования но коду Бергера. Путем ввода в устройство блоков кодирования по коду Бергера обеспечивается обнаружение многократных однонаправленных ошибок в двух, например, семиразрядных модулях 2 памяти и исправление их в одном из модулей 2 памяти, за счет чего повышается достоверность контроля устройства. При этом число контрольных разрядов в блоке 1 памяти снижается, например, до тринадцати, за счет чего повышается информационная емкость устройства. Блоки 28- 31служат для определения номеров модулей 2, в которых произошли однонаправленные ошибки во всех разрядах, а блок 32вырабатывает сигнал некорректируемой ошибки и сигналы наличия ошибок. 8 ил. (Л оо о 4 о оо о

5

JL

10,.

Г-7

/ 70

фиё.2

(риг.5

Kff/i.f/ZS)

фиг. 6

7,2, J от 5л. J4 4,5,6 от бл. 26

Н27

Составитель т. Зайцева

Редактор И. КасардаТехред И. ВересКорректор М. Пожо

Заказ 1316/52Тираж 590Подписное

Е НИИПИ Государственного комитета ССХР по делам изобретений и открытий

1 13035, Москва, Ж- 35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг. 8

| Запоминающее устройство с автономным контролем | 1980 |

|

SU881877A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 4030067, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1987-04-15—Публикация

1985-12-30—Подача