И (Обретение (j гноен гея к вычиелите.чьной технике , а именно к замоминаюшнм yeTjioii- 1;гиам со ередстнами контроля, и может 6t.iTb неио.11);«)вино для контро.ш блпко и мо:;у, 1ь- iioii иамяти при ()днона11рав.|е|;ном характере мод,1ы:ы.х О 11ибок.

Цел и-юПретения i)ii:,:iu ii ie лппи- iejiHoci и чОг:тро,1я.

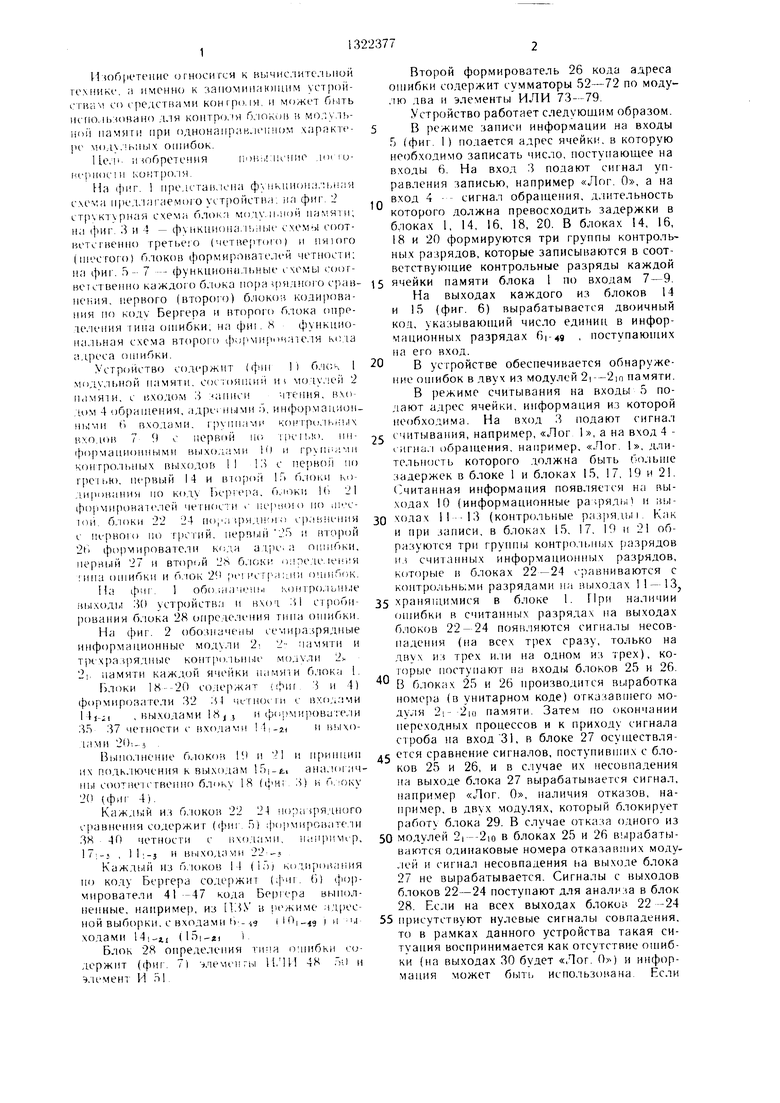

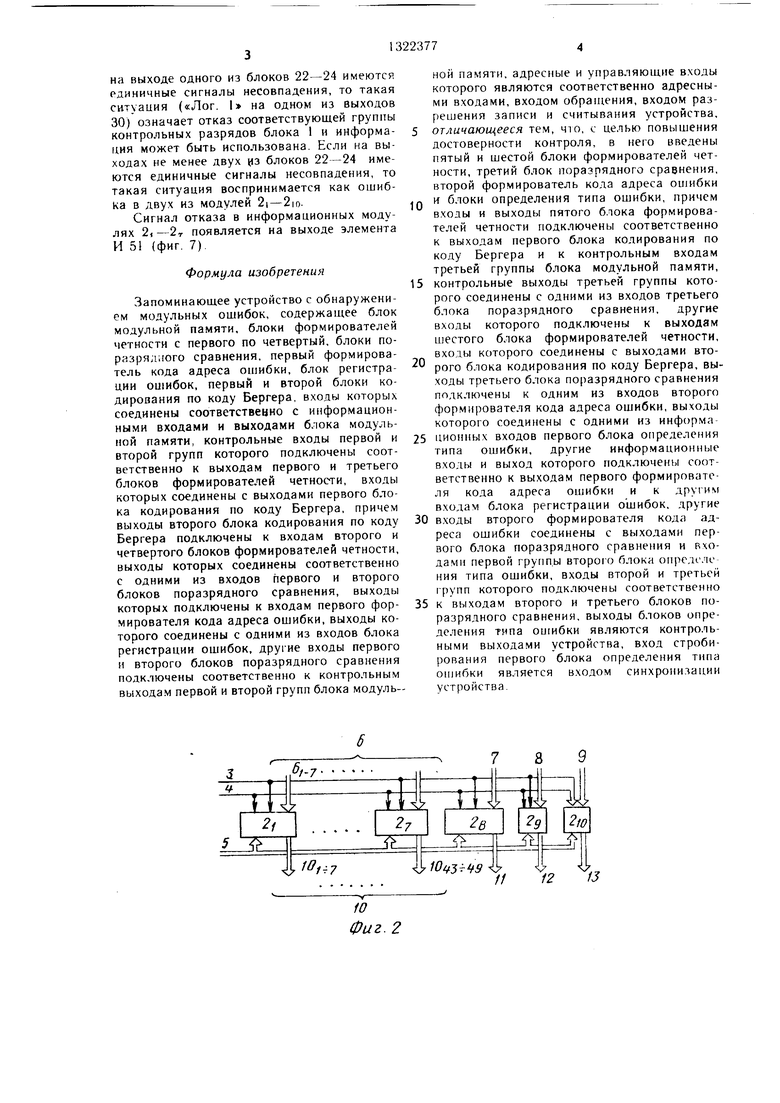

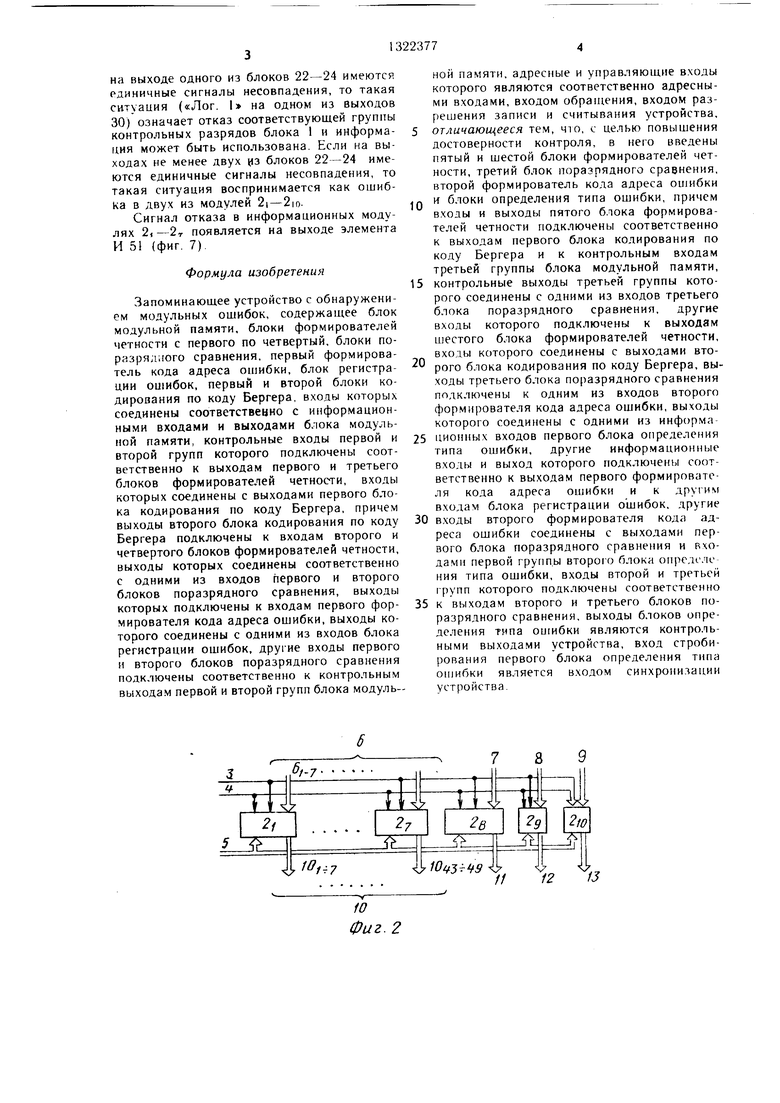

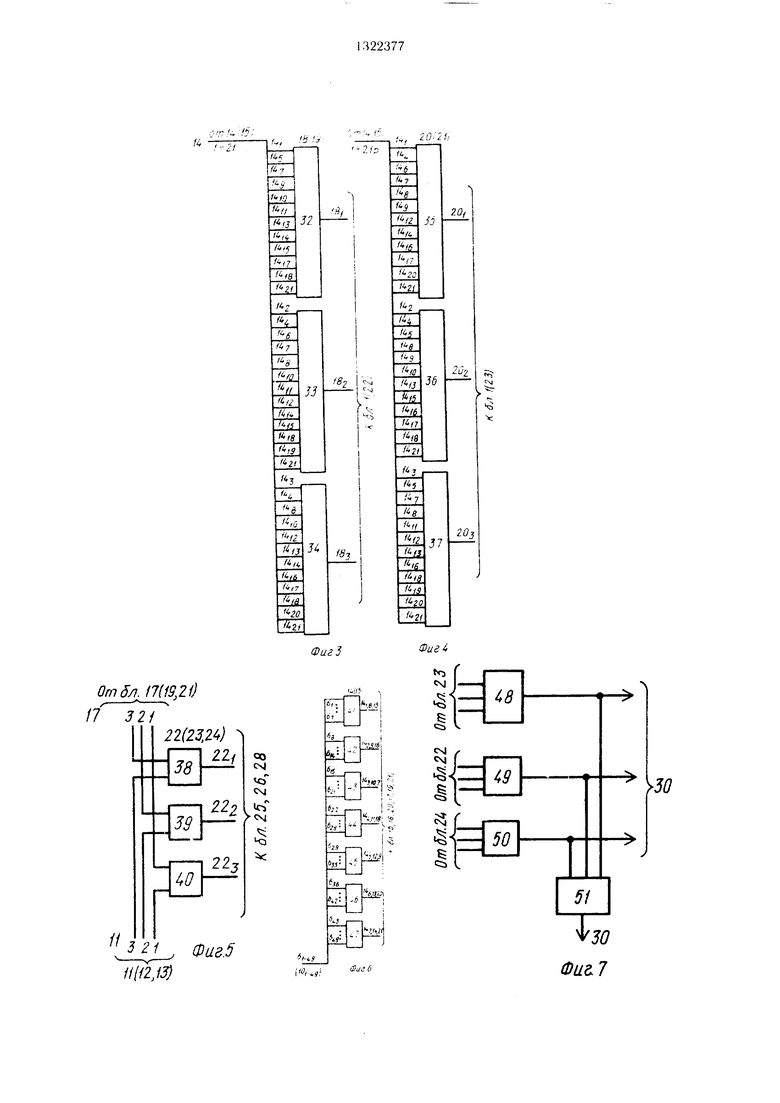

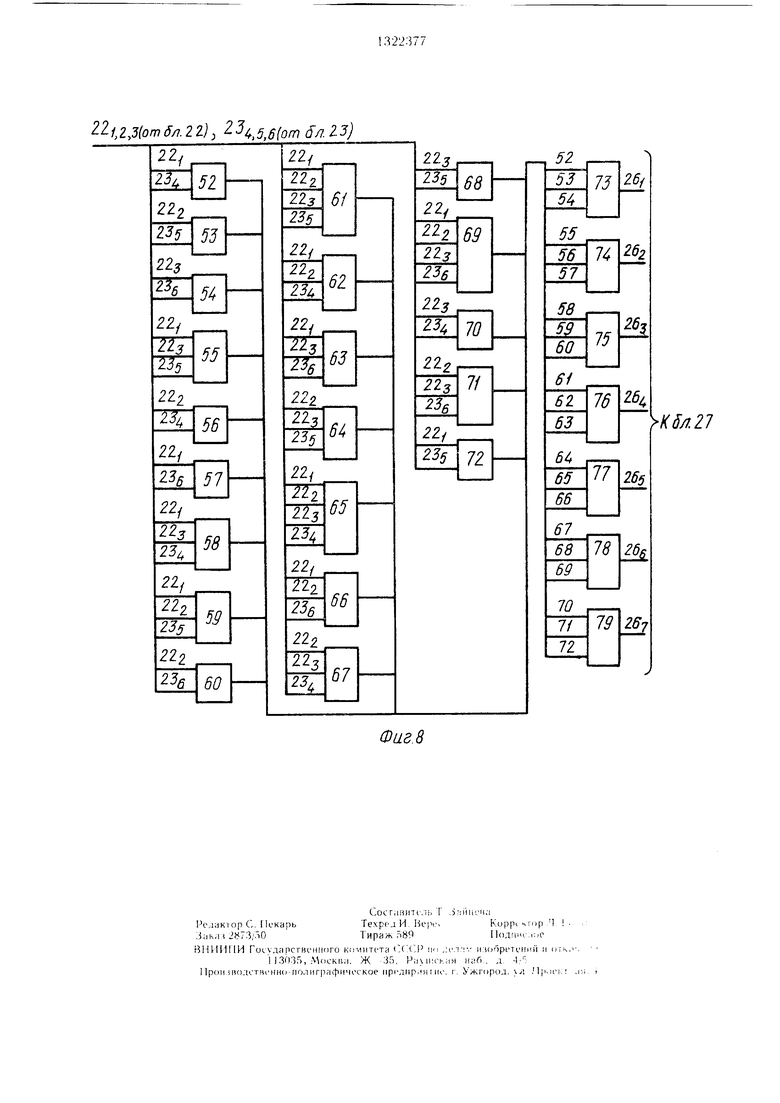

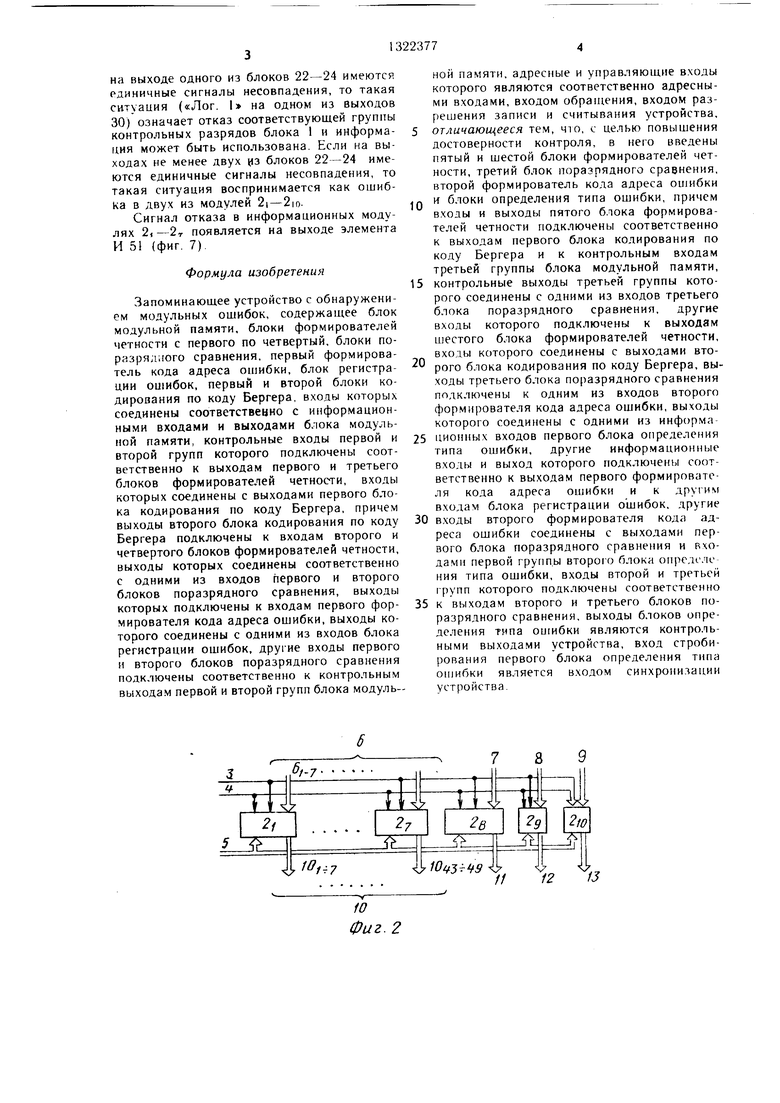

На ijinr. 1 нредетаилена ф-ункииона. мл.ии exev.a нред. ки-аемого уст ойети,1. на фиг. 2 етр ктурная ехема блокп модульной на фиг. 3 и 4 - (jiyiiKiuiona. ibHbie схемы еоот- нетегвенно третьего (четве 1Т(1 о) и пяюго (Hiecroro) блоков формирователей четности; на фиг. п- 7 -- ()ункиионал1 ные ехемы соог- ветственно каждого б.тока нора рядного нения, первого (второго) блоко;; K(Jдиpoвa- ния но коду Бергера и второго б.-юка опре- де.тения гина оижбки, на фи1 . S функцио- иальная схема второю ф;)|| 1ироиа1еля ко.та адреса ошибки.

стройство содержит (фн1 li блок I модульной иамяти, сосгояшии и( M(j4y, 2 намят и, с входом 3 : аниси , входом 4 обран1ения, адре Н1,1ми Г), инфо)мацион- ными ti входами, группами KOHi po.ii-,i-:,x вхо.и )в 7 9 с первой по Ti ieiuio, пп- |{)о 1маниоииыми выходами 10 и груп11ими контрольных выходов И : с iiepBoii по rpeibK). первый 14 и Biopoii I fi бло1чП ко- д.ирования по коду 1)ергера. блоки И) 21 i(in| iMHpoHa i( ieii петности nepisoio но iii . c- Kui. блоки 22 24 ю,, qin.u .oi о cpabiu-inui с ие|1во1(1 по г()сгнй, первьи1 2Я и второй 2t) формирователи Ko;i,a ат.ре.а опп|бки. первый 27 и второй 28 б.юки гшоеде. 1ения ;ина 01иибки и б. юк ;ien cr -a rxiiiirioK.

На фи1 1 обо;начеим 1 онтрольиые И1 1ходь 3(1 устр(;йства и вхоч : строби- роваиия блока 28 определения тина ои1ибки.

На (|)иг. 2 обозначены семиразрядные информационные моду,пи 2; 2- памяти и трех)а.рядные контро.тьные МОДУЛИ 2. 2, памяти кажд.ой ячейки иамяти блока 1.

Гзлоки IS--20 соде|1жат (rjinr i и 4) формирователи 32 :U четное и с входами 14i-ii .выходами 18, и ф(срмирова ге.чи 35 ,37 четноетн с входами li-zt и вы хота ми 20:- J .

Вынолненне блоков 1,1 и 21 и иринпии их подк.тючения к выходам Ifii-ti аналогач- 1П)1 соответ ственно блпку 18 (фн; ) и б.:оку 20 (фиг 4).

и.ч б. юков 22 2-1 пора (рядного сравнения содержит (( иг. Г)) фо|)мировате, 1И ЗК - 40 четности с пхо.чами, nanjiiiMep, 17;-; , lli-з выходами 22-3

Каждый из б.юков 14 (if)) кодирования но коду Бергера содержит (ф иг. (J) формирователи 41 -47 кода Бергера выполненные, например, из П ЛУ в (н жиме а,ч|)ес- ной . с входами Г). 4Э ) и -м ходами 14i-ii (I Ti-zi 1

Блок 28 определения типа о иибки содержит (фиг . 7) элементы И. 111 48 ,)l и .темен И al.

Второй формирователь 26 кода адреса ои1ибки содержит сумматоры 52-72 по модулю два и элементы ИЛИ 73-79,

Устройство работает следующим образом.

В режиме заниси информации на входы

5 (фиг. 1) подается адрес ячейки, в которую необходимо записать число, поступающее на входы 6, На вход 3 подают сигнал управления записью, например «Лог, О, а на

вход 4 - - сигнал обращения, длительность которого должна превосходить задержки в блоках 1, 14, 16, 18, 20, В блоках И, 16, 18 и 20 формируются три группы контрольных разрядов, которые записываются в соответствующие контрольные разряды каждой

5 ячейки памяти блока 1 по входам 7-9, На выходах каждого из блоков 14 и 15 (фиг, 6) вырабатывается двоичный код, указываю ций число единиц в информационных разрядах 61-49 , поступаюпи1х на его вход.

0 в устройстве обеспечивается обнаружение ошибок в двух из модулой памяти, В режиме считывания на входы 5 подают адрес ячейки, информация из которой необходима. На вход 3 подают сигнал

5 считывания, например, «Лог 1, а на вход 4 - сигна.1 обращения, например. «Лог, 1, длительность которого должна быть больи1е задержек в блоке 1 и блоках 15, 17, 19 и 21, (читанная информация появляется иа выходах 10 (информационные разряды) и и,10 ходах II--13 (контрольные разряды. Как и при записи, в блоках 15, 17. 19 и 21 образуются три группы контрольных разрядов И.1 считанных информационных разрядов, которые в блоках 22-24 сравниваются с контрольными разрядами па выходах 11-13,

5 :раняп1имися в блоке 1, При наличии (ипибки в считанных разрядах на выходах блоков 22-24 пояг ляются сигналы несовпадения (на всех трех сразу, только на двух из трех и,1и на одном из трех), которые поступают на входы блоков 25 и 26,

В блоках 25 и 26 нроизводится выработка номера (в унитарном коде) отказавшего модуля 2i- 2|() памяти. Затем по окончании переходных процессов и к приходу сигнала строба на вход 31, в блоке 27 осуществля5 ется сравнение сигналов, поступивших с блоков 25 и 26, и в случае их несовпадения иа выходе блока 27 вырабатывается сигнал, например «Лог, О, наличия отказов, например, в двух модулях, который блокирует работу блока 29, В случае отказа одного из

0 модулей 2|--2io в блоках 25 и 26 вырабатываются одинаковые номера отказавших моду- .1ей и сигнал несовпадения на выходе блока 27 не вырабатывается. Сигналы с выходов блоков 22-24 поступают для анализа в блок 28, Если на всех выходах блокои 22 -24

5 присутствуют нулевые сигналы совпадения, то в рамках данного устройства такая ситуация воспринимается как отсутствие ошибки (на выходах 30 будет «Лог, ) и информация может быт ь использована. Если

на выходе одного из блоков 22-24 имеются единичные сигналы несовпадения, то такая ситуация («Лог. 1 на одном из выходов 30) означает отказ соответствующей группы контрольных разрядов блока I и информация может быть использована. Если на выходах не менее двух у13 блоков 22-24 имеются единичные сигналы несовпадения, то такая ситуация воспринимается как ошибка в двух из модулей .

Сигнал отказа в информационных модулях 2i-2т появляется на выходе элемента И 51 (фиг. 7).

Формула изобретения

Запоминающее устройство с обнаружением модульных ощибок, содержащее блок модульной памяти, блоки формирователей четности с первого по четвертый, блоки по- разрял.юго сравнения, первый формирователь кода адреса ошибки, блок регистрации ошибок, первый и второй блоки кодирования по коду Бергера, входы которых соединены соответствеино с информационными входами и выходами блока модульной памяти, контрольные входы первой и второй групп которого подключены соответственно к выходам первого и третьего блоков формирователей четности, входы которых соединены с выходами первого блока кодирования по коду Бергера, причем выходы второго блока кодирования по коду Бергера подключены к входам второго и четвертого блоков формирователей четности, выходы которых соединены соответственно с одними из входов первого и второго блоков поразрядиого сравнения, выходы которых подключены к входам первого формирователя кода адреса ошибки, выходы которого соединены с одними из входов блока регистрации ошибок, другие входы первого и второго блоков поразрядного сравнения подключены соответственно к контрольным выходам первой и второй групп блока модульной памяти, адресные и управляющие входы которого являются соответственно адресиы- ми входами, входом обращения, входом разрешения записи и считывания устройства,

отличающееся тем, чпо, с целью повышения достоверности контроля, в него введены пятый и шестой блоки формирователей четности, третий блок поразрядного сравнения, второй формирователь кода адреса

Q и блоки определения типа ошибки, причем входы и выходы пятого блока формирователей четности подключены соответственно к выходам первого блока кодирования по коду Бергера и к контрольным входам третьей группы блока модульной памяти,

5 контрольные выходы третьей группы которого соединены с одними из входов третьего блока поразрядного сравнения, другие входы которого подключены к выходам шестого блока формирователей четности, входы которого соединены с выходами вто рого блока кодирования по коду Бергера, выходы третьего блока поразрядного сравнения подключены к одним из входов второго формирователя кода адреса ошибки, выходы которого соединены с одними из ииформа5 ционных входов первого блока определения типа ошибки, другие информационные входы и выход которого подключены соответственно к выходам первого формирователя кода адреса ошибки и к другим входам блока регистрации ошибок, другие

0 входы второго формирователя кода адреса ошибки соединены с выходами первого блока поразрядного сравнения и входами первой группь второго блока опредслс ния типа ошибки, входы второй и третьей групп которого подключены соответственно

5 к выходам второго и третьего блоков поразрядного сравнения, выходы блоков определения типа ошибки являются контрольными выходами устройства, вход строби- рования первого блока определения типа ошибки является входом синхрони.чации устройства.

/4

2a 2i

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1305781A1 |

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1985 |

|

SU1302328A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с обнаружением и исправлением модульных ошибок | 1985 |

|

SU1304080A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1411834A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам с самоконтролем, и может быть применено для контроля блоков модульной памяти при однонаправленном характере модульных ошибок. Целью изобретения является повышение достоверности контроля. Устройство содержит блок 1 модульной памяти, каждая ячейка которого Ш выполнена из семиразрядных информационных модулей 2|-2г памяти и трехразрядных контрольных модулей памяти, блоки 14, 15 кодирования по коду Бергера, блоки 16-21 формирователей четности, блоки 22-24 поразрядного С4}авнения, формирователи 25, 26 кода адреса ошибки, блоки 27, 28 определения типа ошибки и блок 29 регистрации ошибок. При записи и при чтении информации происходит кодирование данных в блоках 14, 15 кодирования по коду Бергера и блоках 16-21 формирователей четности. При записи три группы контрольных кодов записываются в модули 28-2io памяти и затем при считывании сравииваются поразрядно с образованными из считанных данных тремя группами контрольных кодов в блоках 22-24. В блоке 28 анализируются сигналы с выходов блоков 22-24 поразрядного сравнения и на его выходах 30 появляются сигналы наличия ошибки и сигнал ошибки в информационных разрядах. 8 ил. & (Л 00 1Ю ГчЭ 00 Фиг. 1

Фиг 5

От 5л. 17(19,21)

22(22.2) 22/

f.iv;.

MlJ

QO

NJ О

CM .«сГ

;,.«

ss

г

Фиг.5

/-4#

i Oi-.i:

S.

Фаг, О

ч.Фиг

NJ

5

са СМ

CM

а

5

5

CS

30

Фиа7

22i,2,3(om6л.21), 2. Sf, 13)

К5л.П

Фаг.8

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для диагностики памяти | 1984 |

|

SU1211810A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-07—Публикация

1986-01-02—Подача