Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со средствами контроля, и может быть использовано в модульных запоминающих устройствах при однонаправленном характере ошибок.

Цель изобретения - повыщение достоверности контроля при одновременном повышении информационной емкости устройства.

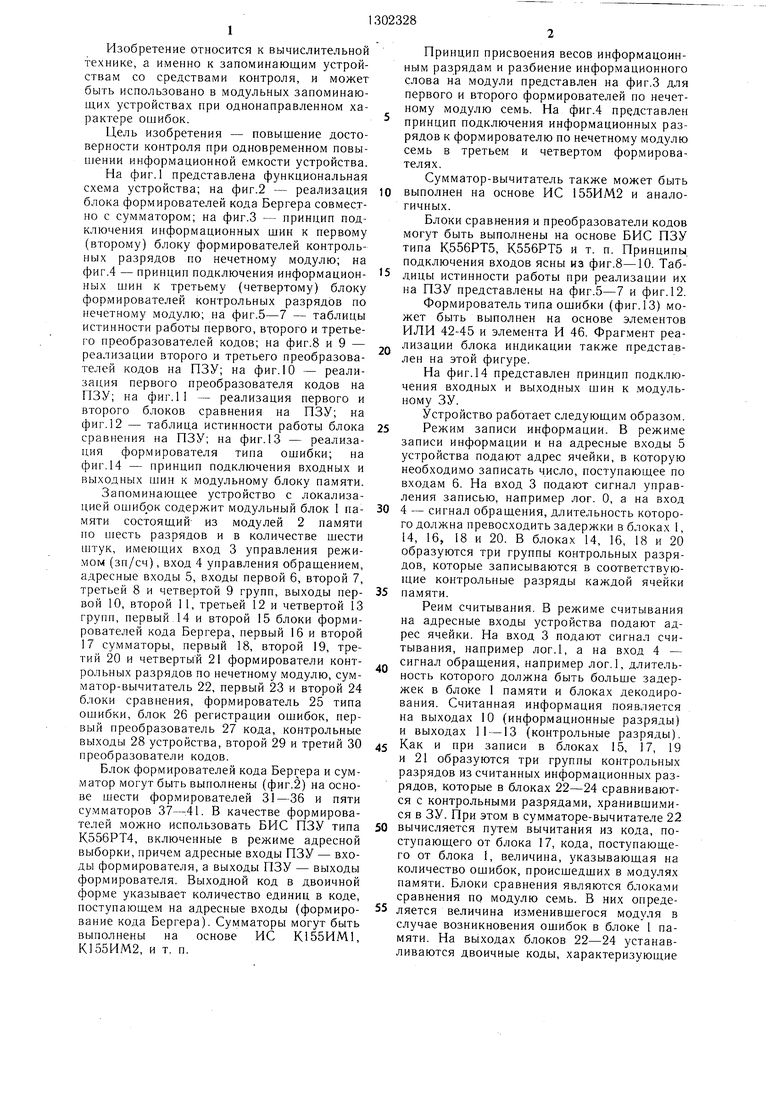

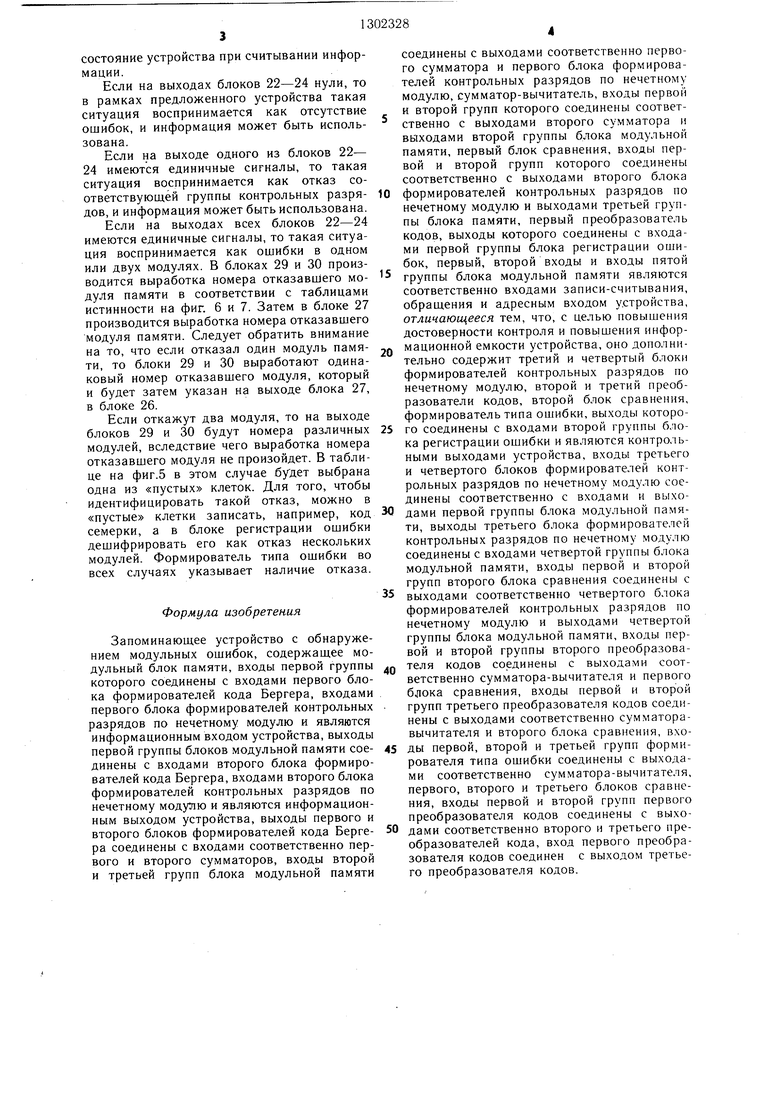

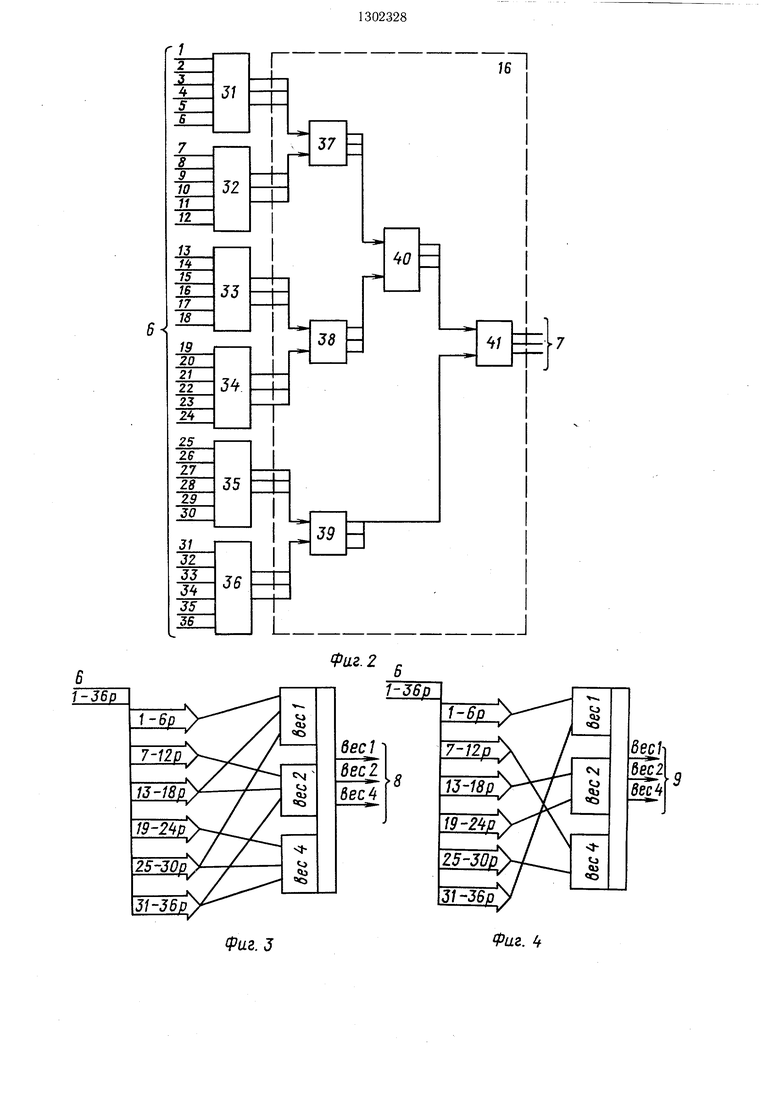

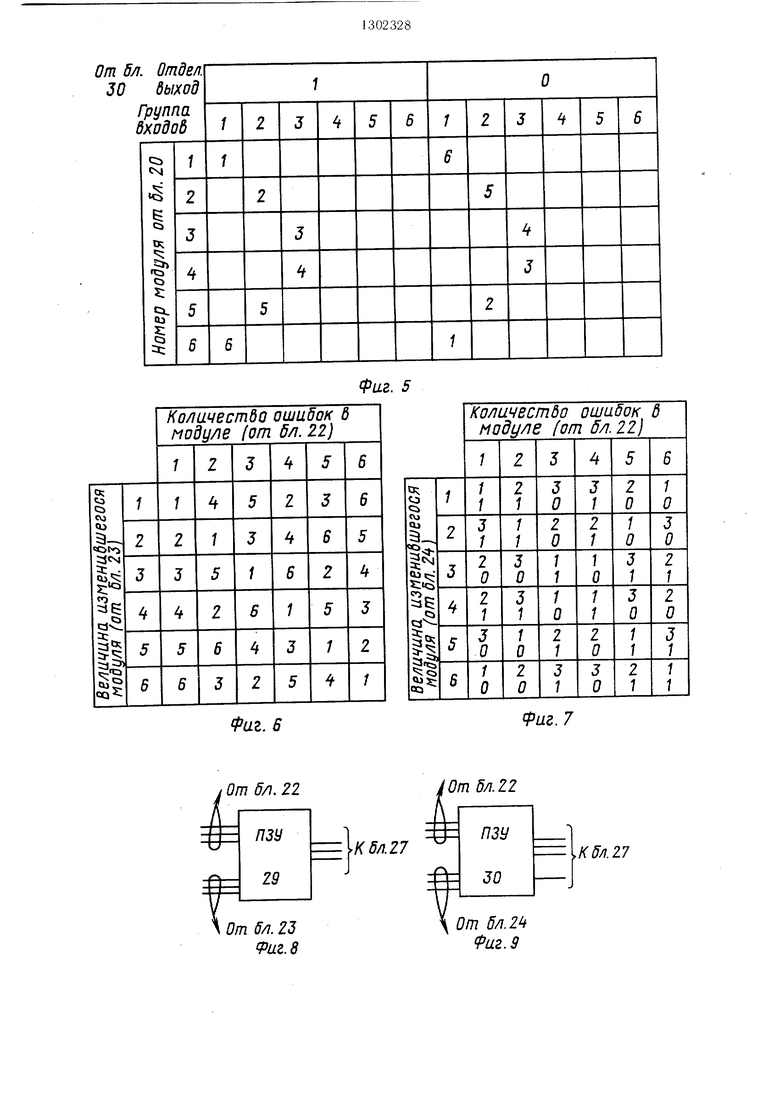

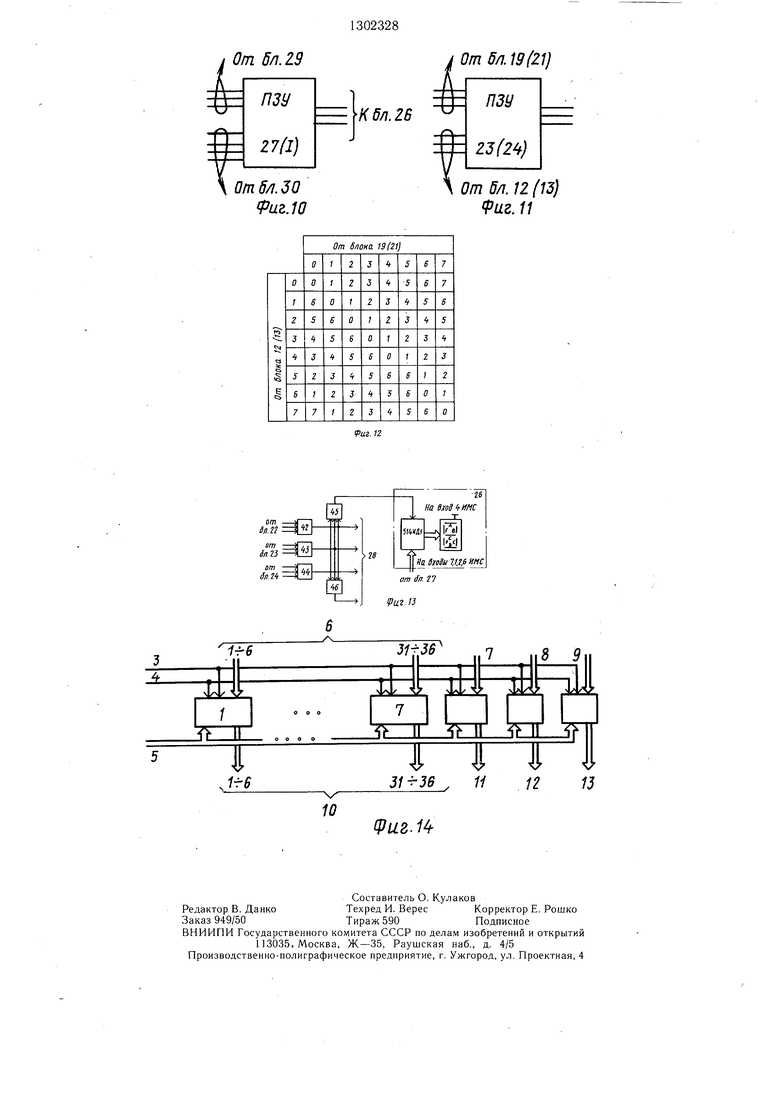

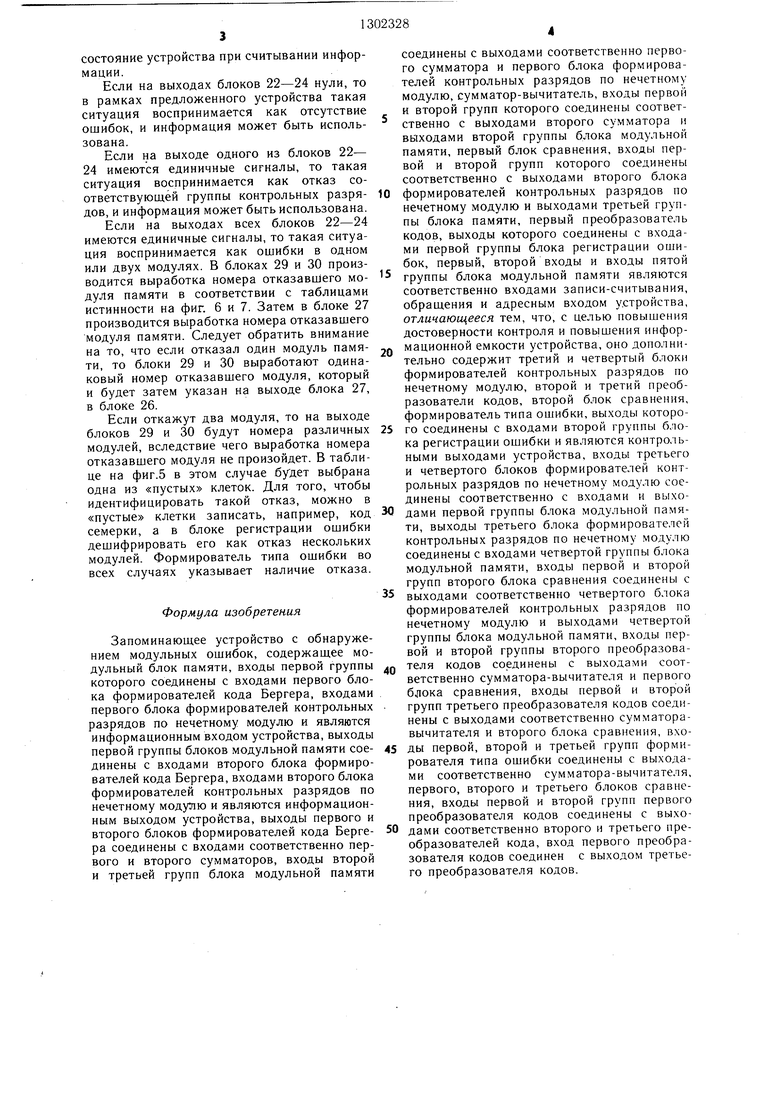

На фиг.1 представлена функциональная схема устройства; на фиг.2 - реализация блока формирователей кода Бергера совместно с сумматором; на фиг.З - принцип подключения информационных шин к первому (второму) блоку формирователей контрольных разрядов по нечетному модулю; на фиг.4 - принцип подключения информационных шин к третьему (четвертому) блоку формирователей контрольных разрядов по нечетному модулю; на фиг.5-7 - таблицы истинности работы первого, второго и третьего преобразователей кодов; на фиг.8 и 9 - реализации второго и третьего преобразователей кодов на ПЗУ; на фиг. 10 - реализация первого преобразователя кодов на ПЗУ; на фиг. II - реализация первого и второго блоков сравнения на ПЗУ; на фиг. 12 - таблица истинности работы блока сравнения на ПЗУ; на фиг.13 - реализация формирователя типа ошибки; на фиг. 14 - принцип подключения входных и выходных шин к модульному блоку памяти.

Запоминаюшее устройство с локализацией ошибок содержит модульный блок I памяти состоящий из модулей 2 памяти по шесть разрядов и в количестве шести штук, имеющих вход 3 управления режимом (зп/сч), вход 4 управления обращением, адресные входы 5, входы первой 6, второй 7, третьей 8 и четвертой 9 групп, выходы первой 10, второй 11, третьей 12 и четвертой 13 групп, первый.14 и второй 15 блоки формирователей кода Бергера, первый 16 и второй 17 сумматоры, первый 18, второй 19, третий 20 и четвертый 21 формирователи контрольных разрядов по нечетному модулю, сум- матор-вычитатель 22, первый 23 и второй 24 блоки сравнения, формирователь 25 типа ошибки, блок 26 регистрации ошибок, первый преобразователь 27 кода, контрольные выходы 28 устройства, второй 29 и третий 30 преобразователи кодов.

Блок формирователей кода Бергера и сумматор могут быть выполнены (фиг.2) на основе шести формирователей 31-36 и пяти сумматоров . В качестве формирователей можно использовать БИС ПЗУ типа К556РТ4, включенные в режиме адресной выборки, причем адресные входы ПЗУ - входы формирователя, а выходы ПЗУ - выходы формирователя. Выходной код в двоичной форме указывает количество единиц в коде, поступающем на адресные входы (формирование кода Бергера). Сумматоры могут быть выполнены на основе ИС К155ИМ1, К155ИМ2, и т. п.

Принцип присвоения весов информацоин- ным разрядам и разбиение информационного слова на модули представлен на фиг.З для первого и второго формирователей по нечетному модулю семь. На фиг.4 представлен

принцип подключения информационных разрядов к формирователю по нечетному модулю семь в третьем и четвертом формирователях.

Сумматор-вычитатель также может быть

выполнен на основе ИС 155ИМ2 и аналогичных.

Блоки сравнения и преобразователи кодов могут быть выполнены на основе БИС ПЗУ типа К556РТ5, К556РТ5 и т. п. Принципы подключения входов ясны из фиг.8-10. Таблицы истинности работы при реализации их на ПЗУ представлены на фиг.5-7 и фиг.12. Формирователь типа ошибки (фиг. 13) может быть выполнен на основе элементов ИЛИ 42-45 и элемента И 46. Фрагмент реализации блока индикации также представлен на этой фигуре.

На фиг. 14 представлен принцип подключения входных и выходных шин к .модульному ЗУ.

Устройство работает следующим образом.

Режим записи информации. В режиме записи информации и на адресные входы 5 устройства подают адрес ячейки, в которую необходимо записать число, поступающее по входам 6. На вход 3 подают сигнал управления записью, например лог. О, а на вход

4 - сигнал обращения, длительность которого должна превосходить задержки в блоках 1, 14, 16, 18 и 20. В блоках 14, 16, 18 и 20 образуются три группы контрольных разрядов, которые записываются в соответствующие контрольные разряды каждой ячейки

памяти.

Реим считывания. В режиме считывания на адресные входы устройства подают адрес ячейки. На вход 3 подают сигнал считывания, например лог.1, а на вход 4 - сигнал обращения, например лог.1, длительность которого должна быть больше задержек в блоке 1 памяти и блоках декодирования. Считанная информация появляется на выходах 10 (информационные разряды) и выходах 11 -13 (контрольные разряды).

Как и при записи в блоках 15, 17, 19 и 21 образуются три группы контрольных разрядов из считанных информационных разрядов, которые в блоках 22-24 сравниваются с контрольными разряда.ми, хранившимися в ЗУ. При этом в сумматоре-вычитателе 22

вычисляется путем вычитания из кода, поступающего от блока 17, кода, поступающего от блока 1, величина, указывающая на количество ошибок, происшедших в модулях памяти. Блоки сравнения являются блоками сравнения по модулю семь. В них определяется величина изменившегося модуля в случае возникновения ошибок в блоке 1 памяти. На выходах блоков 22-24 устанавливаются двоичные коды, характеризующие

состояние устройства при считывании информации.

Если на выходах блоков 22-24 нули, то в рамках предложенного устройства такая ситуация воспринимается как отсутствие ошибок, и информация может быть использована.

Если на выходе одного из блоков 22- 24 имеются единичные сигналы, то такая ситуация воспринимается как отказ соответствующей группы контрольных разрядов, и информация может быть использована.

Если на выходах всех блоков 22-24 имеются единичные сигналы, то такая ситуация воспринимается как ошибки в одном или двух модулях. В блоках 29 и 30 производится выработка номера отказавшего модуля памяти в соответствии с таблицами истинности на фиг. 6 и 7. Затем в блоке 27 производится выработка номера отказавшего модуля памяти. Следует обратить внимание на то, что если отказал один модуль памяти, то блоки 29 и 30 выработают одинаковый номер отказавшего модуля, который и будет затем указан на выходе блока 27, в блоке 26.

Если откажут два модуля, то на выходе блоков 29 и 30 будут номера различных модулей, вследствие чего выработка номера отказавшего модуля не произойдет. В таблице на фиг.5 в этом случае будет выбрана одна из «пустых клеток. Для того, чтобы идентифицировать такой отказ, можно в «пустые клетки записать, например, код семерки, а в блоке регистрации ошибки дешифрировать его как отказ нескольких модулей. Формирователь типа ошибки во всех случаях указывает наличие отказа.

Формула изобретения

Запоминающее устройство с обнаружением модульных ошибок, содержащее модульный блок памяти, входы первой группы которого соединены с входами первого блока формирователей кода Бергера, входами первого блока формирователей контрольных разрядов по нечетному модулю и являются информационным входом устройства, выходы первой группы блоков модульной памяти соединены с входами второго блока формирователей кода Бергера, входами второго блока формирователей контрольных разрядов по нечетному моду7 ю и являются информационным выходом устройства, выходы первого и второго блоков формирователей кода Бергера соединены с входами соответственно первого и второго сумматоров, входы второй и третьей групп блока модульной памяти

соединены с выходами соответственно первого сумматора и первого блока формирователей контрольных разрядов по нечетному модулю, сумматор-вычитатель, входы первой и второй групп которого соединены соответственно с выходами второго сумматора и выходами второй группы блока модульной памяти, первый блок сравнения, входы первой и второй групп которого соединены соответственно с выходами второго блока

0 формирователей контрольных разрядов по нечетному модулю и выходами третьей группы блока памяти, первый преобразователь кодов, выходы которого соединены с входами первой группы блока регистрации ошибок, первый, второй входы и входы пятой

5 группы блока модульной памяти являются соответственно входами записи-считывания, обращения и адресным входом устройства, отличающееся тем, что, с целью повышения достоверности контроля и повышения инфор0 мационной емкости устройства, оно дополнительно содержит третий и четвертый блоки формирователей контрольных разрядов по нечетному модулю, второй и третий преобразователи кодов, второй блок сравнения, формирователь типа ошибки, выходы которо5 го соединены с входами второй группы блока регистрации ошибки и являются контрольными выходами устройства, входы третьего и четвертого блоков формирователей контрольных разрядов по нечетному модулю соединены соответственно с входами и выхо0 дами первой группы блока модульной памяти, выходы третьего блока формирователей контрольных разрядов по нечетному модулю соединены с входами четвертой группы блока модульной памяти, входы первой и второй групп второго блока сравнения соединены с

выходами соответственно четвертого блока формирователей контрольных разрядов по нечетному модулю и выходами четвертой группы блока модульной памяти, входы первой и второй группы второго преобразовар теля кодов соединены с выходами соответственно сумматора-вычитателя и первого блока сравнения, входы первой и второй групп третьего преобразователя кодов соединены с выходами соответственно сумматора- вычитателя и второго блока сравнения, вхо5 ды первой, второй и третьей групп формирователя типа ошибки соединены с выходами соответственно сумматора-вычитателя, первого, второго и третьего блоков сравнения, входы первой и второй групп первого преобразователя кодов соединены с выхо0 дами соответственно второго и третьего преобразователей кода, вход первого преобразователя кодов соединен с выходом третьего преобразователя кодов.

Фаг. 5

Фиг. it

Фаг. 6

От 6л, 22

Фиг. 5

Фаг.7

ОтЬп.22

Ж 5л. 27

От Вл.2.9

От 5/1.30 fuz.W

От 5/1.19f21

К 5л.26

От 5/1.J2M Риг. 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1986 |

|

SU1322377A1 |

| Запоминающее устройство с обнаружением и исправлением модульных ошибок | 1985 |

|

SU1304080A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1305781A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения надежных запоминающих устройств с возможностью локализации модульных однонаправленных ошибок. Целью изобретения является повышение достоверности контроля при одновременном повьипе3 5 1111 10 НИИ информационной емкости устройства. Устройство содержит модульн1)1Й блок 1 памяти, состоящий из модулей 2 памяти, имеющий вход 3 управления режимом, вход 4 управления обращением, адресные входы 5, входы первой 6, второй 7, третьей 8. четвертой 9 групп, выходы первой 10, второй 11, третьей 12, четвертой 13 групп. Г1ервый 14 и второй 15 блоки формирователей кода Бергера, первый 16 и второй 17 сумматоры, первый 18, второй 19, третий 20, четвертый 21 формирователи контрольных разрядов по нечетному модулю, сумматор-вычита- тель 22, первый 23 и второй 24 блоки сравнения по нечетному модулю, формирователь 25 тина оц1ибки, блок 26 регистрации ошибок, нервый преобразователь 27 кода, контрольные выходы 28 устройства, второй 29 и третий 30 преобразователи кодов. Устройство позволяет обнаруживать отказы в двух модулях памяти при одновременном повышении разрядной сетки запоминаюп1его устройства в два раза. 14 и,-1. (О сл оо о tNO СО ю 00

Составитель О. Кулаков

Редактор В. ДанкоТехред И. ВересКорректор Е. Рошко

Заказ 949/50Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

9иг.1

| Запоминающее устройство с автономным контролем | 1980 |

|

SU881877A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-30—Подача