.J.

.. nril

-Дг-1

Ш гл

(Л

lie.

О

Л

и

JVT;

|Ь

а о со со со

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых узлов.

Цель изобретения - расширение функциональных возможностей за счет обеснечения контроля цифровых узлов с двунаправленными входами/выходами

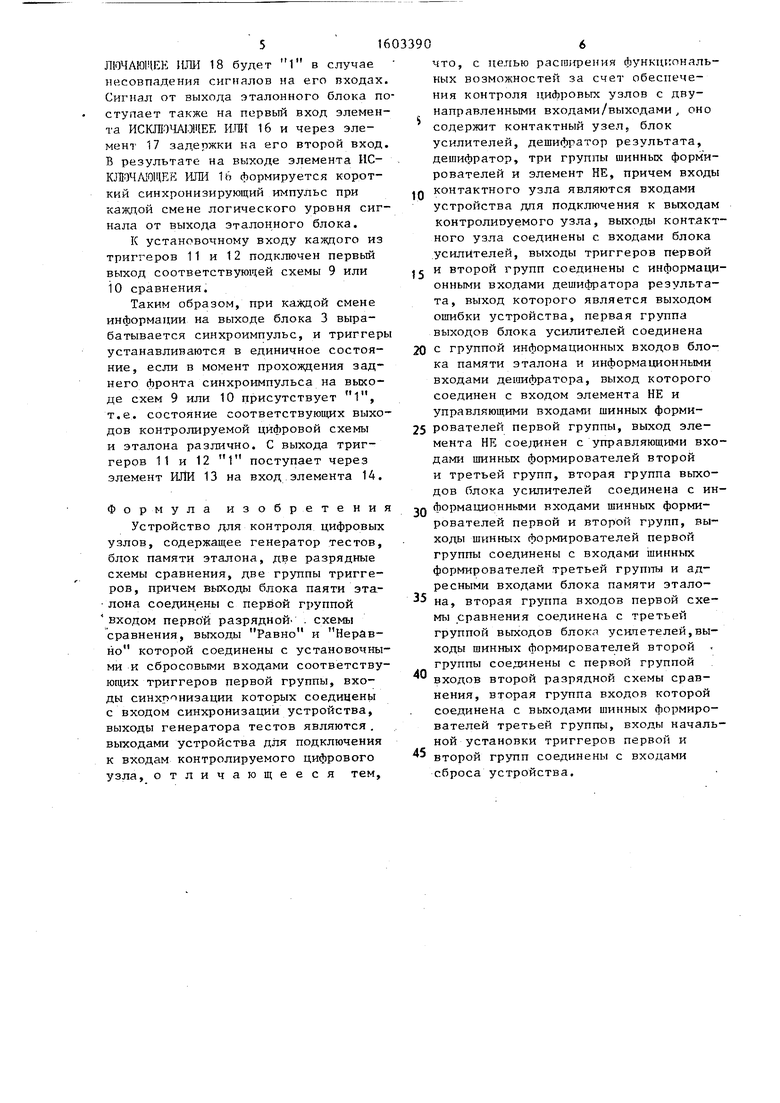

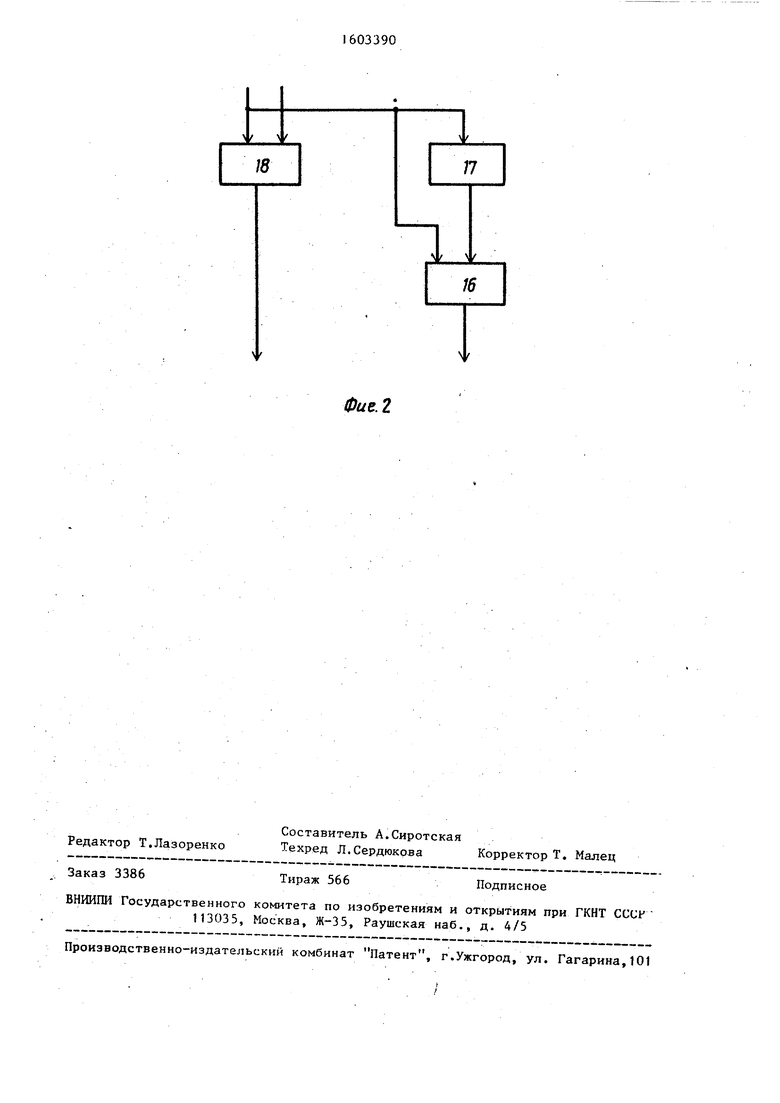

На фиг.1 показана блок-схема устройства; на фиг.2 - структура разрядной схемы сравнения.

Устройство (фиг.1) содержит контактный узел 1, блок 2 усилителей, блок 3 памяти эталона с двунаправленными выводами, дешифратор 4, элемент НЕ 5, шинные формирователи 6-8 разрядные схемы 9 и 10 сравнения, группы триггеров 11, 12, дешифратор 13 результата, контролируемый цифровой узел 14, генератор 15 тестов. Схема сравнения (фиг.2) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16, элемент 17 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18.

Устройство работает следующим образом.

Узел 1 помещается на контрочиру- емую цифровую схему, которая установлена на разъеме логической платы Затем на его входы подаются контролирующие тесты для данной платы. При этом генератором тестов может быть как устройство тестового контроля, работающее по заранее составленной контролирующей программе, так и непосредственно само, готовое изделие цифровой техники.

На входы контролируемого цифрового узла поступают двоичные наборы, являющиеся производными входных наборов.

Усилители обеспечивают съем со всех выводов контролируемой цифровой схемы сигналов, которые поступают на входы блока 2, служащих для уменьшения емкостной и активной нагрузки на проверяемый узел. Сигналы с выходов блока 2 поступают непосредственно или через формирователи 6 на входы блока 3.

На каждом тестовом наборе двоичные сигналы, поступающие на выводы блока 3, являю1циеся его входами, одновременно поступают также и на информационные входы соответствующего дешифратора 4. Дешифратор 4 необходим для определения состояния входов/выходов блока 3. В случае, если двоичный набор на входах блока 3 оп0

G

ределлет состояние входов/выходов как входов, то на выходе дешифратора 4 вырабатывается 1, которая передается на управляющий вход первого фор мирователя 6 и открывает его для передачи информации с соответствующих выходов блока 2 на входы/выходы блока 3. Одновременно О с выхода элемента 5 поступает на управляющие входы формирователей 7 и 8, переводя их в третье состояние.

В случае, если двоичный набор на входах блока 3 определяет состояние

, входов/выходов блока 3 как выходов, на выходе дешифратора А появляется О, который передается на управляющий вход первого формирователя 6 и переводит его в третье состояние,

0 т.е. отключает его от входов/выходов блока 3. С выхода элемента 5 1 поступает на управляющие входы второго 7 и третьего 8 формирователей и открывает их. В результате через

5 третий формирователь 8 информация с входов/выходов блока 3 поступает на первые входы схем 10 сравнения, а на вторые входы этих схем сравнения поступает через второй формирователь 7 информация с соответствующих выводов блока 2 от контролируемой цифровой схемы.

С выходов блока 3 двоичная информация поступает на первые входы схем 9 сравнения, на вторые входы которых

5 поступает информация с соответствующих выходов контролируемой цифровой схемы через узел 1 и блок 2.

Каждая из схем сравнения первой 9 и второй 10 групп работает следующим образом. В процессе контроля время смены информации на выходах эталонного и контролируемого блоков может несколько отличаться друг от друга, причем смена двоичной инфор мации на выходах эталонного блока 3 происходит несколько позже, чем на выходах контролируемого блока. Поэтому в схемах 9, 10 сравнения предусмотрено вырабатывание сигнала синхронизации, позволяющего однозначно определять наличие или отсутствие совпадения сигналов контролируемого и эталонного блоков. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 осуществля5 вт постоянное сравнение сигналов от эталонного блока, поступающих на его первый вход, и сигналов от конт ролируемой схемы, поступакнцих на второй вход. На выходе элемента ИСКQ

0

Л10ЧАЮ1НЕЕ ИЛИ 18 будет 1 в случае несовпадения сигналов на его входах. Сигнал от выхода эталонного блока поступает также на первый вход элемента ИСКЛЮЧАГЛЦЕЕ И.Ш1 16 и через элемент 17 задержки на его второй вход. В результате на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 формируется короткий синхронизирующий импульс при каждой смене логического уровня сигнала от выхода Эталонного блока.

К установочному входу каждого из триггеров 11 и 12 подключен первый выход соответствующей схемы 9 или 10 сравнения.

Таким образом, при кавдой смене информации на выходе блока 3 вырабатывается синхроимпульс, и триггеры устанавливаются в единичное состояние, если в момент прохождения заднего фронта синхроимпульса на выходе схем 9 или 10 присутствует 1, т.е. состояние соответствующих выходов контролируемой цифровой схемы и эталона различно. € выхода триггеров 11 и 12 1 поступает через элемент ИЛИ 13 на вход элемента 14.

Формула изобретения

Устройство для контроля цифровых узлов, содержащее генератор тестов, блок памяти эталона, две разрядные схемы сравнения, две группы триггеров, причем выходы блока паяти эта- лона соединены с первой группой входом первой разрядной . схемы сравнения, выходы Равно и Неравно которой соединены с установочными и сбросовыми входами соответствующих триггеров первой группы, входы синхронизации которых соединены с входом синхронизации устройства, выходы генератора тестов являются , выходами устройства для подключения к входам контролируемого цифрового узла, отличающееся тем.

5

0

5

0

5

0

5

что, с целью расплфения функциональных возможностей за счет обеспечения контроля цифровых узлов с двунаправленными входами/выходами оно содержит контактны11 узел,, блок усилителей, дешифратор результата, дешифратор, три группы шинных формирователей и элемент НЕ, причем входы контактного узла являются входами устройства для подключения к выходам контролируемого узла, выходы контактного узла соединены с входами блока усилителей, выходы триггеров первой и второй групп соединены с информационными входами дешифратора результата, выход которого является выходом ошибки устройства, первая группа выходов блока усилителей соединена с группой информационных входов блока памяти эталона и информационными входами дешифратора, выход которого соединен с входом элемента НЕ и управляющими входами шинных формирователей первой группы, выход элемента НЕ соеданен с управляющими входами шинных формирователей второй и третьей групп, вторая группа выходов блока усилителей соединена с информационными входами шинных формирователей первой и второй групп, выходы шинных формирователей первой группы соединены с входами шинных формирователей третьей группы и адресными входами блока памяти эталона, вторая группа входов первой схемы сравнения соединена с третьей группой выходов блокп усипетелей,выходы шинных формирователей второй группы соединены с первой группой входов второй разрядной схемы сравнения, вторая группа входов которой соединена с выходами шинных формирователей третьей группы, входы начальной установки триггеров первой и второй групп соединены с входами сброса устройства.

18

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых узлов. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля цифровых узлов с двунаправленными входами/выходами. Устройство содержит генератор тестов 15, блок памяти 3 эталона, две разрядные схемы сравнения 9, 10, две группы триггеров 11, 12, контактный узел 1, блок усилителей 2, дешифратор результа 13, дешифратор 4, три группы шинных формирователей 6, 7, 8, элемент НЕ 5. 1 ил.

Фие. 2

| Устройство для контроля больших интегральных схем (БИС) | 1980 |

|

SU918904A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР №1295399, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-30—Публикация

1987-06-04—Подача