Изобретение относится к вычислительной .технике и может быть использовано в системах приемопередачи дискретной информации.

Цель изобретения - расширение функциональных возможностей устройства за счет передачи источнику информации квитанции об освобождении памяти в кодовой форме.

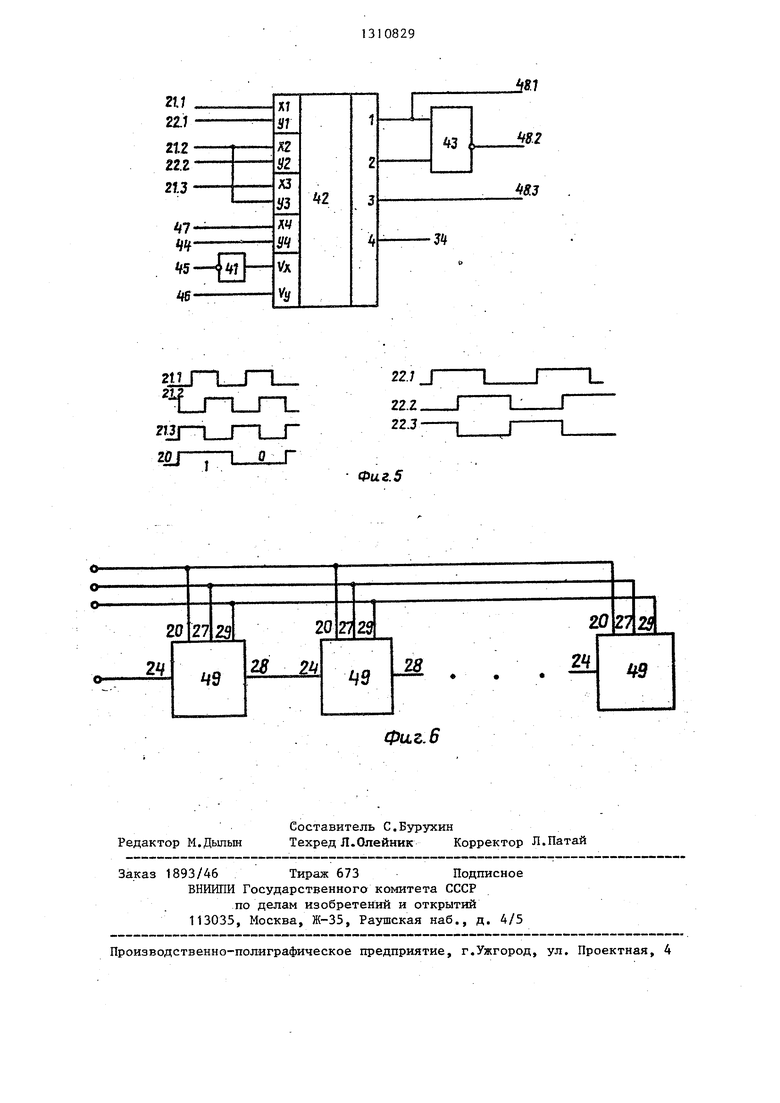

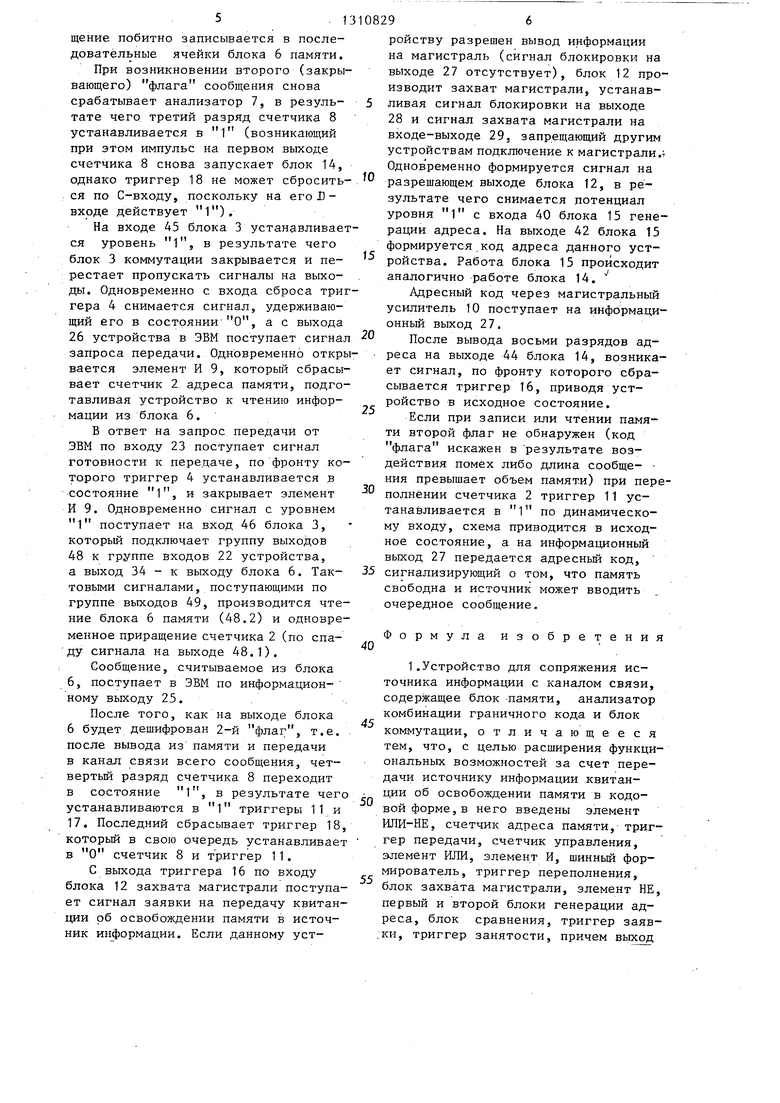

На фиг. 1 представлена функциональная схема устройства; на фи-г. 2 - схема анализатора комбинации граничного кода; на фиг, 3 - схема блока генерации адреса; на фиг, 4 - временная диаграмма работы анализатора комбинации граничного кода; на фиг.5 схема блока коммутации и временные диаграммы тактовых сигналов; на фиг, 6 - пример использования устройства.

Устройство содержит элемент ИЛИ-НЕ 1, счетчик 2 адреса памяти, блок 3 коммутации, триггер 4 передачи, элемент ИЛИ 5, блок 6 памяти, анализатор 7 комбинации граничного кода счетчик 8 управления, элемент И 9, шинный формирователь 10, триггер 11 переполнения, блок 12 захвата магистрали, элемент НЕ 13, первый, второй блоки 14 и 15 генерации адреса, блок 16 сравнения, триггер 17 заявки, триггер 18 занятости, выход 19, информационный вход 20, группы тактовых входов 21 и 22, вход 23 готовности к передаче, вход.24 блокировки магистрали, информационный выход 25, выход 26 запроса передачи, адресный выход 27, выход 28 блокировки магистрали, вход-выход 29 захвата магистрали.

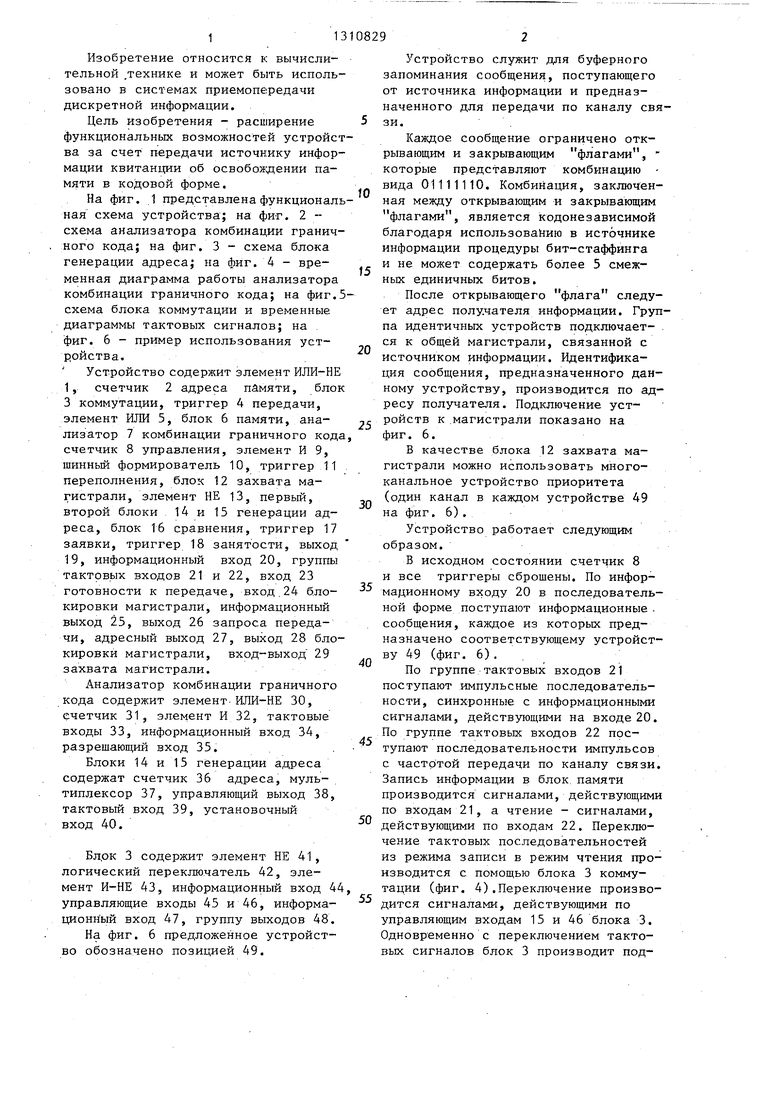

Анализатор комбинации граничного кода содержит элемент-ИЛИ-НЕ 30, счетчик 31, элемент И 32, тактовые входы 33, информационный вход 34, разрешающий вход 35,.

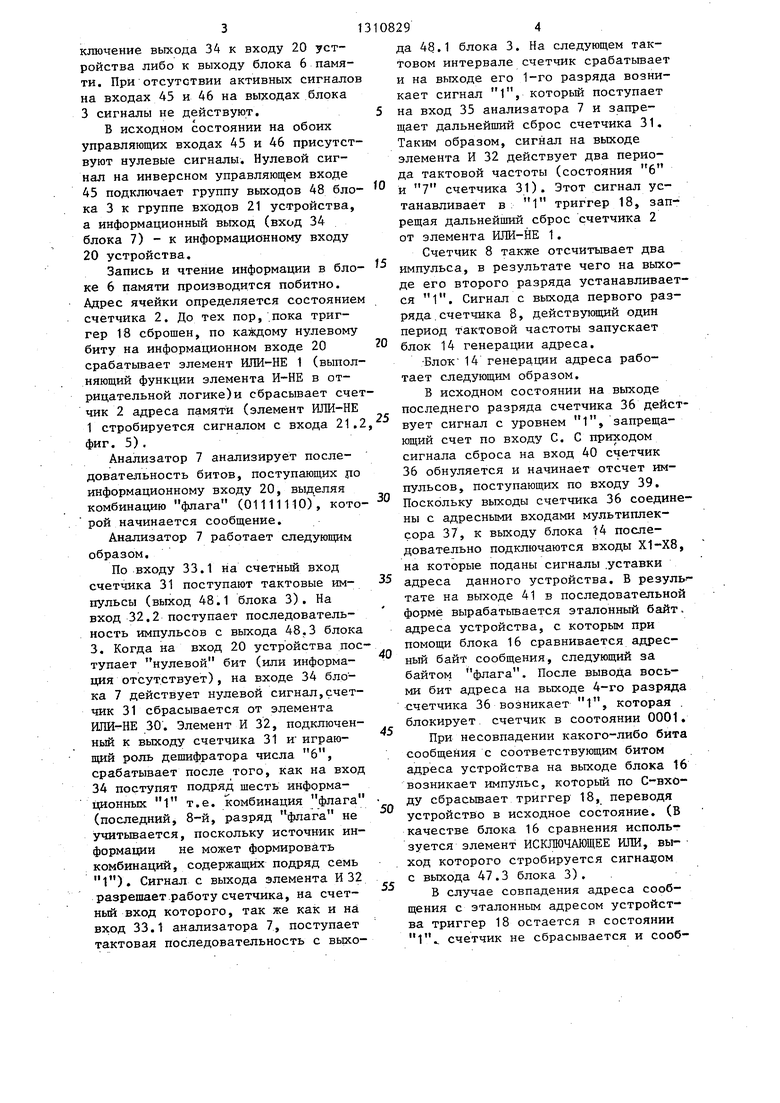

Блоки 14 и 15 генерации адреса содержат счетчик 36 адреса, мультиплексор 37, управляющий выход 38, тактовый вход 39, установочный вход 40,

Блрк 3 содержит элемент НЕ 41, логический переключатель 42, элемент И-НЕ 43, информационный вход 44 управляющие входы 45 и 46, информационный вход 47, группу выходов 48,

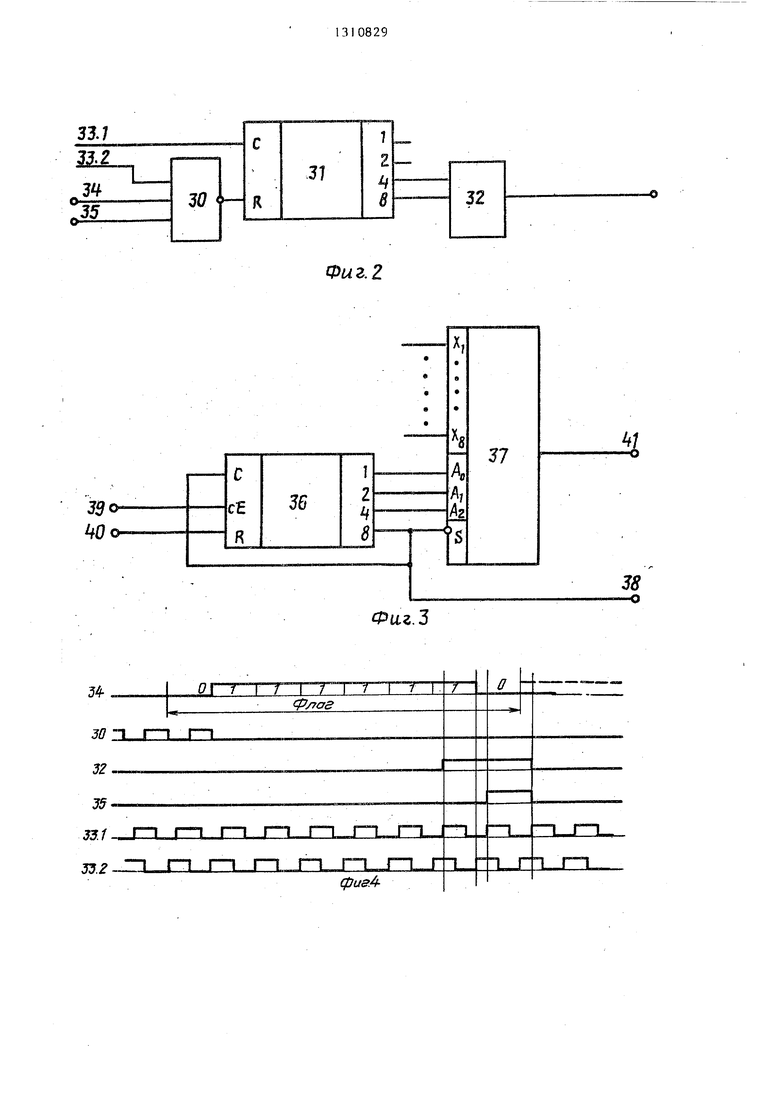

На фиг, 6 предложенное устройство обозначено позицией 49.

5

0

5

Устройство служит для буферного запоминания сообщения, поступающего от источника информации и предназначенного для передачи по каналу связи.

Каждое сообщение ограничено открывающим и закрывающим флагами, которые представляют комбинацию вида 01111110. Комбинация, заключенная между открывающим и закрывающим флагами, является кодонезависимой благодаря использованию в источнике информации процедуры бит-стаффинга и не может содержать более 5 смежных единичных битов,

После открывающего флага следует адрес получателя информации. Группа идентичных устройств подключает- . ся к общей магистрали, связанной с источником информации. Идентификация сообщения, предназначенного данному устройству, производится по адресу получателя. Подключение устройств к.магистрали показано на фиг, 6,

В качестве блока 12 захвата магистрали можно использовать многоканальное устройство приоритета (один канал в каждом устройстве 49 на фиг, 6),

Устройство работает следующим образом,

В исходном состоянии счетчик 8 и все триггеры сброшены. По инфор- мационному входу 20 в последовательной форме поступают информационные . сообщения, каждое из которых предназначено соответствующему устройству 49 (фиг. 6). .

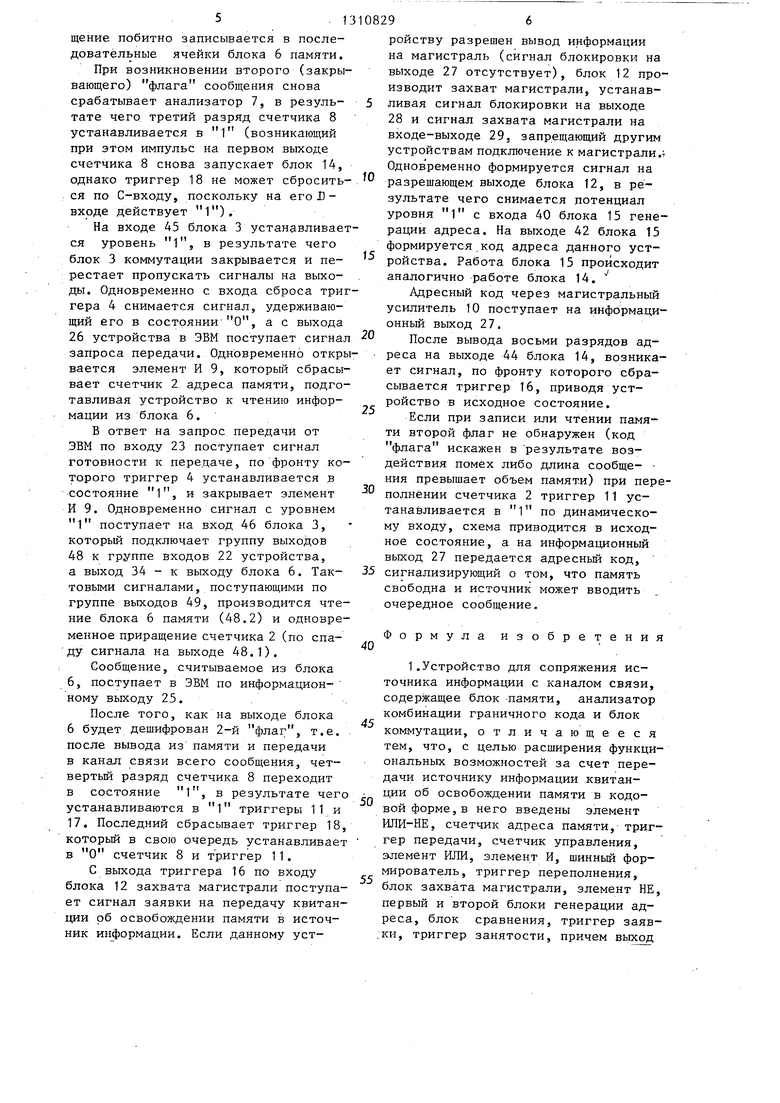

По группе тактовых входов 21 поступают импульсные последовательности, синхронные с информационными сигналами, действующими на входе 20, По группе тактовых входов 22 поступают последовательности импульсов с частотой передачи по каналу связи. Запись информации в блок памяти производится сигналами, действующими по входам 21, а чтение - сигналами, действующими по входам 22, Переключение тактовых последовательностей из режима записи в режим чтения производится с помощью блока 3 коммутации (фиг, 4).Переключение производится сигналами, действующими по управляющим входам 15 и 46 блока 3. Одновременно с переключением тактовых сигналов блок 3 производит под0

0

5

0

5

ключение выхода 34 к входу 20 устройства либо к выходу блока 6 памяти. При отсутствии активных сигнало на входах 45 и 46 на выходах блока 3 сигналы не действуют,

В исходном состоянии на обоих управляющих входах 45 и 46 присутствуют нулевые сигналы. Нулевой сигнал на инверсном управляющем входе 45 подключает группу выходов 48 блока 3 к группе входов 21 устройства, а информационный выход (вход 34 блока 7) - к информационному входу 20 устройства.

Запись и чтение информации в блоке 6 памяти производится побитно. Адрес ячейки определяется состояние счетчика 2. До тех пор, .пока триггер 18 сброшен, по каждому нулевому биту на информационном входе 20 срабатывает элемент ИЛИ-НЕ 1 (выполняющий функции элемента И-НЕ в отрицательной логике)и сбрасывает счечик 2 адреса памяти (элемент ИЛИ-НЕ 1 стробируется сигналом с входа 21. фиг. 5).

Анализатор 7 анализирует последовательность битов, поступающих ро информационному входу 20, выделяя комбинацию флага (01111110), которой начинается сообщение.

Анализатор 7 работает следующим образом.

По входу 33.1 на счетный вход счетчика 31 поступают тактовые импульсы (выход 48.1 блока 3). На вход 32.2 поступает последовательность импульсов с выхода 48.3 блока 3. Когда на вход 20 устройства поступает нулевой бит (или информация отсутствует), на входе 34 блока 7 действует нулевой сигнал,счетчик 31 сбрасывается от элемента ИЛИ-НЕ 30. Элемент И 32, подключенный к выходу счетчика 31 и- играющий роль дешифратора числа 6, срабатывает после того, как на вход 34 поступят подряд шесть информационных 1 т.е. комбинация флага (последний, 8-й, разряд флага не учитывается, поскольку источник информации не может формирова.ть комбинаций, содержащих подряд семь 1), Сигнал с выхода элемента И 32 разрешает .работу счетчика, на счетный вход которого, так же как и на вход 33.1 анализатора 7, поступает тактовая последовательность с вько

10

{5

20

3108294

да 48.1 блока 3. На следующем тактовом интервале счетчик срабатьшает и на выходе его 1-го разряда возникает сигнал 1, который поступает на вход 35 анализатора 7 и запрещает дальнейший сброс счетчика 31, Таким образом, сигнал на выходе элемента И 32 действует два периода тактовой частоты (состояния 6 и 7 счетчика 31). Этот сигнал устанавливает в; 1 триггер 18, запрещая дальнейший сброс счетчика 2 от элемента ИЛИ-НЕ 1.

Счетчик 8 также отсчитывает два импульса, в результате чего на выходе его второго разряда устанавливается 1. Сигнал с выхода первого разряда . счетчика 8, действующий один период тактовой частоты запускает блок 14 генерации адреса.

Блок 14 генерации адреса работает следующим образом.

В исходном состоянии на выходе последнего разряда счетчика 36 действует сигнал с уровнем 1, запрещающий счет по входу С. С приходом сигнала сброса на вход 40 счетчик 36 обнуляется и начинает отсчет импульсов, поступающих по входу 39. Поскольку выходы счетчика 36 соединены с адресными входами мультиплексора 37, к выходу блока t4 последовательно подключаются входы XI-Х8, на которые поданы сигналы .уставки адреса данного устройства. В резуль - тате на выходе 41 в последовательной форме вырабатьтается эталонный байт. адреса устройства, с которьм при помощи блока 16 сравнивается адресный байт сообщения, следующий за байтом флага. После вывода восьми бит адреса на выходе 4-го разряда счетчика 36 возникает 1, которая блокирует счетчик в соотоянии 0001,

При несовпадении какого-либо бита сообщения с соответствующим битом адреса устройства на выходе блока 16 возникает импульс, который по С-вхо- ду сбрасьтает триггер 18, переводя устройство в исходное состояние. (В качестве блока 16 сравнения используется элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вы- ход которого стробируется сигнаиом с выхода 47.3 блока 3). .

В случае совпадения адреса сообщения с эталонньм адресом устройства триггер 18 остается в состоянии 1 счетчик не сбрасывается и сооб30

35

40

45

50

55

5. 13

щение побитно записывается в последовательные ячейки блока 6 памяти.

При возникновении второго (закрывающего) флага сообщения снова срабатывает анализатор 7, в результате чего третий разряд счетчика 8 устанавливается в 1 (возникающий при этом импульс на первом выходе счетчика 8 снова запускает блок 14, однако триггер 18 не может сброситься по С-входу, поскольку на его D- входе действует 1).

На входе 45 блока 3 устанавливается уровень 1, в результате чего блок 3 коммутации закрывается и перестает пропускать сигналы на выходы. Одновременно с входа сброса триггера 4 снимается сигнал, удерживающий его в СОСТОЯНИИ О, а с выхода 26 устройства в ЭВМ поступает сигнал запроса передачи. Одновременно открывается элемент И 9, которьш сбрасывает счетчик 2 адреса памяти, подготавливая устройство к чтению инфор- мадии из блока 6.

В ответ на запрос передачи от ЭВМ по входу 23 поступает сигнал готовности к передаче, по фронту которого триггер 4 устанавливается в состояние 1, и закрывает элемент И 9. Одновременно сигнал с уровнем 1 поступает на вход 46 блока 3, который подключает группу выходов 48 к группе входов 22 устройства, а выход 34 - к выходу блока 6. Тактовыми сигналами,, поступающими по группе выходов 49, производится чтение блока 6 памяти (48.2) и одновременное приращение счетчика 2 (по спа- ду сигнала на выходе 48.1).

Сообщение, считываемое из блока 6, поступает в ЭВМ по информационному выходу 25.

После того, как на выходе блока 6 будет дешифрован 2-й флаг, т.е. после вывода из памяти и передачи в канал связи всего сообщения, чет- вертьш разряд счетчика 8 переходит в состояние 1, в результате чего устанавливаются в 1 триггеры 11 и 17. Последний сбрасывает три;ггер 18, который в свою очередь устанавливает в О счетчик 8 и триггер 11.

С выхода триггера 16 по входу блока 12 захвата магистрали поступает сигнал заявки на передачу квитанции об освобождении памяти в источник информации. Если данному уст

96

ройству разрешен вывод информации на магистраль (сигнал блокировки на выходе 27 отсутствует), блок 12 производит захват магистрали, устанавливая сигнал блокировки на выходе 28 и сигнал захвата магистрали на входе-выходе 29. запрещающий другим устройствам подключение к магистрали. Однов ременно формируется сигнал на разрешающем выходе блока 12, в результате чего снимается потенциал уровня 1 с входа 40 блока 15 генерации адреса. На выходе 42 блока 15 формируется код адреса данного устройства. Работа блока 15 происходит аналогично работе блока 14.

Адресный код через магистральный усилитель 10 поступает на информационный выход 27.

После вывода восьми разрядов адреса на выходе 44 блока 14, возникает сигнал, по фронту которого сбрасывается триггер 16, приводя устройство в исходное состояние.

Если при записи или чтении памяти второй флаг не обнаружен (код флага искажен в результате воздействия помех либо длина сообще- - ния превышает объем памяти) при пере

полнении счетчика 2 триггер 11 устанавливается в 1 по динамическому входу, схема приводится в исходное состояние, а на информационный выход 27 передается адресный код, сигнализирующий о том, что память свободна и источник может вводить очередное сообщение.

Формула изобретения

1.Устройство для сопряжения источника информации с каналом связи, содержащее блок памяти, анализатор комбинации граничного кода и блок коммутации, отличающееся тем, что, с целью расширения функциональных возможностей за счет передачи источнику информации квитанции об освобождении памяти в кодовой форме, в него введены элемент ИЛИ-НЕ, счетчик адреса памяти, триггер передачи, счетчик управления, элемент ИЛИ, элемент И, шинный формирователь, триггер переполнения, блок захвата магистрали, элемент НЕ, первый и второй блоки генерации адреса, блок сравнения, триггер заяв- ки, триггер занятости, причем выход

Ш

5

20

25

I1310829

первого разряда счетчика управления соединен с разрешающим входом анализатора комбинации граничного кода и с установочным входом первого блока генерации адреса, выход которого 5 соединен с первым информационным входом блока сравнения, второй информа.ционньй вход которого соединен с первьм входом элемента ИЛИ-НЕ, с

;первым информационным входом блока коммутации и с входом устройства для подключения информационного выхода источника информации, второй вход элемента ИЛИ-НЕ соединен с единичным выходом триггера занятости, нулевой выход которого соединен с входами сброса счетчика управления и триггера переполнения, единичньй вход которого соединен с выходом четвертого разряда счетчика.управления, выход третьего разряда которого соединен с входом режима блока памяти, с входом запрета блока коммутации, с нулевым входом триггера передачи, с первым входом элемента И, с информационным входом триггера занятости, с входом устройства для подключения входа запроса передачи, единичный вход триггера занятости соединен с входом

разрешения счетчика управления и с выходом анализатора, комбинации граничного кода, тактовьй вход триггера занятости соединен с выходом блока сравнения, нулевой вход триггера занятости соединен с выходом триггера заявки и с входом запроса блока захвата -магистрали, выход блокировки магистрали и выход захвата магистрали которого соединены соответственно с выходами устройства для подключения входа блокировки магистрали ЭВМ и с входом-выходом устройства для подключения входа-выхода захвата магистрали ЭВМ, вход блокировки магистрали блока захвата магистрали соединен с входом устройства для подключения выхода блокировки магистрали ЭВМ, выход раз- решения обмена блока захвата магистрали через элемент НЕ подключен к установочному входу второго блока

;.генерации адреса, информационньй выход которого через шинньй форми рователь соединен с выходом устройст

ва для подключения адресного входа ЭВМ, выход синхронизации блока генерации адреса соединен с динамическим

30

35

40

45

50

.-55

вх вх ге то ра сб эл ко с вт ну ди с вы ны с ци то до дл ад ны ад дл ти ци ме пе ад вх па на по ру гр ди ка па ка вы гр ко ко

ю ко эл пр не хо эл ра вь та и ля щи

Ш

5

20

25

5 30

35

40

45

50

55

входом триггера заявки, единичный вход которого соединен с выходом триггера переполнения,динамический вход которого соединен с выходом последнего разряда счетчика адреса памяти, вход сброса которого соединен с выходом элемента ИЛИ, первый, второй входы которого соединены соответственно с выходами элементов ШШ-НЕ и И, второй вход элемента И соединен с нулевьм выходом триггера передачи, динамический вход которого соединен с входом устройства для подключения выхода готовности к передаче, единичный выход триггера передачи соединен с входом разрешения блока коммутации, второй информационньй вход которого соединен с информационным выходом блока памяти и выходом устройства для подключения информационного входа, адресные входы блока памяти соединены с информационными выходами счетчика адреса памяти, группа входов устройства для подключения первой группы тактирующих выходов источника информации соединена с третьим входом элемента ИЛИ-НЕ, с тактовыми входами первого и второго блоков генерации адреса и с первой группой тактовых входов блока коммутации, вторая группа тактовых входов которого соединена с группой входов устройства для подключения к второй группе тактирующих выходов источника информации, группа выходов блока коммутации соединена со счетными входами счетчика управления и счетчика адреса памяти, со стробируюпщми входами блока памяти и блока сравнения и тактовыми входами анализатора комбинации граничного кода, информационньй вход которого соединен с выходом блока коммутации,

2. Устройство по п.1,о т л и ч а- ю щ е е с я тем, что анализатор комбинации граничного кода содержит элемент ИЛИ-НЕ,- счетчик и элемент И, причем выход элемента ИЛИ-НЕ соединен с входом сброса счетчика, выходы двух разрядов которого через элемент И подключены к выходу дешифратора, счетный вход счетчика и пер- вьй вход элемента ИЛИ-НЕ образуют тактовые входы анализатора, второй и третий входы элемента ИЛИ-НЕ являются информационным и разрешающим входами анализатора.

20J

1 . 0., Г

Редактор М.Дьшьш

Составитель С.Бурухин

Техред Л.Олейник Корректор Л.Патай

Заказ 1893/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Фиг. 5

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для сопряжения | 1987 |

|

SU1434441A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах нриемо- передачи дискретной информации. Целью изобретения является расширение функциональных возможностей устройства за счет передачи источнику информации квитанции об освобояздении памяти в кодовой форме. Устройство содержит элемент ИЛИ-НЕ 1, счетчик 2 адреса памяти,блок 3 коммутации, триггер 4 передачи, элемент ИЛИ 5, блок 6 памяти, анализатор 7 комби- . нации граничного кода, счетчик 8 управления, элемент И 9, шинный формирователь 10, триггер 11 переполнения, блок 12 захвата магистрали, элемент НЕ 13, первый 14 и второй 15 блоки генерации адреса, блок 16 сравнения,триггер 17 заявки,триггер 18 занятости. Благодаря введению триггеров и блоков генерации адреса устройство может идентифицировать предназначенное ему.сообщение и сообщать источнику информации о готовности к передаче очередного сообщения путем по- сьшки квитанции об освобождении мяти по информационной магистрали в виде адресного кода данного устройства. 1 з.п. ф-лы, 6 ил. (Л со ге со

| Патент США № 3469085, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство с автономным контролем | 1978 |

|

SU763973A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-05-15—Публикация

1985-12-29—Подача