оо

Jiib

.4

Изобретение относится к вычислительной технике и может быть использовано для сопряжения двух вычислительных систем, имеющих интерфейс типа магистрали.

Целью изобретения является повышение пропускной способности устройства за счет организации прямой логической связи между магистралями.

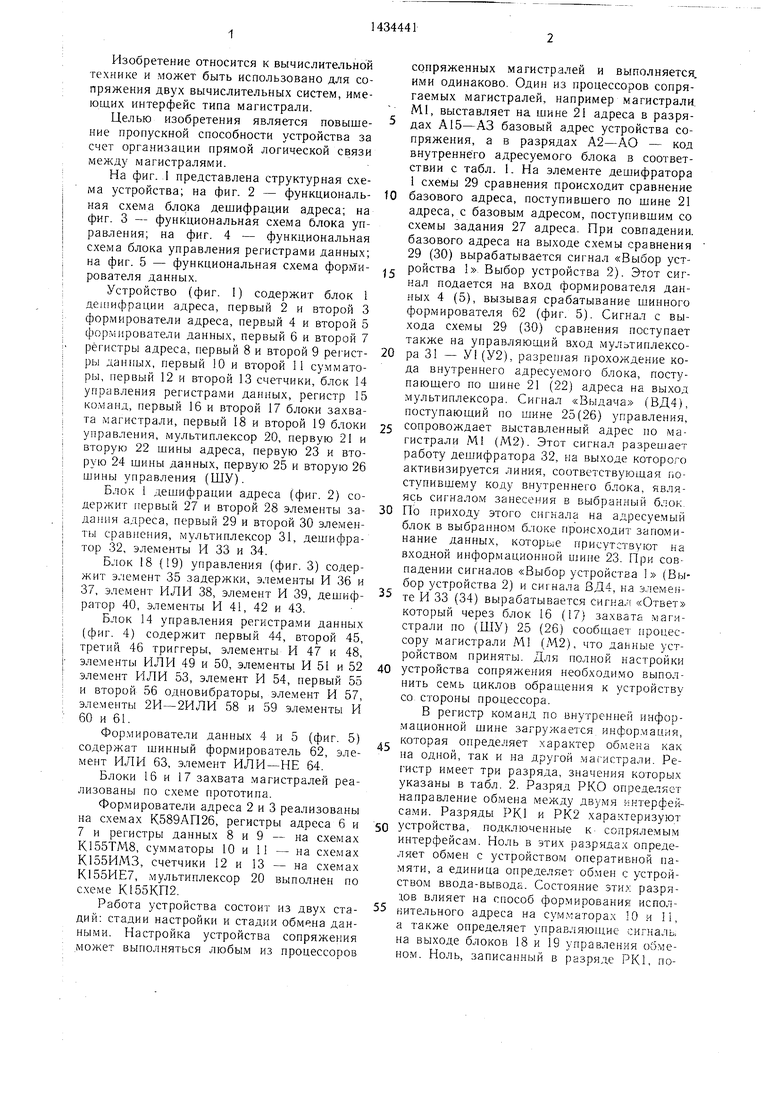

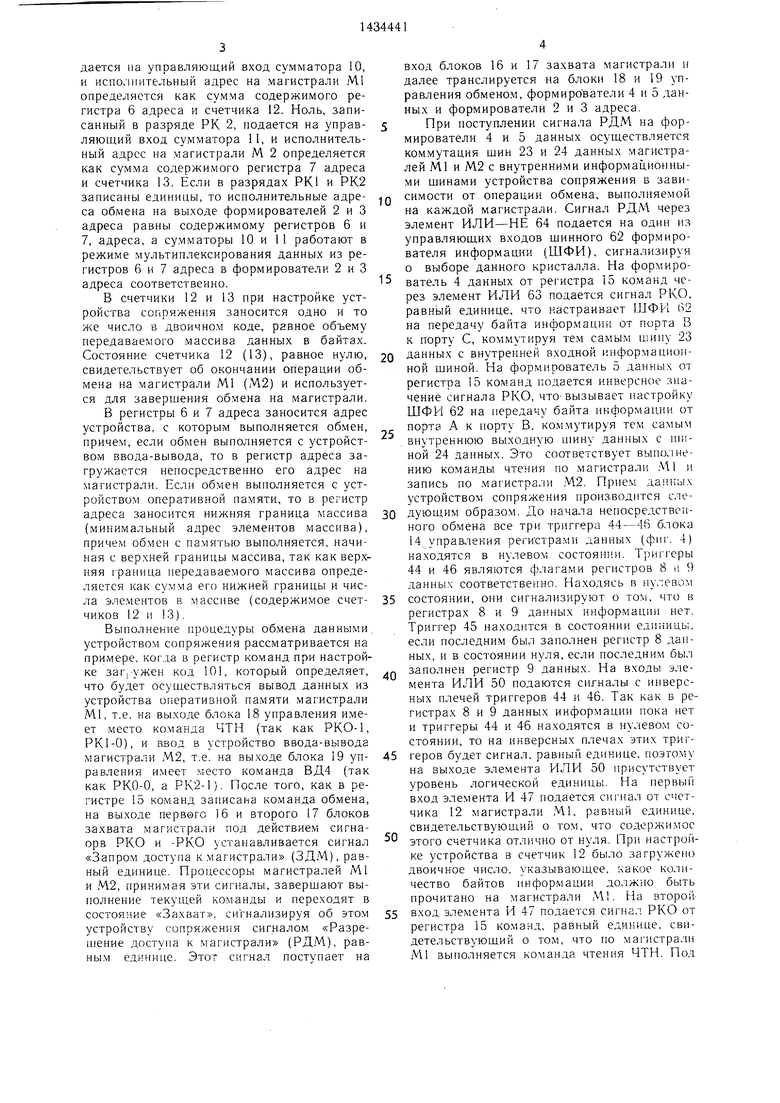

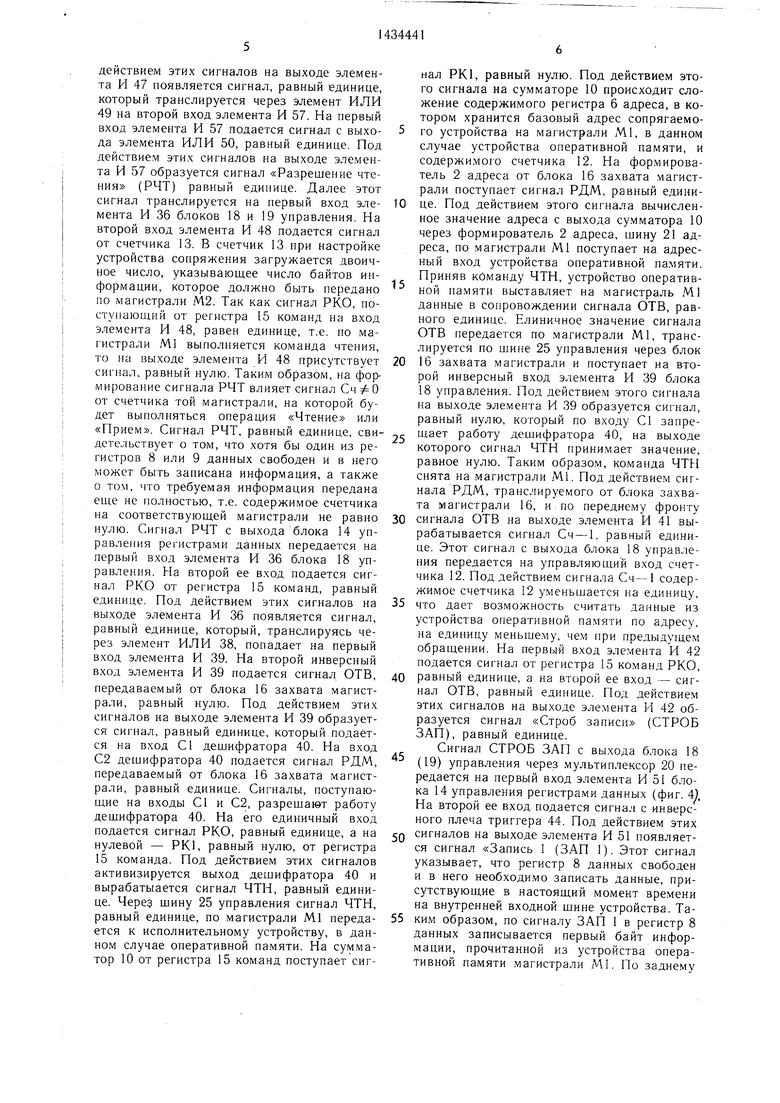

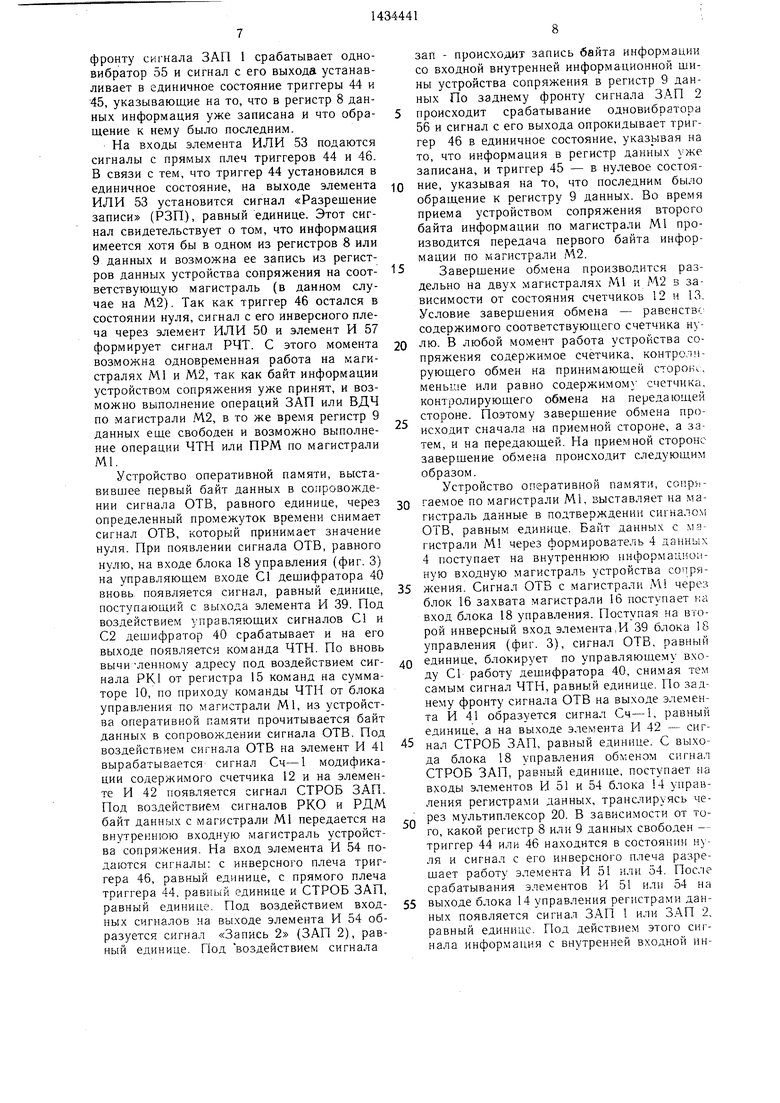

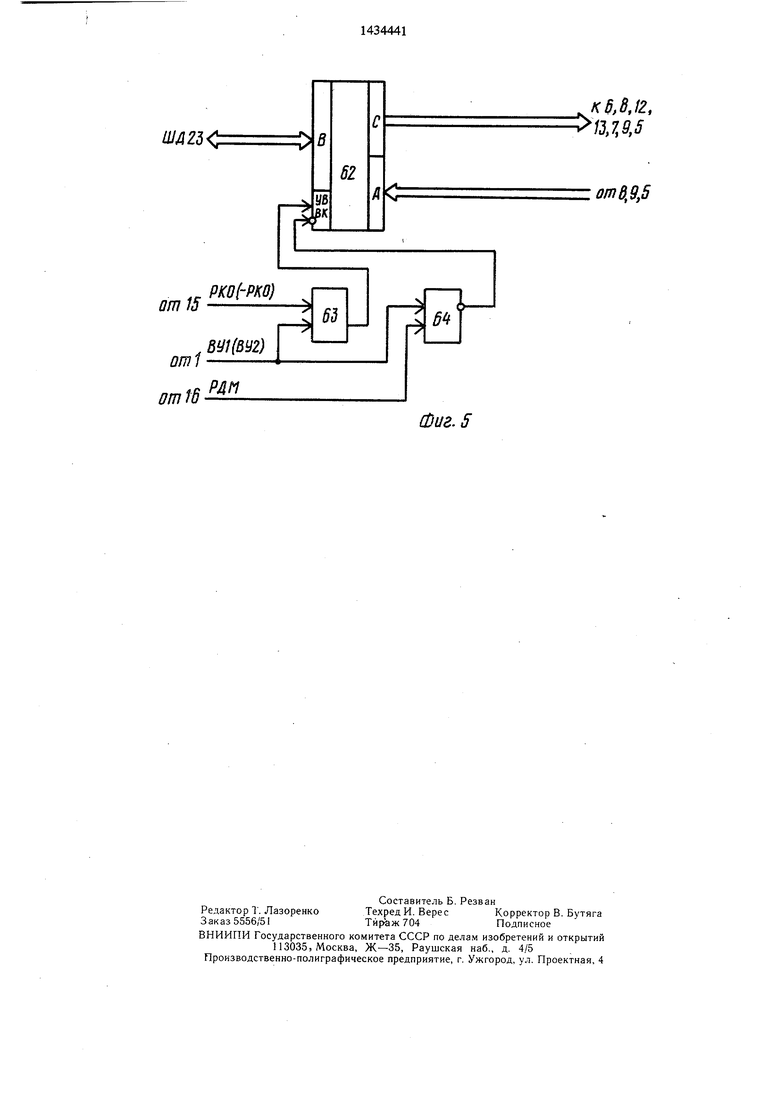

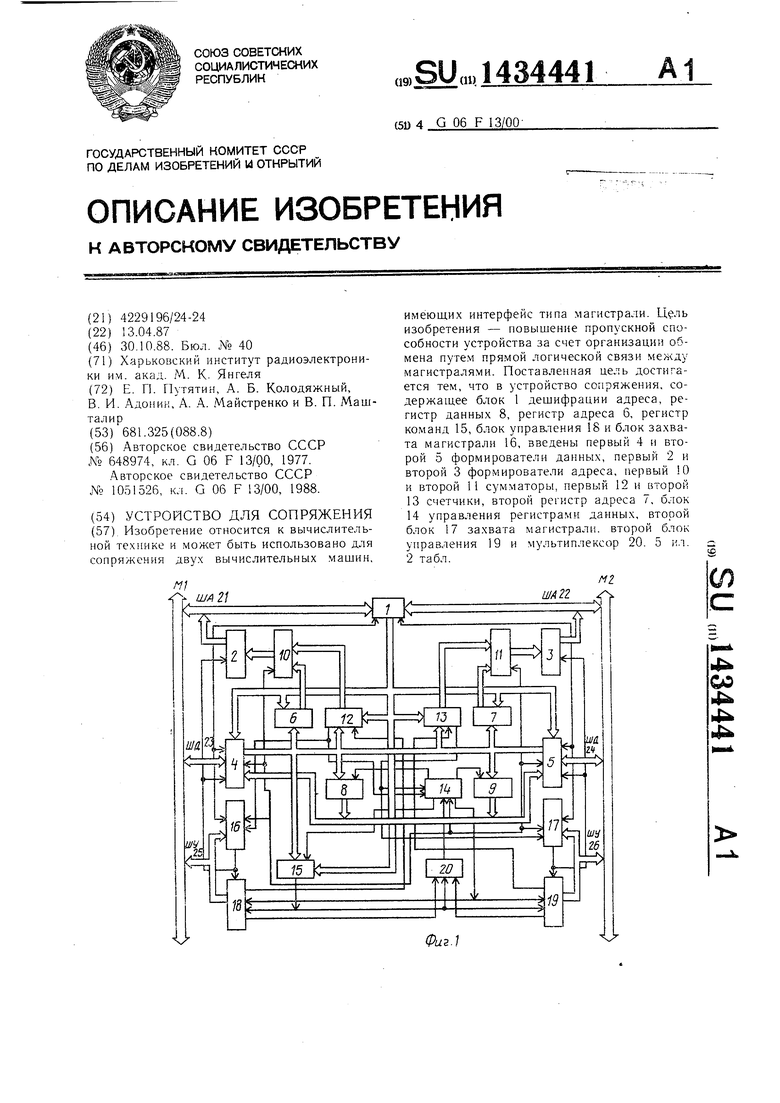

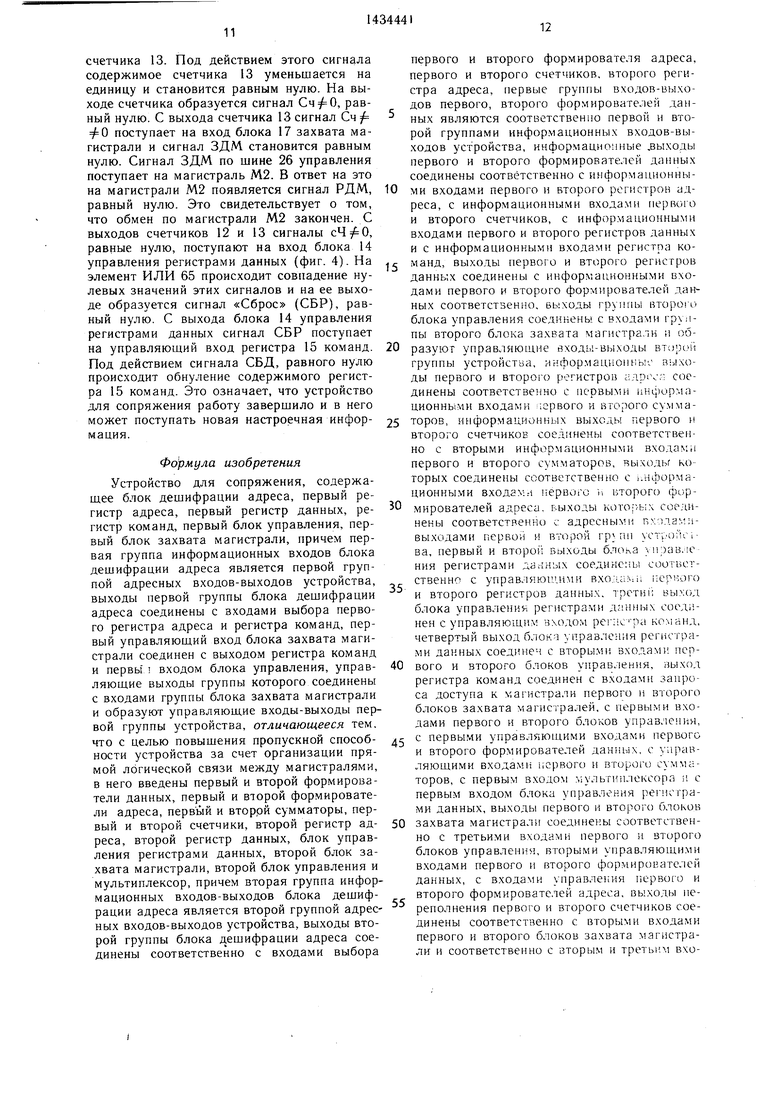

На фиг. .1 представлена структурная схема устройства; на фиг. 2 - функциональная схема блока дешифрации адреса; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема блока управления регистрами данных; на фиг. 5 - функциональная схема рователя данных.

Устройство (фиг. 1) содержит блок i дешифрации адреса, первый 2 и второй 3 формирователи адреса, первый 4 и второй 5 формирователи данных. Первый 6 и второй 7 регистры адреса, первый 8 и второй 9 pei-ист- ры данных, первый 10 и второй 11 сумматоры, первый 12 и второй 13 счетчики, блок 14 управления регистрами данных, регистр 15 команд, первый 16 и второй 17 блоки захвата магистрали, первый 18 и второй 19 блоки управления, мультиплексор 20, первую 21 и вторую 22 шины адреса, первую 23 и вторую 24 шины данных, первую 25 и вторую 26 шины управления (ШУ).

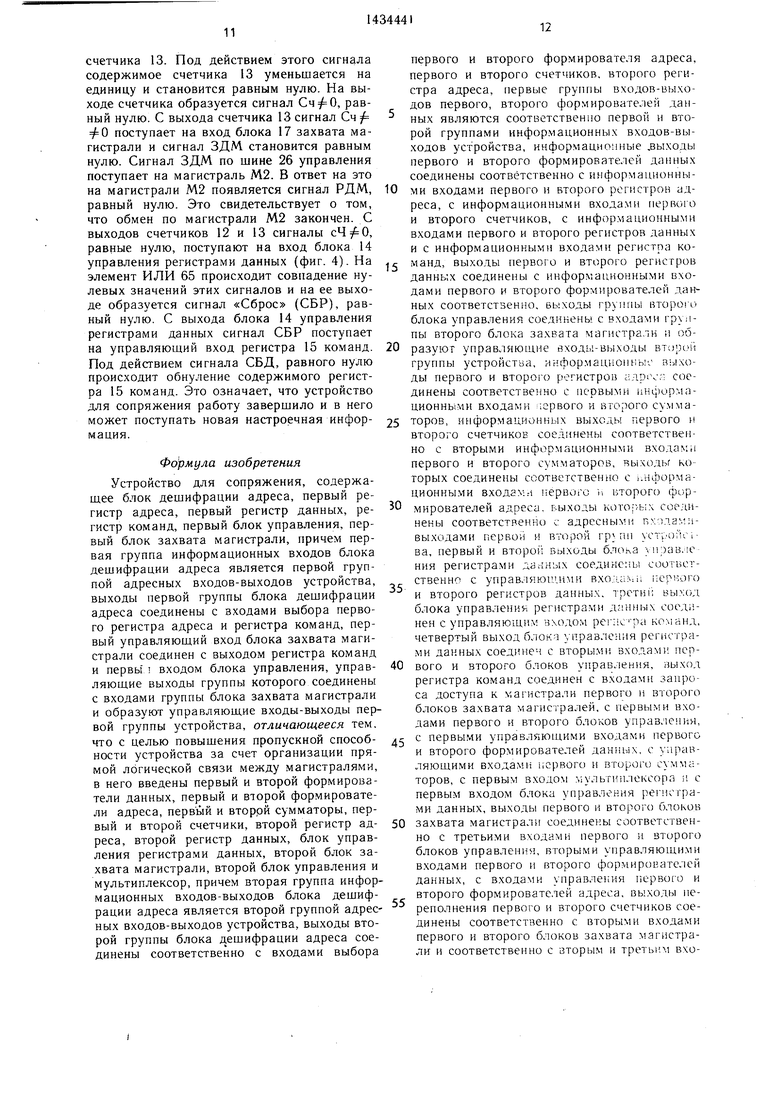

Блок 1 л1,ешифрации адреса (фиг. 2) содержит тервый 27 и второй 28 элементы за- дапяя адреса, первый 29 и второй 30 элементы сравнения, мультиплексор 31, дешифратор 32, элементы И 33 и 34.

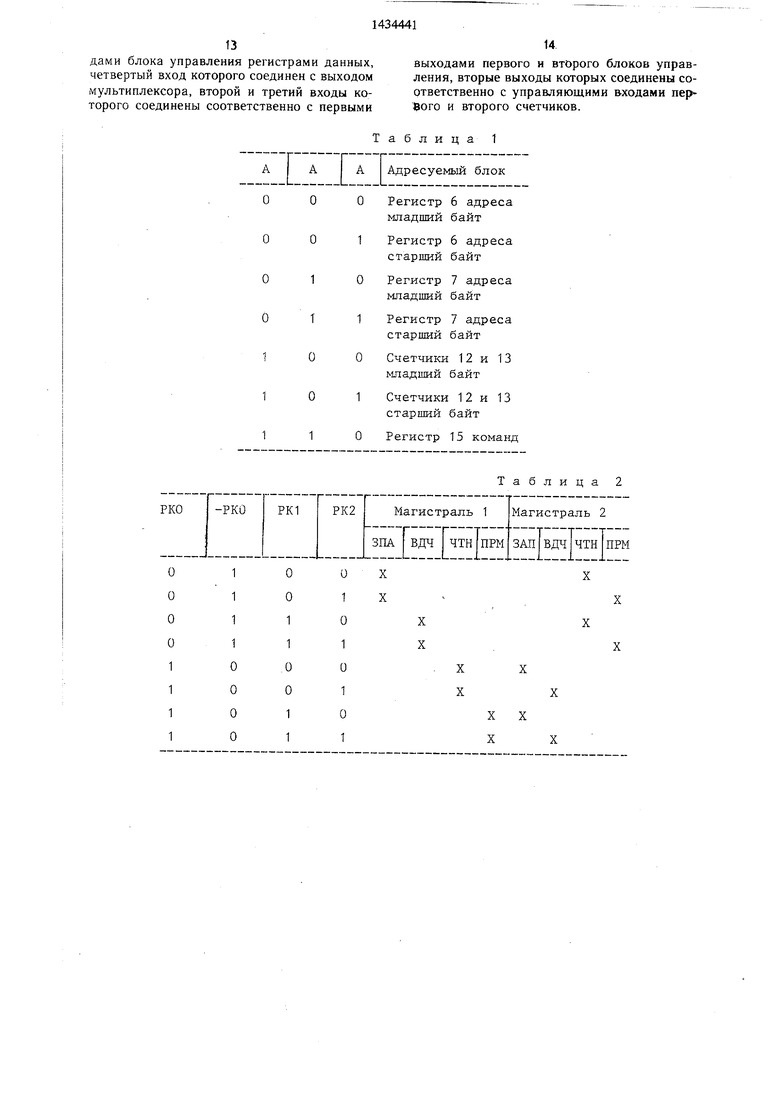

Блок 18 (9) управления (фиг. 3) содержит э..мент 35 задержки, элементы И 36 и 37, элемент ИЛИ 38, элемент И 39, дешифратор 40, элементы И 41, 42 и 43.

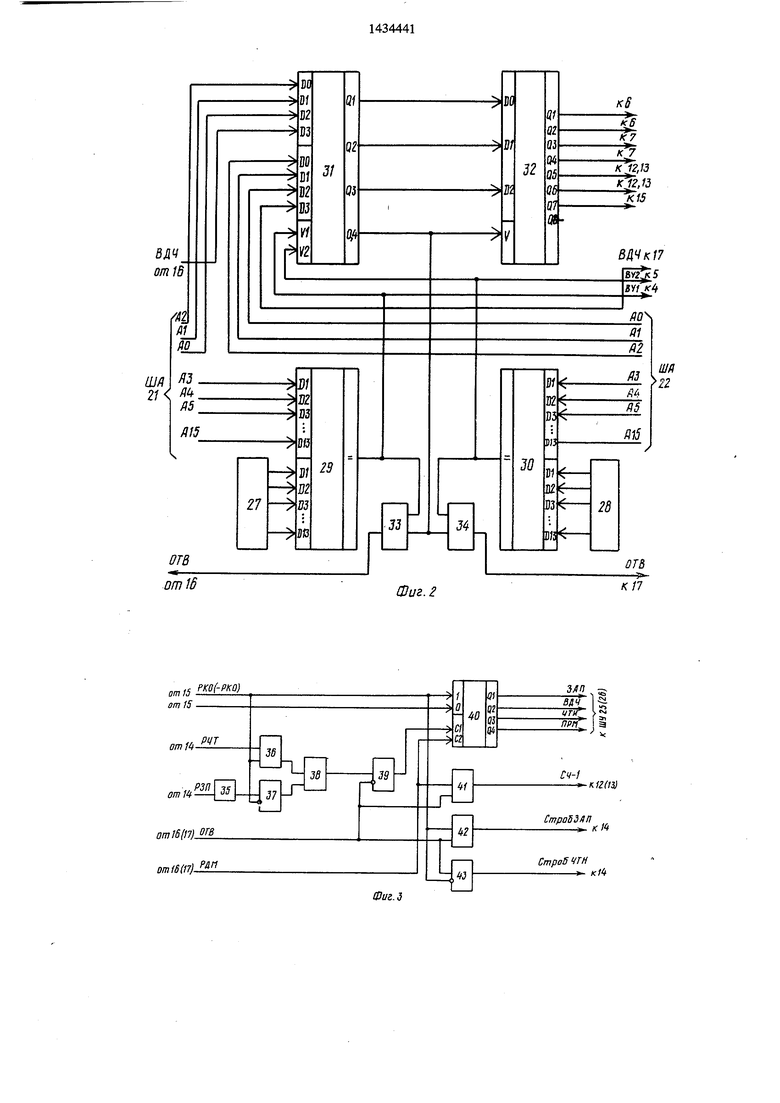

Блок 14 управления регистрами данных (фиг. 4) содержит первый 44, второй 45, третий, 46 триггеры, элементы И 47 к 48, элементы ИЛИ 49 и 50, элементы И 51 и 52 элемент ИЛИ 53, элемент И 54, первый 55 и второй 56 одновибраторы, элемент И 57, элементы 2И-2ИЛИ 58 и 59 элементы И 60 и 61.

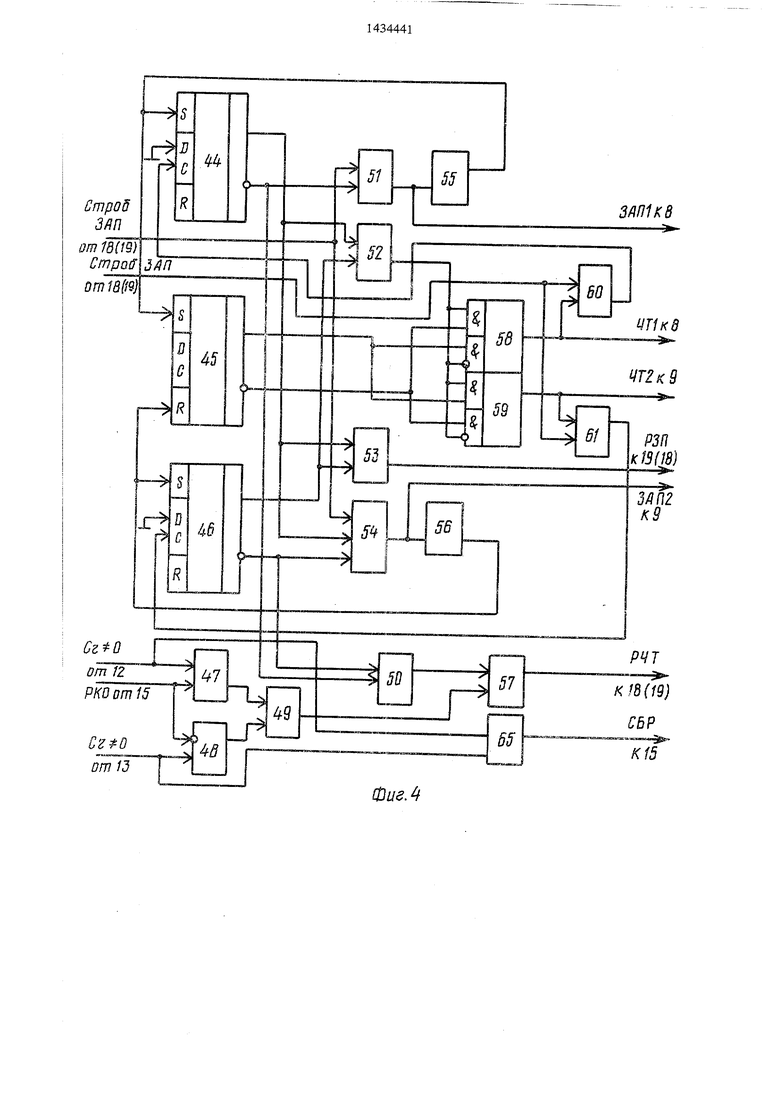

Формирователи данных 4 и 5 (фиг. 5) содержат шинный формирователь 62, элемент ИЛИ 63, элемент ИЛИ-НЕ 64.

Блоки 16 и 17 захвата магистралей реализованы по схеме прототипа.

Формирователи адреса 2 и 3 реализованы на схемах К589АП26, регистры адреса 6 и 7 и регистры данных 8 и 9 - на схемах К155ТМ8, сумматоры 10 и 11 - на схемах К155ИМЗ, счетчики 12 и 13 - на схемах К155ИЕ7, .мультиплексор 20 выполнен по схеме К155КП2.

Работа устройства состоит из двух стадий: стадии настройки и стадии обмена данными. Настройка устройства сопряжения может выполняться любым из процессоров

сопряженных магистралей и выполняется, ими одинаково. Один из процессоров сопрягаемых магистралей, например магистрали. Ml, выставляет на шине 21 адреса в разрядах А15-A3 базовый адрес устройства сопряжения, а в разрядах А2-АО - код внутренне го адресуемого блока в соответствии с табл. 1. На элементе дешифратора 1 схемы 29 сравнения происходит сравнение

базового адреса, поступившего по шине 21 адреса, с базовым адресом, поступившим со схемы задания 27 адреса. При совпадении, базового адреса на выходе схемы сравнения 29 (30) вырабатывается сигнал «Выбор устг ройства 1, Выбор устройства 2). Этот сигнал подается на вход формирователя данных 4 (5), вызывая срабатывание шинного формирователя 62 (фиг. 5). Сигнал с выхода схемы 29 (30) сравнения поступает также на управляюш.ий вход мультиплексо0 ра 31 - У (У2), разрешая прохождение кода внутреннего адресуемого блока, посту- паюшего по шине 21 (22) адреса на выход .мультиплексора. Сигнал «Выдача (ВД4), поступаюший по шине 25(26) управления,

5 сопровождает выставленный адрес по магистрали М (М2). Этот сигнал разрешает работу дешифратора 32, на выходе которого активизируется линия, соответствуюшая поступившему коду внутреннего блока, являясь сигналом занесения в выбранный блок.

0 По приходу этого сигнала на адресуе.мый блок в выбранном блоке происходит запоминание данных, которые присутствуют на входной информационной шипе 23. При совпадении сигналов «Выбор устройства 1 (Выбор устройства 2) и сигнала ВД4, на элемен5 те И 33 (34) вырабатывается сигна.- «Ответ который через блок 16 (17) захвата магистрали по (ШУ) 25 (26) сообщает процессору магистрали Ml (М2), что даяные устройством приняты. Для полной настройки

0 устройства сопряжения необходимо выполнить семь циклов обращения к устройству со стороны процессора.

В регистр команд по внутренней инфор- .мационной шине загружается информация, I- которая определяет характер обмена как на одной, так и па другой магистрали. Регистр имеет три разряда, значения которых указаны в табл. 2. Разряд РКО определяет н-аправление обмена между двумя интерфейсами. Разряды РК1 и F K2 характеризуют

0 устройства, подключенные к сопрялемым интерфейсам. Ноль в этих разрядах определяет обмен с устройством оперативной на- .мяти, а единица определяе об.мен с устройством ввода-вывода. Состояние этих разрядов влияет на способ формирования испол5 нительного адреса на сум.чаторах 0 и 11, а также определяет управляющие сигналь на выходе блоков 18 и 19 управления обме- но.м. Ноль, записанный в разряде РК1, подается на управляющий вход сумматора 10, и исполнительный адрес на магистрали Ml определяется как сумма содержимого регистра 6 адреса и счетчика 12. Ноль, записанный в разряде РК 2, подается на управ- 5 ляющий вход сумматора 11, и исполнительный адрес на магистрали М 2 определяется как сумма содержимого регистра 7 адреса и счетчика 13. Если в разрядах РК1 и РК2 записаны единицы, то исполнительные адреса обмена на выходе формирователей 2 и 3 адреса равны содержимому регистров 6 и 7, адреса, а сумматоры 10 и 11 работают в режиме мультиплексирования данных из регистров 6 и 7 адреса в формирователи 2 и 3 адреса соответственно.

В счетчики 12 и 13 при настройке устройства сопряжения заносится одно и то же число в двоичном коде, равное объему передаваемого массива данных в байтах. Состояние счетчика 12 (13), равное нулю, свидетельствует об окончании операции обмена на магистрали Ml (М2) и используется для завершения обмена на магистрали.

В регистры 6 и 7 адреса заносится адрес устройства, с которым выполняется обмен, причем, если обмен выполняется с устройством ввода-вывода, то в регистр адреса загружается непосредственно его адрес на магистрали. Если обмен выполняется с уст- ройство.м оперативной памяти, то в регистр

вход блоков 16 и 1/ захвата магистрали н далее транслируется на блоки 18 и 19 управления обменом, формирователи 4 и 5 данных и формирователи 2 и 3 адреса.

При поступлении сигнала РДМ на формирователи 4 и 5 данных осуществляется коммутация щин 23 и 24 данных магистралей Ml и М2 с внутренними информационными щинами устройства сопряжения в зави Q симости от операции обмена, выполняемой на каждой магистрали. Сигнал РДМ через элемент ИЛИ-НЕ 64 подается на один из управляющих входов щинного 62 формирователя информации (ШФИ), сигнализируя о выборе данного кристалла. На формиро15 ватель 4 данных от регистра 15 команд через элемент ИЛИ 63 подается сигнал РКО, равный единице, что настраивает ШФИ 62 на передачу байта информации от порта В к порту С, коммутируя тем самым шину 23

20 данных с внутренней входной информационной щиной. На формирователь 5 данных от регистра 15 команд подается инверсное значение сигнала РКО, что-вызывает настройку ШФИ 62 на 11ередачу байта информации от порта А к порту В, ком.мутируя тем самым внутреннюю выходную тину данных с тиной 24 данных. Это соответствует вьики нению команды чтения по магистрали Ml и запись по магистрали .N12. Прием данных устройством сопряжения производится сле25

адреса заносится нижняя граница массива ЗО дующим образом. До начала непосредствеи(минимальный адрес элементов массива), причем обмен с памятью выполняется, начиная с верхней границы массива, так как верхняя 1-раница передаваемого массива определяется как сумма его нижней границы и числа эле.ментов в массиве (содержимое счетчиков 12 и 13).

Выполнение процедуры обмена данными, устройством сопряжения рассматривается на примере, ког.да в регистр команд при настройке загружен код 101, который определяет, что будет осуществляться вывод данных из устройства оперативной памяти магистрали Ml, т.е. на выходе блока 18 управления и.ме- ет место команда ЧТН (так как РКО-1, РК1-0), и ввод в устройство ввода-вывода

35

40

ного обмена все три триггера 44-46 блока 14 управления регистрами данных (фн1 . 4) находятся в нулевом состоянии. Триггеры 44 и 46 являются флагами регистров 8 и 9 данных соответственно. Находясь в нулевом состоянии, они сигнализируют о том, что в регистрах 8 и 9 данных информации нет. Триггер 45 находится в состоянии единицы, если последним был заполнен регистр 8 данных, и в состоянии нуля, если последним был заполнен регистр 9 данных. На входы элемента ИЛИ 50 подаются сигналы с инверсных плечей триггеров 44 и 46. Так как в регистрах 8 и 9 данных информации пока нет и триггеры 44 и 46 находятся в нулевом состоянии, то на инверсных плечах этих тригмагистрали М2, т.е. на выходе блока 19 уп- 45 геров будет сигнал, равный единице, поэтому равления имеет место команда ВД4 (такна выходе элемента ИЛИ 50 присутствует

На nepBbiii

как РКО-0, а РК2-1). После того, как в регистре 15 команд записана команда обмена, на выходе первего 16 и второго 17 блоков захвата магистрали под действием сигна- орв РКО и -РКО устанавливается сигнал «Запром доступа к магистрали (ЗДМ), равный единице. Процессоры магистралей Ml и М2, прини.мая эти сигналы, заверщают выполнение текущей команды и переходят в состояние «Захват, сигнализируя об этом устройству сопряжения сигналом «Разрешение доступа к магистрали (РДМ), рав- ны.м единице. Этот сигнал поступает на

уровень логической единицы, вход элемента И 47 подается сигнал от счетчика 12 магистрали Ml, равный единице, свидетельствующий о том, что содержимое

50 этого счетчика отлично от нуля. При настройке устройства в счетчик 12 было загружено двоичное число, указывающее, какое количество байтов информации должно быть прочитано на магистрали Ml. На второй

55 вход элемента И 47 подается сигнал РКО от регистра 15 команд, равный единице, свидетельствующий о том, что по магистра.ли Ml выполняется команда чтения ЧТН. Под

вход блоков 16 и 1/ захвата магистрали н далее транслируется на блоки 18 и 19 управления обменом, формирователи 4 и 5 данных и формирователи 2 и 3 адреса.

При поступлении сигнала РДМ на формирователи 4 и 5 данных осуществляется коммутация щин 23 и 24 данных магистралей Ml и М2 с внутренними информационными щинами устройства сопряжения в завиQ симости от операции обмена, выполняемой на каждой магистрали. Сигнал РДМ через элемент ИЛИ-НЕ 64 подается на один из управляющих входов щинного 62 формирователя информации (ШФИ), сигнализируя о выборе данного кристалла. На формиро5 ватель 4 данных от регистра 15 команд через элемент ИЛИ 63 подается сигнал РКО, равный единице, что настраивает ШФИ 62 на передачу байта информации от порта В к порту С, коммутируя тем самым шину 23

0 данных с внутренней входной информационной щиной. На формирователь 5 данных от регистра 15 команд подается инверсное значение сигнала РКО, что-вызывает настройку ШФИ 62 на 11ередачу байта информации от порта А к порту В, ком.мутируя тем самым внутреннюю выходную тину данных с тиной 24 данных. Это соответствует вьики нению команды чтения по магистрали Ml и запись по магистрали .N12. Прием данных устройством сопряжения производится сле5

5

0

ного обмена все три триггера 44-46 блока 14 управления регистрами данных (фн1 . 4) находятся в нулевом состоянии. Триггеры 44 и 46 являются флагами регистров 8 и 9 данных соответственно. Находясь в нулевом состоянии, они сигнализируют о том, что в регистрах 8 и 9 данных информации нет. Триггер 45 находится в состоянии единицы, если последним был заполнен регистр 8 данных, и в состоянии нуля, если последним был заполнен регистр 9 данных. На входы элемента ИЛИ 50 подаются сигналы с инверсных плечей триггеров 44 и 46. Так как в регистрах 8 и 9 данных информации пока нет и триггеры 44 и 46 находятся в нулевом состоянии, то на инверсных плечах этих тригНа nepBbiii

уровень логической единицы, вход элемента И 47 подается сигнал от счетчика 12 магистрали Ml, равный единице, свидетельствующий о том, что содержимое

этого счетчика отлично от нуля. При настройке устройства в счетчик 12 было загружено двоичное число, указывающее, какое количество байтов информации должно быть прочитано на магистрали Ml. На второй

вход элемента И 47 подается сигнал РКО от регистра 15 команд, равный единице, свидетельствующий о том, что по магистра.ли Ml выполняется команда чтения ЧТН. Под

действием этих сигналов на выходе элемента И 47 появляется сигнал, равный единице, который транслируется через элемент ИЛИ 49 на второй вход элемента И 57. На первый вход элемента И 57 подается сигнал с выхода элемента ИЛИ 50, равный единице. Под действием этих сигналов на выходе элемента И 57 образуется сигнал «Разрешение чтения (РЧТ) равный единице. Далее этот сигнал транслируется на первый вход элемента И 36 блоков 18 и 19 управления. На второй вход элемента И 48 подается сигнал от счетчика 13. В счетчик 13 при настройке устройства сопряжения загружается двоичное число, указывающее число байтов информации, которое должно быть передано по магистрали М2. Так как сигнал РКО, поступающий от регистра 15 команд на вход элемента И 48, равен единице, т.е. по магистрали Ml выпо.тняется команда чтения, то па выходе элемента И 48 присутствует сигнал, равный нулю. Таким образом, на формирование сигнала РЧТ влияет сигнал от счетчика той магистрали, на которой будет выполняться операция «Чтение или «Прием. Сигнал РЧТ, равный единице, свидетельствует о том, что хотя бы один из регистров 8 или 9 данных свободен и в него может быть записана информация, а также о том, что требуемая информация передана еще не полностью, т.е. содержимое счетчика на соответствующей магистрали не равно нулю. Сигнал РЧТ с выхода блока 14 управления ре1 истрами данных передается на первый вход элемента И 36 блока 18 управления. На второй ее вход подается сигнал РКО от регистра 15 команд, равный единице. Под действием этих сигналов на выходе элемента И 36 появляется сигнал, равный единице, который, транслируясь через элемент ИЛИ 38, попадает на первый вход элемента И 39. На второй инверсный вход элемента И 39 подается сигнал, ОТВ, передаваемый от блока 16 захвата магистрали, равный нулю. Под действием этих сигналов на выходе элемента И 39 образуется сигнал, равный единице, который подается на вход С1 дешифратора 40. На вход С2 дешифратора 40 подается сигнал РДМ, передаваемый от блока 16 захвата магистрали, равный единице. Сигналы, поступающие на входы С1 и С2, разрешают работу дешифратора 40. На его единичный вход подается сигнал РКО, равный единице, а на нулевой - РК1, равный нулю, от регистра 15 команда. Под действием этих сигналов активизируется выход дешифратора 40 и вырабатыается сигнал ЧТН, равный единице. Через шину 25 управления сигнал ЧТН, равный единице, по магистрали Ml передается к исполнительному устройству, в данном случае оперативной памяти. На сумматор 10 от регистра 15 команд поступает сигнал РК1, равный нулю. Под действием этого сигнала на сумматоре 10 происходит сложение содержимого регистра 6 адреса, в котором хранится базовый адрес сопрягаемого устройства на магистрали Ml, в данном случае устройства оперативной памяти, и содержимого счетчика 12. На формирователь 2 адреса от блока 16 захвата магистрали поступает сигнал РДМ, равный единице. Под действием этого сигнала вычисленное значение адреса с выхода су.мматора 10 через формирователь 2 адреса, щину 21 адреса, по магистрали Ml поступает на адресный вход устройства оперативной памяти. ПриняЕ команду ЧТН, устройство оперативной памяти выставляет на магистраль Ml данные в сопровождении сигнала ОТВ, равного единице. Елиничное значение сигнала ОТВ передается по магистрали Ml, транслируется по шине 25 управления через блок

16 захвата магистрали и поступает на второй инверсный вход элемента И 39 блока 18 управления. Под действием этого сигнала на выходе элемента И 39 образуется сигнал, равный нулю, который по входу С1 запрещает работу дешифратора 40, на выходе которого сигнал ЧТН принимает значение, равное нулю. Таким образом, команда ЧТН снята на магистрали Ml. Под действием сигнала РДМ, транслируемого от блока захвата магистрали 16, и. по переднему фронту

сигнала ОТВ на выходе элемента И 41 вырабатывается сигнал Сч-1, равный единице. Этот сигнал с выхода блока 18 управления передается на управляющий вход счетчика 12. Под действием сигнала Сч-1 содержимое счетчика 12 уменьщается на единицу,

что дает возможность считать данные из устройства оперативной памяти по адресу, на единицу меньшему, чем при предыдущем обращении. На первый вход элемента И 42 подается сигнал от регистра 15 команд РКО,

равный единице, а на второй ее вход - сигнал ОТВ, равный единице. Под действием этих сигналов на выходе элемента И 42 образуется сигнал «Строб записи (СТРОБ ЗАП), равный единице.

Сигнал СТРОБ ЗАП с выхода блока 18

(19) управления через мультиплексор 20 передается на первый вход элемента И 51 блока 14 управления регистрами данных (фиг. 4) На второй ее вход подается сигнал с инверсного плеча триггера 44. Под действием этих

сигналов на выходе элемента И 51 появляется сигнал «Запись 1 (ЗАП 1). Этот сигнал указывает, что регистр 8 данных свободен и в него необходимо записать данные, присутствующие в настоящий момент времени на внутренней входной шине устройства. ТаКИМ образом, по сигналу ЗАП 1 в регистр 8 данных записывается первый байт информации, прочитанной из устройства оперативной памяти магистрали Ml. По заднему

фронту сигнала ЗАП 1 срабатывает одно- вибратор 55 и сигнал с его выхода устанавливает в единичное состояние триггеры 44 и 45, указывающие на то, что в регистр 8 данных информация уже записана и что обращение к нему было последним.

На входы элемента ИЛИ 53 подаются сигналы с прямых плеч триггеров 44 и 46.

8связи с тем, что триггер 44 установился в единичное состояние, на выходе элемента ИЛИ 53 установится сигнал «Разрешение записи (РЗП), равный единице. Этот сигнал свидетельствует о том, что информация имеется хотя бы в одном из регистров 8 или

9данных и возможна ее запись из регистров данных устройства сопряжения на соответствующую магистраль (в данном случае на М2). Так как триггер 46 остался в состоянии нуля, сигнал с его инверсного плеча через элемент ИЛИ 50 и элемент И 57 формирует сигнал РЧТ. С этого момента возможна одновременная работа на магистралях Ml и М2, так как байт информации устройством сопряжения уже принят, и возможно выполнение операций ЗАП или ВДЧ по магистрали М2, в то же время регистр 9 данных еще свободен и возможно выполнение операции ЧТН или ПРМ по магистрали Ml.

Устройство оперативной памяти, выставившее первый байт данных в сопровождении сигнала ОТВ, равного единице, через определенный промежуток времени снимает сигнал ОТВ, который принимает значение нуля. При появлении сигнала ОТВ, равного нулю, на входе блока 18 управления (фиг. 3) на управляющем входе С1 дешифратора 40 вновь появляется сигнал, равный единице, поступающий с выхода элемента И 39. Под воздействием управляющих сигналов С1 и С2 дешифратор 40 срабатывает и на его выходе появляется команда ЧТН. По вновь вычи ленному адресу под воздействием сигнала РК1 от регистра 15 команд на сумматоре 10, по приходу команды ЧТН от блока управления по магистрали Ml, из устройства оперативной памяти прочитывается байт данных в сопрово.ждении сигнала ОТВ. Под воздействием сигнала ОТВ на элемент И 41 вырабатывается сигнал Сч-1 модификации содержимого счетчика 12 и на элементе И 42 появляется сигнал СТРОБ ЗАП. Под воздействием сигналов РКО и РДМ байт данных с магистрали Ml передается на внутреннюю входную магистраль устройства сопряжения. На вход элемента И 54 подаются сигналы: с инверсного плеча триггера 46, равный единице, с прямого плеча триггера 44, равный единице и СТРОБ ЗАП, равный единице. Под воздействием входных сигналов на элемента И 54 образуется сигнал «Запись 2 (ЗАП 2), равный единице. Под воздействием сигнала

5

зап - происходит запись байта информации со входной внутренней информационной щи- ны устройства сопряжения в регистр 9 данных По заднему фронту сигнала ЗА.П 2 происходит срабатывание одновибратора 56 и сигнал с его выхода опрокидывает триггер 46 в единичное состояние, указьшая на то, что информация в регистр данных уже записана, и триггер 45 - в нулевое состояO ние, указывая на то, что последним было обращение к регистру 9 данных. Во время приема устройством сопряжения второго байта информации по магистрали Ml производится передача первого байта информации по магистрали ..

5Завершение обмена производится раздельно на двух магистралях Ml и М2 в зависимости от состояния счетчиков 12 и 13. Условие завершения обмена - равенстве- содержимого соответствующего счетчика ну0 лю. В любой момент работа устройства сопряжения содержимое счетчика, контро. рующего обмен на принимающей сторон, меньше или равно содержимому счетчика, контролирующего обмена на передающей стороне. Поэтому завершение обмена происходит сначала на приемной стороне, а затем, и на передающей. На приемной сторонс завершение обмена происходит следующим образом.

Устройство оперативной памяти, conpji0 гаемое по магистрали Ml, выставляет на магистраль данные в подтверждении сигналом ОТВ, равным единице. Байт данных с магистрали Ml через фор.мирователь 4 данных 4 поступает на внутреннюю информацном- ную входную магистраль устройства сочря5 жения. Сигнал ОТВ с магистрали М через блок 16 захвата магистрали 16 поступает ка вход блока 18 управления. Поступая на второй инверсный вход элемента,И 39 блока 18 управления (фиг. 3), сигнал ОТВ, равный

0 единице, блокирует по управляющему входу С1 работу дешифратора 40, снимая тем самым сигнал ЧТН, равный единице. По заднему фронту сигнала ОТВ на выходе элемента И 41 образуется сигнал Сч-1, равный единице, а на выходе элемента И 42 - сиг5 нал СТРОБ ЗАП, равный единице. С выхода блока 18 управления обменом сигнал СТРОБ ЗАП, равный единице, поступает на входы элементов И 51 и 54 блока 4 управления регистрами данных, транслируясь че рез мультиплексор 20. В зависимости от того, какой регистр 8 или 9 данных свободен - триггер 44 или 46 находится в состоянпи нуля и сигнал с его инверсного плеча разрешает работу элемента И 51 или 54. После срабатывания элементов И 51 или 54 на

5 выходе блока 14 управления регистрами данных появляется сигнал ЗАП 1 или З.А.П 2, равный единице. Под действием этого сигнала информация с внутренней входной информационной магистрали устройства записывается в соответствующий регистр- данных 8 или 9. Таким образом, байт информации принимается устройством сопряжения. С выхода блока 18 управления сигнал Сч- 1, равный единице, подается на управляющий вход счетчика 12. Под действием этого сигнала содержимое счетчика 12 уменьшается на единицу и, так как принятый байт был последним, становится равным нулю: На выходе счетчика 12 сигнал изменяет свое значение с единичного на нулевое. С выхода счетчика 12 сигнала поступает на вход блока 14 управления регистрами данных и на вход блока 16 захвата магистрали. В блоке 14 управления регистрами данных (фиг. 4) сигнал , равный нулю, подается на первый вход эле.мента И 47. Под действием этого сигнала элемент И 47 блокируется и на его выходе образуется сигнал, равный нулю, который, транслируясь через элемепт ИЛИ 49, поступает на второй вход элемента И 57. Под действием этого сигнала элемент И 57 блокируется и на его выходе образуется сигнал РЧТ, равный нулю. С выхода блока 14 управления регистрами данных сигнал РЧТ, равный нулю, подается на вход блока 18 управления (фиг. 3). Поступая на первый вход элемента И 36, сигнал РЧТ, равный нулю, блокирует его работу и на его выходе образуется сигнал, равный нулю, который, транслируясь через элемент ИЛИ 38, поступает на первый прямой вход элемента И 39. Под действием этого сигнала на выходе элемента И 39 образуется сигнал, равный нулю, который, поступая на управляющий вход С1 дещифратора 40, запрещает его работу. Теперь сигнал ЧТН на выходе дептфратора 40 при изменении сигнала ОТВ не становится равным единице. С выхода счетчика 12 сигнал Сч 0, равный нулю, поступает на вход блока ,16 захвата .магистрали. Под действием этого сигнала блоком 16 захвата магистрали снимается сигнал ЗДМ, равный единице, через щину 25 управления по магистрали Ml. На магистрали Ml появ- ляется сигнал РДМ, равный нулю. Этот сигнал сигнализирует о том, что обмен информацией по магистрали Ml закончен.

Завершение обмена на передающей стороне происходит следующим образом.

В блоке 14 управления регистрами данных (фиг, 4) на входы элемента ИЛИ 53 подаются сигналы с прямых плеч триггеров 44 и 46, а на ее выходе вырабатывается сигнал РЗП. Таким образом, сигнал РЗП на выходе элемента ИЛИ 53 равен единице тогда, когда в единичном состоянии находится хотя бы один из указанных триггеров, а это означает, что хотя бы в одном из регистров В или 9 данных имеется байт информации, еще не считанный из устройства.

0

5

0

5

0

5

0

5

0

5

С выхода блока 14 управления регистрами данных сигнал РЗП, равный единице, поступает на вход блока 19 управления (фиг. 3). При наличии сигналов - РЗП, равного единице, ОТВ, равного нулю, РДМ, равного единице, по управляющим входам С1 и С2 раз- рещается работа дещифратора 40. Под действием сигналов - РКО, равного нулю, и РК2, равного единице, на.выходе дещифратора 40 образуется сигнал ВДЧ, равный единице. С выхода блока 19 управления через щину 26 управления сигнал ВДЧ, равный единице, поступает на магистраль М2. Внешнее устройство, сопрягаемое по магистрали М2, приняв сигнал ВДЧ, равный единице, осуществляет прием байта информации и подтверждает это сигналом ОТВ, равным единице. Транслируясь через магистраль Ml, блок 17 захвата магистрали, этот сигнал поступает на вход блока 19 управления (фиг. 3 Этот сигнал, поступая на второй инверсный вход элемента И 39, вырабатывает на ее выходе си.гнал, равный нулю, который блокирует по входу С1 работу дешифратора 40. На выходе дешифратора 40 сигнал ВДЧ принимает значение нуля. Под действием сигналов - ОТВ, равного единице, и РКО, равного нулю, на выходе элемента И 43 вырабатывается сигнал СТРОБ ЧТН, равный единице. Под действием сигнала РДМ, равного единице, и по заднему фронту сигнала ОТВ на выходе элемента И 41 образуется сигнал сЧ-1, равный единице. С выхода блока 19 управления сигнал СТРОБ ЧТН передается на вход блока 14 управления регистрами данных (фиг. 4). На элементе И 60 или 61 происходит совпадение сигналов СТРОБ ЧТН, равного единице, и сигнала ТЧ1 или ЧТ2 соответственно, равного единице, в зависимости от того, из какого регистра 8 или 9 данных был прочитан последний байт данных, и сигнал с выхода этого элемента, равный единице, поступает на синхронизирующий вход С триггера, устанавливая его в нулевое состояние. Так как оба триггера 44 и 46 находятся в состоянии нуля, на входы элемента ИЛИ 53 подаются сигналы с их прямых плеч, равные нулю. На выходе этого элемента образуется сигнал РЗП, равный нулю. С выхода блока 14 управления регистрами данных сигнал РЗП поступает на вход блока 19 управления (фиг. 3). Через линию 35 задержки сигнал РЗП, равный нулю, поступает на первый вход элемента И 37, образуя на его выходе сигнал, равный нулю. С выхода элемента И 37 нулевой сигнал транслируется через элемент ИЛИ 38 и поступает на первый вход элемента И 39, блокируя его работу. С этого момента выдача сигнала ВДЧ, равного единице, с выхода дещифратора 40 запрещена. С выхода блока 19 управления сигнал Сч-1, равный единице, поступает на управляющий вход

счетчика 13. Под действием этого сигнала содержимое счетчика 13 уменьшается на единицу и становится равным нулю. На выходе счетчика образуется сигнал , равный нулю. С выхода счетчика 13 сигнал Сч 0 поступает на вход блока 17 захвата магистрали и сигнал ЗДМ становится равным нулю. Сигнал ЗДМ по шине 26 управления поступает на магистраль М2. В ответ на это на магистрали М2 появляется сигнал РДМ, равный нулю. Это свидетельствует о том, что обмен по магистрали М2 закончен. С выходов счетчиков 12 и 13 сигналы , равные нулю, поступают на вход блока 14 управления регистрами данных (фиг. 4). На элемент ИЛИ 65 происходит совпадение нулевых значений этих сигналов и на ее выходе образуется сигнал «Сброс (СБР), равный нулю. С выхода блока 14 управления регистрами данных сигнал СБР поступает на управляющий вход регистра 15 команд. Под действием сигнала СБД, равного нулю происходит обнуление содержимого регистра 15 команд. Это означает, что устройство для сопряжения работу завершило и в него может поступать новая настроечная инфор- мация.

Фо рмула изобретения

Устройство для сопряжения, содержа- ш,ее блок дешифрации адреса, первый регистр адреса, первый регистр данных, ре- гистр команд, первый блок управления, первый блок захвата магистрали, причем первая группа информационных входов блока дешифрации адреса является первой группой адресных входов-выходов устройства, выходы первой группы блока дешифрации адреса соединены с входами выбора первого регистра адреса и регистра команд, первый управляющий вход блока захвата магистрали соединен с выходом регистра команд и первь входом блока управления, управ- ляюшие выходы группы которого соединены с входами группы блока захвата магистрали и образуют управляющие входы-выходы первой группы устройства, отличающееся тем. что с целью повышения пропускной способ- ности устройства за счет организации прямой логической связи между магистралями, в него введены первый и второй формирователи данных, первый и второй формирователи адреса, первьш и вторрй сумматоры, первый и второй счетчики, второй регистр ад- реса, второй регистр данных, блок управления регистрами данных, второй блок захвата магистрали, второй блок управления и мультиплексор, причем вторая группа информационных входов-выходов блока дешифрации адреса является второй группой адресных входов-выходов устройства, выходы второй группы блока д ешифрации адреса соединены соответственно с входами выбора

первого и второго формирователя адреса, первого и второго счетчиков, второго регистра адреса, первые группы входов-выходов первого, второго формирователей данных являются соответственно первой и второй группами информационных входов-выходов устройства, информационные выходы первого и второго формирователей данных соединены соответственно с информационными входами первого и второго регистрон адреса, с информационными входами первого и второго счетчиков, с информационными входами первого и второго регистров данных и с информационными входами регистра команд, выходы первого и второго регистров данных соединены с информационными входами первого и второго форм1 рователей данных соответственно, выходы группы второго блока управления соединены с входами rpvii- пы второго блока захвата магистрали п образуют управляющие входы-выходы второ и группы устройства, информационны;- выходы первого и BTOpoi O регистров алО Ч ;; соединены соответственно с первыми инсрорма- ционными входами первого и второго сумматоров, информационных выходы первого и второго счетчиков соединены соответственно с вторыми информационными BxoAaNui первого и второго сумматоров, выходы которых соединены соответственно с ьнформа- ционны.ми входам.-i первого и второго формирователей адреса, выходы котО;Н;1х соединены соответственно с адресными nxon.aN-u- выходами первой и второй гр пи устрой - за, первый и второГ; выходы бло.ка уирав. С ния регистрами ладных соединсмы соответственно с управляющими Bxo.;i. первого и второго регистров данных, третиii выход блока управления регистрами данных нен с управляющим входом регис ра команд, четвертый выход блока управления регистрами данных соединен с вторы.ми входами первого и второго блоков управления, выход регистра команд соединен с входами запроса доступа к магистрали первого и второго блоков захвата магистралей, с первыми входами первого и второго блоков управления, с первыми управляющими входами первого и второго формирователей данных, с y.ipaB- ляющими входами первого и второго сумматоров, с первым входом мультинлексора и с первым входом блока управления решсгра- ми данных, выходы первого и второго Гхтоков захвата магистрали соединены соответственно с третьими входами первого и второго блоков управлен11Н, вторыми управляющими входами первого и второго формирователей данных, с входами управления г.ервого и второго формирователей адреса, выходы переполнения первого и второго счетчиков соединены соответственно с вторыми входами первого и второго блоков захвата магистрали и соответственно с вторым и третьим вхо13

14

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

, Изобретение относится к вычислительной технике и может быть использовано для сопряжения дву.х вычислительных машин. имеющих интерфейс типа магистрали. Цель изобретения - повышение пропускной способности устройства за счет организации обмена путе.м пря.мой логической связи между магистралями. Поставленная цель достигается тем, что в устройство сопряжения, со- держашее блок 1 дешифрации адреса, регистр данных 8, регистр адреса 6, регистр команд 15, блок управления 18 и блок захвата магистрали 16, введены первый 4 и второй 5 формирователи данных, первый 2 и второй 3 формирователи адреса, первый 0 и второй 11 сумматоры, первый 12 и второй 13счетчики, второй регистр адреса 7, блок 14управления регистрами данных, второй блок 17 захвата магистрали, второй блок управ,г1ения 19 и мультиплексор 20. 5 ил. 2 табл. iC

дами блока управления регистрами данных, четвертый вход которого соединен с выходом мультиплексора, второй и третий входы которого соединены соответственно с первыми

выходами первого и второго блоков управления, вторые выходы которых соединены соответственно с управляющими входами пер Вого и второго счетчиков.

Таблица 1

Таблица 2

ВДЧ от IB

т С

flO

ша

21

отв

omW

O,

am 15

am 1ft

от lit

omJ6lJ7)JIL.

Dm/S(7)JEL

шв

22

ОТВ

Фиг. 2

к 17

3/f/7

KfZ(t3)

Фиг.З

Х j

44

со

§2

от 18(f9)

л

45

415

25

7/Л /2

UO

п., Н

4Й

ЗДШкв

ffd

ЦПкд

--

2

59

1

-

ШкВ 61

РЗП )

5

56

ЗДП2 К9

57

65

P4J

(19) СЬР К15

ФигЛ

Ш250:

62

om1 от 16

РЛП

. ,5

от 8,9,5

Фиг. 5

| Устройство для сопряжения | 1977 |

|

SU648974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-30—Публикация

1987-04-13—Подача