113

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных машинах.

Целью изобретения является повышение быстродействия.

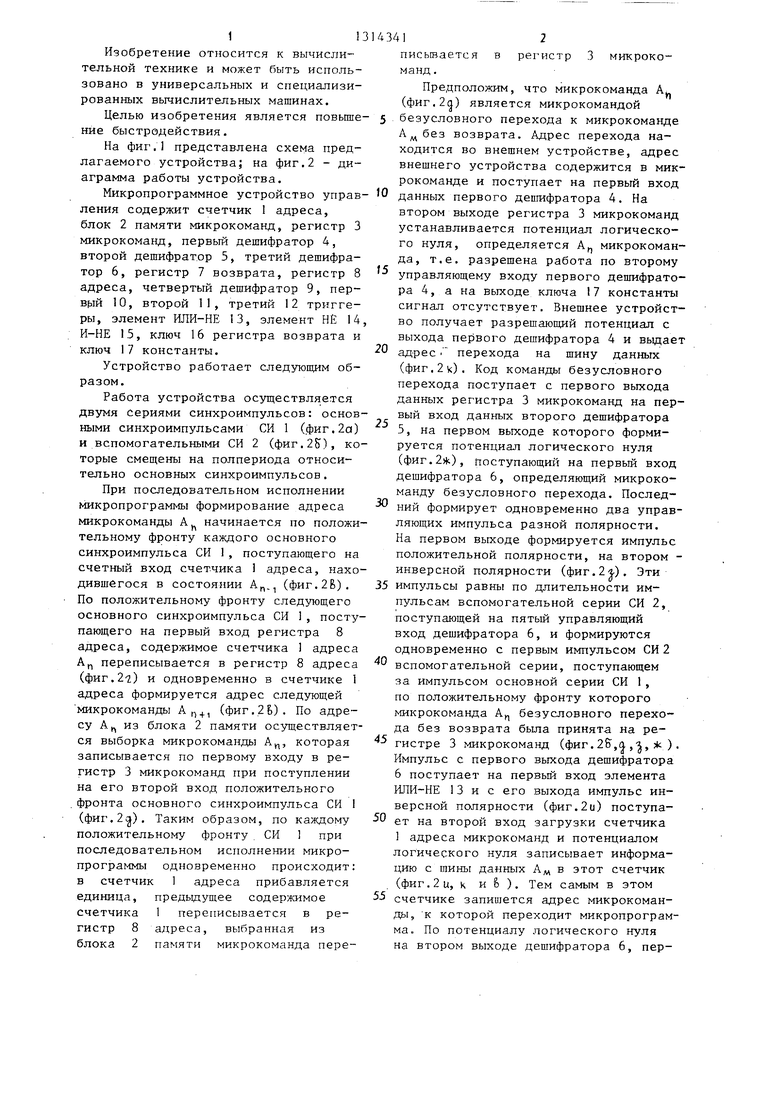

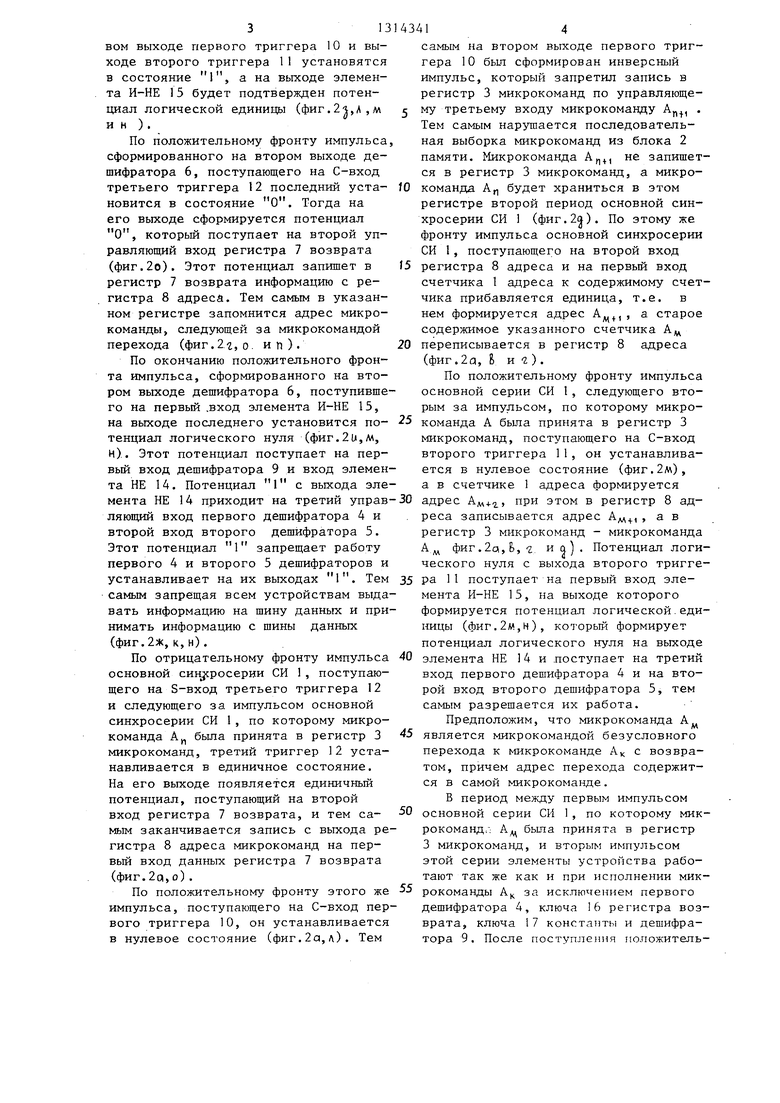

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - диаграмма работы устройства.

Микропрограммное устройство управления содержит счетчик 1 адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, первый дешифратор 4, второй дешифратор 5, третий дешифратор 6, регистр 7 возврата, регистр 8 адреса, четвертый дешифратор 9, пер- 10, второй 11, третий 12 триггеры, элемент ИЛИ-НЕ 13, элемент НЕ 14, И-НЕ 15, ключ 16 регистра возврата и ключ 17 константы.

Устройство работает cлeдyюш м образом.

Работа устройства осуществляется двумя сериями синхроимпульсов: основными синхроимпульсами СИ 1 (фиг.2а) и вспомогательными СИ 2 (фиг.25), которые смещены на полпериода относительно основных синхроимпульсов.

При последовательном исполнении микропрограммы формирование адреса микрокоманды А начинается по положительному фронту каждого основного синхроимпульса СИ 1, поступающего на счетный вход счетчика 1 адреса, находившегося в состоянии Af,., (фиг.2В). По положительному фронту следующего основного синхроимпульса СИ 1, поступающего на первый вход регистра 8 адреса, содержимое счетчика 1 адреса А переписывается в регистр 8 адреса (фиг. 2-2) и одновременно в счетчике 1 адреса формируется адрес следующей микрокоманды А п, (фиг.2&). По адресу Af, из блока 2 памяти осуществляется выборка микрокоманды А,, которая записывается по первому входу в регистр 3 микрокоманд при поступлении на его второй вход положительного фронта основного синхроимпульса СИ 1 (фиг.2). Таким образом, по каждому положительному фронту . СИ 1 при последовательном исполнении микропрограммы одновременно происходит: в счетчик 1 адреса прибавляется единица, предыдуп1ее содержимое счетчика 1 переписывается в регистр 8 адреса, выбранная из блока 2 памяти микрокоманда пере12

письгоается в регистр 3 микрокоманд.

Предположим, что микрокоманда А (фиг.2д) является микрокомандой

безусловного перехода к микрокоманде возврата. Адрес перехода находится во внешнем устройстве, адрес внешнего устройства содержится в микрокоманде и поступает на первый вход

данных первого дешифратора 4. На

втором выходе регистра 3 микрокоманд устанавливается потенциал логического нуля, определяется А, микрокоманда, т.е. разрешена работа по второму управляющему входу первого дешифратора 4 , а на выходе ключа 17 константы сигнал отсутствует. Внешнее устройство получает разрешаюш 1й потенциал с выхода первого дешифратора 4 и вьщает

адрес. перехода на шину данных

(фиг,2k), Код команды безусловного перехода поступает с первого выхода данных регистра 3 микрокоманд на первый вход данных второго дешифратора 5, на первом выходе которого формируется потенциал логического нуля (фиг.2), Поступающий на первый вход дешифратора 6, определяющий микрокоманду безусловного перехода. ПоследНИИ формирует одновременно два управляющих импульса разной полярности. На первом выходе формируется импульс положительной полярности, на втором - инверсной полярности (фиг.2ф). Эти

импульсы равны по длительности импульсам вспомогательной серии СИ 2, поступающей на пятый управляющий вход дешифратора 6, и формируются одновременно с первым импульсом СИ 2

вспомогательной серии, поступающем

за импульсом основной серии СИ 1, по положительному фронту которого микрокоманда А безусловного перехода без возврата была принята на гистре 3 микрокоманд (фиг.2б , , j, ;k ) Импульс с первого выхода дешифратора 6 поступает на первый вход элемента ИЛИ-НЕ 13 и с его выхода импульс инверсной полярности (фиг.2и) поступа50 ет на второй вход загрузки счетчика 1 адреса микрокоманд и потенциалом логического нуля записывает информацию с шины данных А, в этот счетчик (фиг.2и, к и 6 ). Тем самым в этом

55

счетчике запишется адрес микрокоманды, К которой переходит микропрограмма. По потенциалу логического нуля на втором выходе дешифратора 6, пер313

BOM выходе первого триггера 10 и выходе второго триггера 11 установятся в состояние 1, а на выходе элемента И-НЕ 15 будет подтвержден потенциал логической единицы (фиг.2,А,м и н ) .

По положительному фронту импульса сформированного на втором выходе дешифратора 6, поступающего на С-вход третьего триггера 12 последний установится в состояние О. Тогда на его выходе сформируется потенциал О, который поступает на второй управляющий вход регистра 7 возврата (фиг.2о). Этот потенциал запишет в регистр 7 возврата информацию с регистра 8 адреса. Тем самым в указанном регистре запомнится адрес микрокоманды, следующер за микрокомандой перехода (фиг.2-г, о. ип).

По окончанию положительного фронта импульса, сформированного на втором выходе дешифратора 6, поступившего на первый .вход элемента И-НЕ 15, на выходе последнего установится потенциал логического нуля (фиг.2и,ЛА, Н). Этот потенциал поступает на первый вход дешифратора 9 и вход элемента НЕ 14. Потенциал 1 с выхода элемента НЕ 14 приходит на третий управляющий вход первого дешифратора 4 и второй вход второго дешифратора 5. Этот потенциал 1 запрещает работу первого 4 и второго 5 дешифраторов и устанавливает на их выходах 1. Тем самым запрещая всем устройствам выдавать информацию на шину данных и принимать информацию с шины данных (фиг.2ж, к, н).

По отрицательному фронту импульса основной син росерии СИ 1, поступающего на S-вход третьего триггера 12 и следующего за импульсом основной синхросерии СИ I, по которому микрокоманда А была принята в регистр 3 микрокоманд, третий триггер 12 устанавливается в единичное состояние. На его выходе появляется единичный потенциал, поступающий на второй вход регистра 7 возврата, и тем самым заканчивается запись с выхода регистра 8 адреса микрокоманд на первый вход данных регистра 7 возврата (фиг.2а,о).

По положительному фронту этого же импульса, поступающего на С-вход первого триггера 10, он устанавливается в нулевое состояние (фиг.2а,л). Тем

14

самым на втором выходе первого триггера 10 6bLa сформирован инверсный импульс, который запретил запись в регистр 3 микрокоманд по управляющему третьему входу микрокоманду А„, . Тем самым нарушается последовательная выборка микрокоманд из блока 2 памяти. Микрокоманда А, не запишется в регистр 3 микрокоманд, а микрокоманда А будет храниться в этом регистре второй период основной синхросерии СИ 1 (фиг.2). По этому же фронту импульса основной синхросерии СИ I, поступающего на второй вход

регистра 8 адреса и на первый вход счетчика 1 адреса к содержимому счетчика прибавляется единица, т.е. в нем формируется адрес А,, а старое содержимое указанного счетчика А

переписывается в регистр 8 адреса (фиг.2а, & и г).

По положительному фронту импульса основной серии СИ 1, следующего вторым за импульсом, по которому микрокоманда А была принята в регистр 3 микрокоманд, поступающего на С-вход второго триггера 11, он устанавливается в нулевое состояние (фиг.2А), а в счетчике 1 адреса формируется

адрес Адд., при этом в регистр 8 ад- реса записывается адрес А , а в регистр 3 микрокоманд - микрокоманда А дд фиг.2а,Е), -г. °, Потенциал логического нуля с выхода второго триггеРа 11 поступает на первый вход элемента И-НЕ 15, на выходе которого формируется потенциал логической.единицы (фиг.2м,н), который формирует потенциал логического нуля на выходе

элемента НЕ 14 и поступает на третий вход первого дешифратора 4 и на второй вход второго дешифратора 5, тем самым разрешается их работа.

Предположим, что микрокоманда А.. является микрокомандой безусловного

перехода к микрокоманде с возвратом, причем адрес перехода содержится в самой микрокоманде.

В период между первым импульсом

основной серии СИ 1 , по которому микрокоманда- Ад бьша принята в регистр 3 микрокома1-щ, и вторым иьтульсом этой серии элементы устройства работают так же как и при исполнении микрокоманды А за исключением первого дешифратора 4, ключа 16 регистра возврата, ключа 17 константы и дешифратора 9. После поступления положитель5 3

ного фронта импульса основной синхро- серии СИ 1 (фиг,2) на третий вход регистра 3 микрокоманд, по которому микрокоманда А„ записывается в реm

гистр 3 микрокоманд и на его втором выходе устанавливается потенциал логической единицы, служащий признаком того, что в микрокоманде содержится информация, передаваемая на шину данных. Потенциал логической единицы с второго выхода регистра 3 микрокоманд поступает на второй вход первого дешифратора 4 и запрещает его работу, т.е. все внешние устройства относительно описываемого и соединенные с шиной данных получают с выхода первого дешифратора 4 потенциалы, запрещающие выдачу информации на шину данных.

Потенциал логической единицы с второго выхода регистра 3 микрокоманд поступает на второй вход ключа 17 константы и разрешает передачу информации с его выхода на шину данных (фиг.2 к). Запись информации с шины данных в счетчик 1 адреса микрокоманд осуществляется так же как при выполнении микрокоманды А (фиг. 2 ,, ,и,К,л,М ин). В регистр 7 возврата запишется адрес микрокоманды А;,., в соответствии с временной диаграм-- мой (фиг.2а,5,0 и и). Для того, чтобы обеспечить возврат выполняемой микропрограммы к микрокоманде, хранящейся в блоке 2 памяти по адресу А, необходимо обеспечить передачу содержимого регистра 7 возврата через шину данных в счетчик t адреса возврата в течение второго цикла исполнения микропрограммы А, т.е. в течение времени между первым импульс- сом, следующим за импульсом основной синхросерии СИ 1, по которому на регистр 3 микрокоманд была принята микрокоманда А;,, и вторым импульсом основной синхросерии СИ 1 (фиг. 2 ск- и а). Управляющие сигналы-для выполнец

ния возврата формирует дешифратор 9. После этого на третьем выходе регистра 3 микрокоманд появится потенциал логической единицы, служащий признаком того, что исполняемая микрокоманда перехода с возвратом. С появлением потенциала логического нуля на выходе элемента И-НЕ 15 на втором выходе дешифратора 9 формируется потенциал логического нуля (фиг.2р), который запретит передачу информации с

6

первого выхода регистра 3 микрокоманды через ключ 17 константы на шину данных. Одновременно этот потенциал поступает на второй вход ключа 16 регистра возврата и разрешает передачу информации на шину данных (фиг.2 к и р ) .

На первом выходе дешифратора 9 возврата формируется положительный

импульс, равный по длительности импульсу дополнительной синхросерии СИ 2, который поступает на третий вход дешифратора 9 возврата (фиг.2с, a,S и а). Импульс с второго выхода

дешифратора инверсной полярности поступает на первый вход счетчика I адреса и обеспечивает занесение информации с шины данных (фиг.2е,и, к и &), т.е. произойдет загрузка содержимого регистра 7 возврата на шину данных.

25

По положительному фронту второго импульса основной синхросерии СИ 1, поступающего на второй вход счетчика

1 адреса, на второй вход регистра 8 адреса и третий вход регистра 3 микрокоманд, прибавится единица к содержимому счетчика 1 адреса и его содер30 жимое станет-равным А. Старое содержимое указанного счетчика перепишется в регистр 8 адреса, содержимое которого станет равным А., , а в регистр 3 микрокоманд запишется микро35 команда А , (фиг. 2а, ё, г и а ).

В соответствии с принципом работы предлагаемого устройства следующей микрокомандой в регистре 3 микрокоманд будет записана микрокоманда

40 А (фиг. 2-1). Тем самым нет необходимости ставить после микрокоманды AJ, микрокоманду возврата к микрокоманде А,,.

45 Формула, изобретения

Микропрограммное устройство управления, содержащее счетчик адреса, блок памяти М1 крокоманд, регистр мик50 рокоманд, с первого по четвертый дешифраторы, регистр возврата, первый и второй триггеры, причем выход блока памяти микрокоманд соединен с информационным входом регистра микро55 команд, отличающееся тем что, с целью повьш1ения быстродействия, в него введены регистр адреса, третий триггер, элемент И-НЕ, эле713

мент.НЕ, элемент ИЛИ-НЕ, ключ регистра возврата, ключ константы, причем вход кода команды устройства соединен с информационным входом счетчика адреса, выход которого соединен с информационным входом регистра адреса, выход которого соединен с информационным, входом регистра возврата и с адресным входом блока памяти микрокоманд, выход поля микроопераций регистра микрокоманд соединен с первым выходом микроопераций устройства, выход поля кода источника информации регистра микрокоманд соединен с информационным входом первого дешифратора, выход которого соединен с вторым выходом микроопераций устройства выход поля кода приемника информации регистра микрокоманд соединен с информационным входом второго дешифратора, первый выход которого соединен с третьим выходом микроопераций устройства, выход поля признака типа микрокоманды регистра микрокоманд соединен с первым стробирующим входом первого дешифратора и первым уп- равляюш;им входом ключа константы, выход поля константы регистра микрокоманд соединен с информационным входом ключа константы, выход которого соединен с выходом константы устройства, вход условий устройства соединен с первым информационным входом третьего дешифратора, первый выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом синхронизации счетчика адреса, выход поля кода возврата регистра микрокоманд соединен с первым информационным входом четвертого дешифратора, первый выход которого соединен с вторым входом элемента ИЛИ-НЕ, второй выход второго дешифратора соединен с вторым информационным входом третьего дешифратора, третий выход второго дешифратора соеди18

нен с третьим информационным входом третьего дешифратора, четвертый выход второго дешифратора соединен с четвертым информационным входом тре- тьего дешифратора, пятый выход второго дешифратора соединен с пятым информационным входом третьего дешифратора, второй выход которого соединен с входом установки в 1 .первого

триггера, прямой выход которого соединен с информационным входом второго триггера, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с вторым информационным входом четвертого дешифратора, второй выход которого соединен с вторым управляюшим входом ключа константы и с управляюпщм входом ключа регистра возврата, выход которого

соединен с выходом адреса возврата устройства, первый вход синхронизации устройства соединен со счетным входом счетчика адреса, с входами синхронизации регистра адреса, регистра микрокоманд, первого и второго триггеров, и с выходом установки в I третьего триггера, выход которого соединен с входом синхронизации регистра возврата, выход которого соединен с информационным входом ключа регистра возврата, второй вход синхронизации устройства соединен со стробирующими входами четвертого и третьего дешифраторов, второй выход

которого соединен с входом установки в 1 второго триггера, с входом синхронизации третьего триггера и с вторым входом элемента И-НЕ, выход которого соединен с входом элемента

.НЕ, выход которого соединен со стро- бирующим входом второго дешифратора и с вторым стробирующим входом первого дешифратора, инверсный выход первого триггера соединен с входом

разрешения записи регистра микрокоманд.

Заказ ,2214/49

Тираж 673Подписное

ВНИИГТИ Государственно о коьтитета С.ССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д. 4/5

Производственно-полиграфическое предприятие, г. )род, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1200288A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

Изобретение предназначено для использования в универсальных и спеко5 76, П вий Om6j. ка5 циализированных вычислительных машинах. Изобретение позволяет повысить быстродействие за счет сокращения числа формируемь х микрокоманд и сокращения цикла работы устройства путем совмещения во времени процесса формирования адреса микрокоманд. Устройство содержит счетчик 1 адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, первый 4, второй 5, третий 6, четвертый 9 дешифраторы, регистр 7 возврата, регистр 8 адреса, первый 10, второй 11, третий 12 триггеры, элемент ИЛИ-НЕ 13, элемент НЕ 14, элемент И-НЕ 15, ключ 16 регистра возврата, ключ 17 константы. 2 ил. вылод (Л СО 4 /Яблоку (риг.1

| Микропрограммное устройство управления | 1980 |

|

SU935959A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1019450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-30—Публикация

1985-12-09—Подача