Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах для аппаратного вычисления функции D + Y + .

Цель изобретения - упрощение устройства.

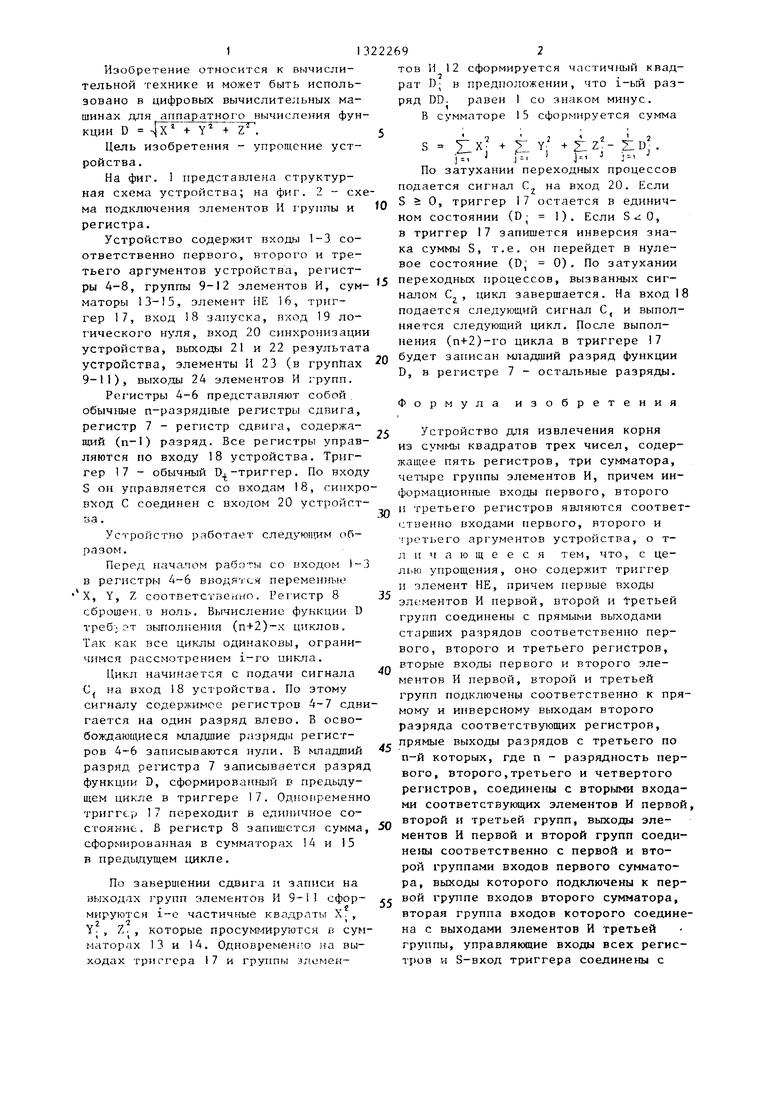

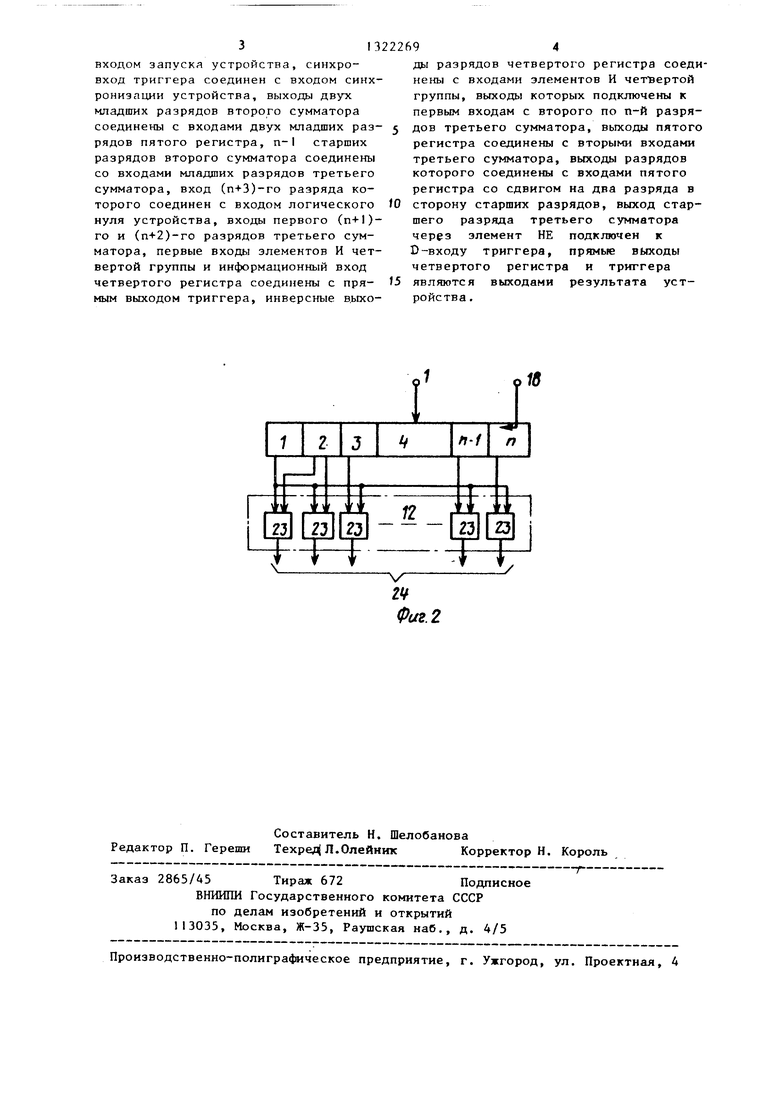

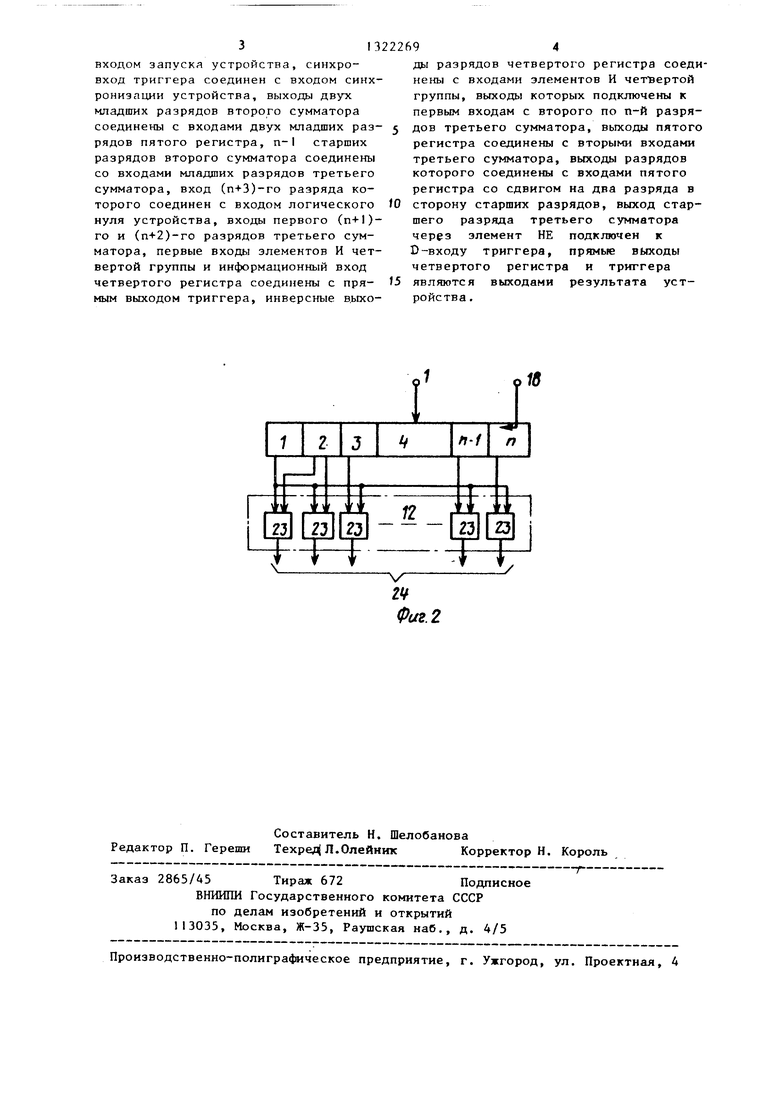

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема подключения элементов И группы и регистра.

Устройство содержит входы 1-3 соответственно первого, второго и третьего аргументов устройства, регистры 4-8, группы 9-12 элементов И, сумматоры 13-15, элемент НЕ 16, триггер 17, вход 18 запуска, вход 19 логического нуля, вход 20 синхронизации устройства, выходы 21 и 22 результата устройства, элементы И 23 (в группах 9-11), выходы 24 элементов И групп.

Регистры 4-6 представляют собой обычные п-разрядные регистры сдвига, регистр 7 - регистр сдвига, содержавши (п-1) разряд. Все регистры управляются по входу 18 устройства. Триггер 17 - обычный D -триггер. По входу S он управляется со входам 18, синхро вход С соединен с входом 20 устройства .

Устройство работает следующим образом.

Перед началом работы со входом 1-3 в регистры 4-6 в)юдятся переменньи X, Y, Z соответственно. Рег истр 8 сброшен.D ноль. Вычисление функции D требует выполнения (п+2)-х циклов. Так как все циклы одинаковы, ограничимся рассмотрением i-ro unK.ria.

Цикл начинается с подачи сигнала С на вход 18 устройства. По этому сигналу содержимое регистров 4-7 сдвигается на один разряд влево. В освобождающиеся разряды регистров 4-6 записываются нули. В младший разряд регистра 7 записывается разряд функции D, сформированный в предыдущем цикхге в триггере 17. Одновременно триггер I7 переходит в едиличное состояние. В регистр 8 запишется сумма, сформированная в сумматорах 14 и 15 в предыдущем цикле.

По завершении сдвига и записи на

выходах групп элементов И 9-1 сфор€мируются частичные квадраты X. ,

Y. , Zr, которые просумгдаруются в сумматорах 13 и 14. Одновременно ла выходах триггера 1 7 и гругты элементов И 12 сформируется частичный квадрат D; в предположении, что i-ый разряд DD. равен I со знаком минус.

В сумматоре 15 сформируется сумма

Х Г Y. ±Z

-.r: J fr: 1 M J

«r

j

По затухании переходных процессов подается сигнал С на вход 20. Если S 5 О, триггер 17 остается в единичном состоянии (D 1). Если , в триггер 17 запишется инверсия знака суммы S, т.е. он перейдет в нулевое состояние (D 0). По затухании переходных процессов, вызванных сигналом С , цикл завершается. На вход 18 подается следующий сигнал С, и выполняется следующий цикл. После выполнения (п+2)-го цикла в триггере 17 будет записан младший разряд функции D, в регистре 7 - остальные разряды.

5

0

5

0

5

0

Формула изобретения

Устройство для извлечения корня из суммы квадратов трех чисел, содержащее пять регистров, три сумматора, четыре группы элементов И, причем ин- формацион1ше входы первого, второго и третьего регистров являются соответственно входами первого, второго и третьего аргументов устройства, о т- л и ч а ю щ е е с я тем, что, с целью упрощения, оно содержит триггер и элемент НЕ, причем первые входы элементов И первой, второй и tpeтьeй групп соединены с прямыми выходами старщих разрядов соответственно первого, второго и третьего регистров, вторые входы первого и второго элементов И первой, второй и третьей групп подключены соответственно к прямому и инверсному выходам второго разряда соответствующих регистров, прямые выходы разрядов с третьего по п-й которых, где п - разрядность первого, второго,третьего и четвертого регистров, соединены с вторыми входами соответствующих элементов И первой, второй и третьей групп, выходы элементов И первой и второй групп соединены соответственно с первой и второй группами входов первого сумматора, выходы которого подключены к пер- e ВОЙ группе входов второго сумматора, вторая группа входов которого соединена с выходами элементов И третьей группы, управляющие входы всех регистров vi S-вход триггера соединены с

входом запуска устройства, синхро- вход триггера соединен с входом синхронизации устройства, выходы двух младших разрядов второго сумматора соединены с входами двух младших разрядов пятого регистра, п-I старших разрядов второго сумматора соединены со входами младших разрядов третьего сумматора, вход ()-го разряда которого соединен с входом логического нуля устройства, входы первого (п+1)- го и ()-го разрядов третьего сумматора, первые входы элементов И четвертой группы и информационный вход четвертого регистра соединены с прямым выходом триггера, инверсные в.ыхо

ды разрядов четвертого регистра соединены с входами элементов И четвертой группы, выходы которых подключены к первым входам с второго по п-й разрядов третьего сумматора, выходы пятого регистра соединены с вторыми входами третьего сумматора, выходы разрядов которого соединены с входами пятого регистра со сдвигом на два разряда в сторону старших разрядов, выход старшего разряда третьего сумматора через злемент НЕ подключен к D-входу триггера, прямые выходы четвертого регистра и триггера являются выходами результата устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1283753A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах ДЛЯ аппаратного вычисления функции D + Y + .Цель изобретения - упрощение устройства - достигается за счет введения в устройство, содержащее пять регистров, четыре группы элементов И 4-8, 9-12 и три сумматора 13-15, триггера 17, элемента НЕ И соответствующего подключения элементов схемы. 2 ил. (Л

| Устройство для вычисления корняКВАдРАТНОгО из СуММы КВАдРАТОВ | 1979 |

|

SU813424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-13—Подача