11354249

етение относится к вычислитехнике и может быть исгюль- ри построении асинхронных в приема и хранения информа

изобретения упрощение паого асинхронного регистра.

зн та

с си

вы к ни л з п д 15 т л с м г н

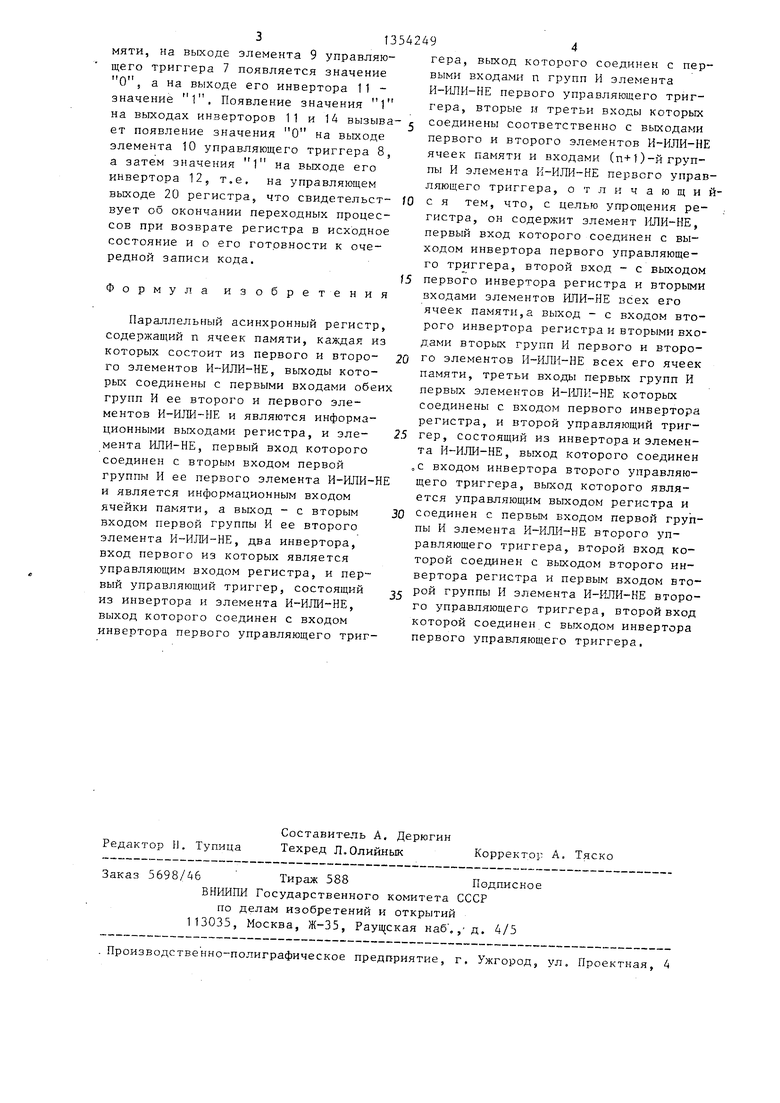

На чертеже представлена схема регистра.

Регистр содержит ячейки 1-3 памяти, каждая из которых состоит из первого 4 и второго 5 элементов И-ЙПИ-НЕ ИЛИ-НЕ 6., первый 7 и второй 8 управляющие триггеры, состоящие из элементов И ИЛИ-НЕ 9 и 10 инверторов 11 и 12 соответственно, первый 13 и второй 14 инверторыэ элемент ИЛИ-НЕ 15, управляющий вход 16,, информацион- ные входы 17-19 и управляющий выход 20,

Параллельный асинхронный регистр работает следующим образом,

В начальном состоянии на управляющем входе 16 регистра имеется значение О, При этом на выходе инвертора 13 имеется значение 1, а на выходе элемента 15 и элементов 6 ячеек 1-3 памяти значение О. В результате на выходах обоих элементов 4 и 5 ячеек 1-3 памяти имеются значения 1, на выходе элемента 9 управляющего триггера 7 - значение О, а на выходе его инвертора 11 - значени Такое же значение и на выходе инвертора 14, что вызывает появление О

значения U на выходе элемента 19 управляющего триггера 8 и значения

1 на выходе его инвертора 12 т,е, на управляющем выходе 20 регистраi

После того, как информационные входы 17-19 ячеек 1-3 памяти поступают однофазные сигналы, соответствующие значениям разрядов записывав-- мого кода, на управляющий вход 16 регистра подается значение 1. При этом, если в ячейку памяти записывается единица j, т,е„ ка ее информационный вход поступает значение j то на выходе ее элемента 4 устанавливается значение О, а ка выходе ее элемента 6 сохраняется такое же значение. Если в ячейку памяти записывается нуль, т.е. на ее информационный вход поступает значение О, то после того, как на выходе инвертора 13 появляется такое же значен.ие, на выходе ее элемента 6 устанавливается

значение 1 , а на вьгкоде ее элемента 5 - значение О,

Таким образом, в результате запи-- си информации в ячейки 1-3 памяти на

выходе одного из элементов 4 или 5 каждой из них появляется значение О, что приводит к появлению значения 1 на выходе элемента 9 управляющего триггера 7, а затем значение О на выходе его инвертора 11 в результате чего на выходе элемента 15 появляется значение 1, Последнее делает ячейки 1-3 памяти нечувстви- тельными к изменению значений сигналов на их информационных входах (отсекает ячейки 1-3 памяти от информационных входов 17-19) и, кроме того, вызывает пояВоТение значения О на выходе инвертора 14, затем значе

5

ния 1 на выходе элемента 10 управляющего триггера 8 и значения О на выходе его инвертора 12, т.е. на управляющем выходе 20 регистра,

5 что свидетельствует об окончании

переходник процессов при записи кода в регистр и установки парафазного кода на соответствующих выходах ячеек 1-3 памяти,

0 После этого произвольным образом могут изменяться сигналы на информа- 1 7 - 1 9

ячеек

-J пационных входах

мяти с тем, чтобь: к моменту следующей записи кода в регистр на этих входах были уста:. ;:овлеиы значения, соответствующие разрядам записываемого кода. Перед новой записью кода регистр дох1жен быть возБраихеи в исходное состояние ,

Перевод ре гисгра в исходное состояние осуществл 1егся пода-гей значения О на его управ-пяющий вход t-б. Это вызывает появлеиле з :ачения 1 на выходе инвертора 13; а затем значе- 5 ния О на выходе элемента 15 и значения 1 на выходе инвертора 14,При этом, если .в ячейку записана единица, то на выходе ее элемента 4 устанавли- 1,

0

вается значение

а на выходе ее

ЁО элементов 5 и 6 сохраняются значения

1 и О соответстзенно Если в ячейку записан нуль, то скачала на выходе ег элемента 6 устанавливается значение О мента 5 - значение сохраняется на выходе элемента 4, После того, как значение

а затем на выходе эле- начение 1 и такое знапоявляется на выходах

зоих элементов 4 и 5 ка)1дой из ячеек 1-3 па313542

мяти, на выходе элемента 9 управляющего триггера 7 появляется значение

О

а на выходе его инвертора 1 1 значение 1, Появление значения Г на выходах инверторов 11 и 14 вызыва ет появление значения О на выходе элемента 10 управляющего триггера 8, а затем значения 1 на выходе его инвертора 12, т.е. на управляющем выходе 20 регистра, что свидетельствует об окончании переходных процессов при возврате регистра в исходное состояние и о его готовности к очередной записи кода.

Формула изобретения

Параллельный асинхронный регистр, содержащий п ячеек памяти, каждая из которых состоит из первого и второ- го элементов И-ИЛИ-НЕ, выходы которых соединены с первыми входами обеи групп И ее второго и первого элементов И-ИЛИ-НЕ и являются информационными выходами регистра, и элемента ИЛИ-НЕ, первый вход которого соединен с вторым входом первой группы И ее первого элемента И-ИЛИ-Н и является информационным входом ячейки памяти, а вьсход - с вторым входом первой группы И ее второго элемента И-ИЛИ-НЕ, два инвертора, вход первого из которых является управляющим входом регистра, и первый управляющий триггер, состоящий из инвертора и элемента И-ИЛИ-НЕ, выход которого соединен с входом инвертора первого управляющего триг

Редактор Н. Тупица Заказ 5698/46

Составитель А. Дерюгин

Техред Л.Олийнык Корректор А, Тяско

Тираж 588Подписное

ВНРШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб ,, д. 4/5

.Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

с

5

5

0

0

494

гера, выход которого соединен с первыми входами п групп И элемента И-ИЛИ-НЕ первого управляющего триггера, вторые и третьи входы которых соединены соответственно с выходами первого и второго элементов И-ИЛИ-НЕ ячеек памяти и входами (п+1)-и группы И элемента И-ИЛИ-НЕ первого управляющего триггера, отличающий- с я тем, что, с целью упрощения регистра, он содержит элемент 1 ШИ-НЕ, первый вход которого соединен с выходом инвертора первого управляющего триггера, второй вход - с выходом первого инвертора регистра и вторыми входами элементов ИЛИ-НЕ всех его ячеек памяти,а выход - с входом второго инвертора регистра и вторыми входами вторых групп И первого и второго элементов всех его ячеек памяти, третьи входы первых групп И первых элементов ИЧ-ШИ-НЕ которых соединены с входом первого инвертора регистра, и второй управляющий триггер, состоящий из инвертора и элемента И-ИЛИ-НЕ, выход которого соединен ,с входом инвертора второго управляющего триггера, выход которого является управляющим выходом регистра и соединен с первым входом первой группы И элемента И-ИЛИ-НЕ второго управляющего триггера, второй вход которой соединен с выходом второго инвертора регистра и первым входом второй группы И элемента И-1ШИ-НЕ второго управляющего триггера, второй вход которой соединен с выходом инвертора первого управляющего триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный асинхронный регистр | 1988 |

|

SU1531172A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Параллельный асинхронный регистр на МДП-транзисторах | 1988 |

|

SU1615807A1 |

| Асинхронный последовательный регистр | 1990 |

|

SU1805501A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении асинхронных устройств приема и хранения информации. Целью изобретения является упрощение регистра. Для достижения этой цели в состав регистра введены элемент ИЛИ-НЕ 15 и второй управляющий триггер 8. Это позволило упростить ячейки памяти 1-3 регистра и регистр в целом. 1 ил. 15 617 СА: СП ю N СО 19

| Параллельный однофазный регистр | 1976 |

|

SU583480A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1196953, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-11-23—Публикация

1986-07-09—Подача