(Л

р- -

I г /хгзря

f ffffjjO

:UfeJl

3

00 О5

сл

00

сд

sj

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1985 |

|

SU1275777A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

Изобретение относится к вычислительной технике и дискретной автоматике. Цель изобретения - повышение надежности преобразователя. Преобразователь изменяет произвольное расположение нулей и единиц в исходном двоичном коде таким образом, что в правой части уплотненного дво-, ичного кода находятся единицы, не - разделенные нулями. Преобразователь двоичного кода в уплотненный код содержит разряды 1, выполненные на триггерах 2 и элементах И 3. 2 ил.

фиг. 1

Изобретение относится к автоматике, вычислительной технике и может использоваться в дискретных автоматических устройствах.

Целью изобретения является повышение надежности преобразователя.

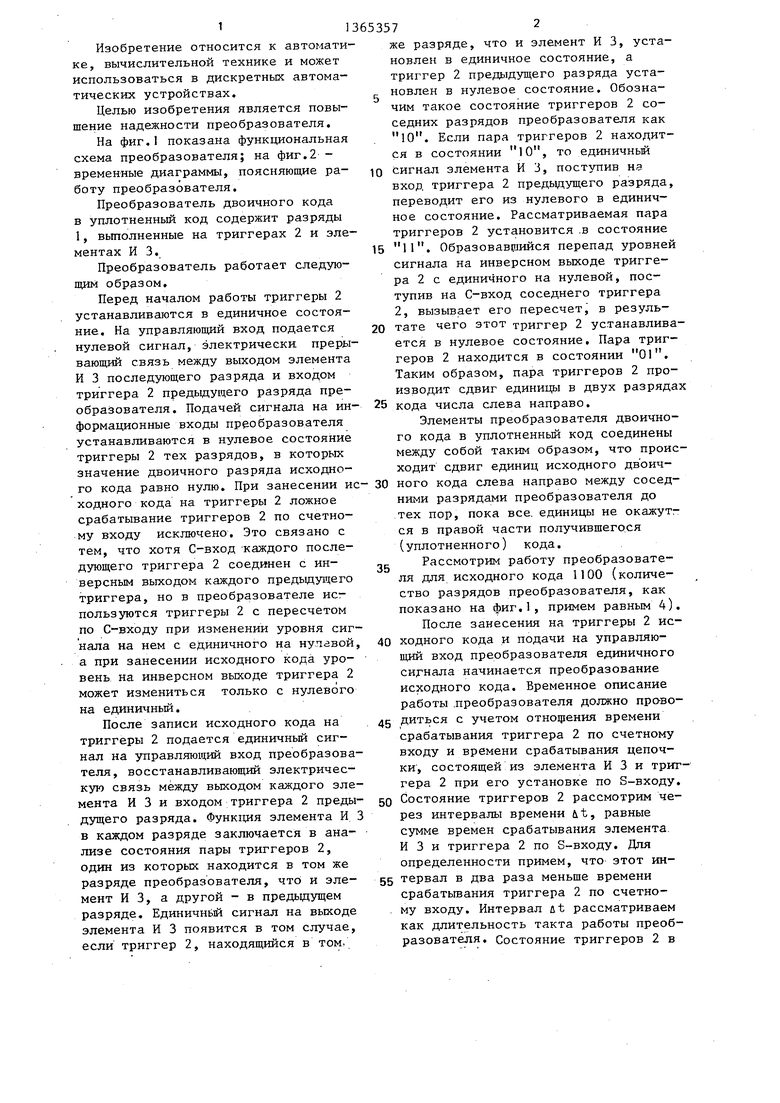

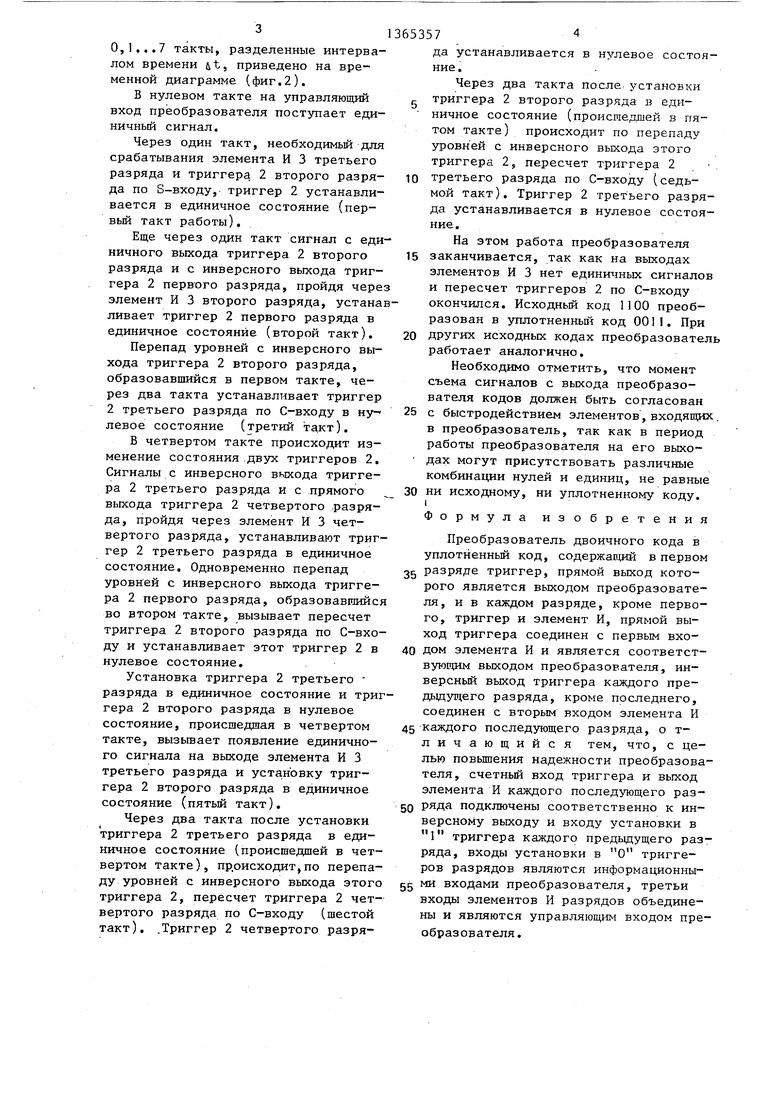

На фиг.I показана функциональная схема преобразователя; на фиг.2 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь двоичного кода в уплотненный код содержит разряды 1, вьтолненные на триггерах 2 и элементах ИЗ.

Преобразователь работает следующим образом.

Перед началом работы триггеры 2 устанавливаются в единичное состояние. На управляющий вход подается нулевой сигнал, электрически прерывающий связь между выходом элемента И 3 последующего разряда и входом триггера 2 предьщущего разряда преобразователя. Подачей сигнала на информационные входы преобразователя устанавливаются в нулевое состояние триггеры 2 тех разрядов, в которых значение двоичного разряда исходного кода равно нулю. При занесении ис- 30 ного кода слева направо между соседходного кода на триггеры 2 ложное срабатывание триггеров 2 по счетному входу исключено. Это связано с тем, что хотя С-вход каждого последующего триггера 2 соединен с инверсным выходом каждого предыду1цего триггера, но в преобразователе исг пользуются триггеры 2 с пересчетом по С-входу при изменении уровня сигнала на нем с единичного на нулевой а при занесении исходного кода уровень на инверсном выходе триггера 2 может измениться только с нулевого на единичньй,

После записи исходного кода на триггеры 2 подается единичньй сигнал на управляющий вход преобразователя, восстанавливающий электрическую связь между выходом каждого элемента И 3 и входом триггера 2 предыдущего разряда. Функция элемента И 3 в каждом разряде заключается в анализе состояния пары триггеров 2, один из которых находится в том же разряде преобразователя, что и элемент И 3, а другой - в предьщущем разряде. Единичной сигнал на выходе элемента И 3 появится в том случае, если триггер 2, находящийся в том.

же разряде, что и элемент ИЗ, установлен в единичное состояние, а триггер 2 предыдущего разряда установлен в нулевое состояние. Обозначим такое состояние триггеров 2 соседних разрядов преобразователя как Ю. Если пара триггеров 2 находится в состоянии 10, то единичньй

сигнал элемента И 3, поступив на вход триггера 2 предыдущего разряда, переводит его из нулевого в единичное состояние. Рассматриваемая пара триггеров 2 установится .в состояние

тате чего этот триггер 2 устанавливается в нулевое состояние. Пара триггеров 2 находится в состоянии 01. Таким образом, пара триггеров 2 производит сдвиг единицы в двух разрядах

кода числа слева направо.

Элементы преобразователя двоичного кода в уплотненньш код соединены между собой таким образом, что происходит сдвиг единиц исходного двоич5

0

ними разрядами преобразователя до тех пор, пока все. единицы не окажут:- ся в правой части получившегося (уплотненного) кода.

Рассмотрим работу преобразователя для исходного кода 1100 (количество разрядов преобразователя, как показано на фиг,1, примем равным 4). После занесения на триггеры 2 исходного кода и подачи на управляющий вход преобразователя единичного сигнала начинается преобразование исходного кода. Временное описание работы .преобразователя должно про-во- диться с учетом отнощения времени срабатывания триггера 2 по счетному входу и времени срабатывания цепочки, состоящей из элемента И 3 и триггера 2 при его установке по S-входу, Состояние триггеров 2 рассмотрим через интервалы времени it, равные сумме времен срабатывания элемента. И 3 и триггера 2 по S-входу. Для определенности примем, что этот ин- 5 тервал в два раза меньще времени срабатьгоания триггера 2 по счетному входу. Интервал ut рассматриваем как длительность такта работы преобразователя. Состояние триггеров 2 в

5

0

О,,,.7 такты, разделенные интервалом времени bt, приведено на временной диаграмме (фиг.2).

Б нулевом такте на управляющий вход преобразователя поступает единичный сигнал.

Через один такт, необходимьй для срабатывания элемента И 3 третьего разряда и триггера 2 второго разряда по S-входу, триггер 2 устанавливается в единичное состояние (пер- вьш такт работы).

Еще через один такт сигнал с единичного выхода триггера 2 второго разряда и с инверсного выхода триггера 2 первого разряда, пройдя через элемент И 3 второго разряда, устанавливает триггер 2 первого разряда в единичное состояние (второй такт).

Перепад уровней с инверсного выхода триггера 2 второго разряда, образовавшийся в первом такте, через два такта устанавливает триггер 2 третьего разряда по С-входу в ну левое состояние (третий такт).

В четвертом такте происходит изменение состояния .двух триггеров 2. Сигналы с инверсного выхода триггера 2 третьего разряда и с прямого выхода триггера 2 четвертого .разряда, пройдя через элемент И 3 четвертого разряда, устанавливают триггер 2 третьего разряда в единичное состояние. Одновременно перепад уровней с инверсного выхода триггера 2 первого разряда, образовавшийся во втором такте, вызывает пересчет триггера 2 второго разряда по С-входу и устанавливает этот триггер 2 в нулевое состояние.

Установка триггера 2 третьего - разряда в единичное состояние и триггера 2 второго разряда в нулевое состояние, происшедшая в четвертом такте, вызьшает появление единичного сигнала на выходе элемента И 3 третьего разряда и уста.нЬвку триггера 2 второго разряда в единичное состояние (пятьш такт).

Через два такта после установки триггера 2 третьего разряда в единичное состояние (происшедшей в четвертом такте), происходит,по перепаду уровней с инверсного выхода этого триггера 2, пересчет триггера 2 четвертого разряда по С-входу (шестой такт). .Триггер 2 четвертого разряда устанавливается в нулевое состояние .

Через два такта после: установки

триггера 2 второго разряда в еди- ничное состояние (происшедшей в пятом такте) происходит по перепаду уровней с инверсного выхода этого триггера 2, пересчет триггера 2 третьего разряда по С-входу (седьмой такт). Триггер 2 третьего разряда устанавливается в нулевое состояние.

На этом работа преобразователя

заканчивается, так как на выходах элементов И 3 нет единичных сигналов и пересчет триггеров 2 по С-входу окончился. Исходньй код 1100 преобразован в уштотненньй код ООП. При

Других исходных кодах преобразователь работает аналогично.

Необходимо отметить, что момент съема сигналов с выхода преобразователя кодов должен быть согласован

с быстродействием элементов, входяш сс. в преобразователь, так как в период работы преобразователя на его выхо- дах могут присутствовать различные комбинации нулей и единиц, не равные

ни исходному, ни уплотненному коду. I

Формула изобретения

Преобразователь двоичного кода в уплотненньй код, содержащий в первом

разряде триггер, прямой выход которого является выходом преобразователя, и в каждом разряде, кроме первого, триггер и элемент И, прямой выход триггера соединен с первым входом элемента И и является соответствующим выходом преобразователя, инверсный выход триггера каждого пре- дьщущего разряда, кроме последнего, соединен с вторым входом элемента И

каждого последующего разряда, о т- личающийся тем, что, с целью повьщтения надежности преобразователя, счетньй вход триггера и выход элемента И каждого последующего разряда подключены соответственно к инверсному выходу и входу установки в 1 триггера каждого предьщущего разряда, входы установки в О триггеров разрядов являются информационными входами преобразователя, третьи входы элементов И разрядов объединены и являются управляющим входом преобразователя.

dt Ql

Qi

шиг.г

| Устройство для подсчета количестваЕдиНиц B дВОичНОМ чиСлЕ | 1978 |

|

SU798830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в уплотненный код | 1982 |

|

SU1061131A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-07—Публикация

1986-07-04—Подача