с приемником информации. Каждая ячейка памяти 1 регистра имеет входы 8-15 и выходы 16-19. Регистр содержит дополнительные элементы И-ИЛИ НЕ 20, 21, 22, выходы которых являются выходами 4, 5, 6 регистра. Пас- ледовательно соединенные ячейки 1 регистра образуют два канала передачи информации: канал передачи единиц и канал передачи нулей. При

этом факт передачи порции информации по каждому из этих каналов фиксируется не состоянием ячейки 1 как таковым, а изменением этого состояния. Один разряд регистра составляет одна ячейка 1 - в предлагаемом регистре допустима плотная запись информации. Исключение составляют две первые и две последние ячейки 1. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1403092A1 |

| @ -Канальный формирователь последовательности импульсов | 1985 |

|

SU1305845A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1383444A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

ЯзоГ рет;ч-п е относится к пычис- jiirre ibHii; тохнпкр и может быть ис- io,nii3oi.: no npti г11-); ектировании асин- ; :pcii nj.p . pe TicTpoj сдвига. Целью )рете11ия ят,. повышение 6i,iCT- роде1 1гтпия рпгцгтра. Регистр состоит и 1 ячеек 1 памяти и имеет инЛор- мяциоишю нхоль; 2, 3 и управляющий iibixou 4, соединяемые с источником ииЛопмаплти, ин(Ъормацио гные выходы 5, (. и vnpaB.iiHioiun вход 7, coeди яe fыe сл о: 1. ts5 со 015

t

Изобретение относится к вычислительной технике и может быть исполь- .зовано при проектировании асинхронных регистров сдвига.

елью изобретения является повышение быстродействия регистра.

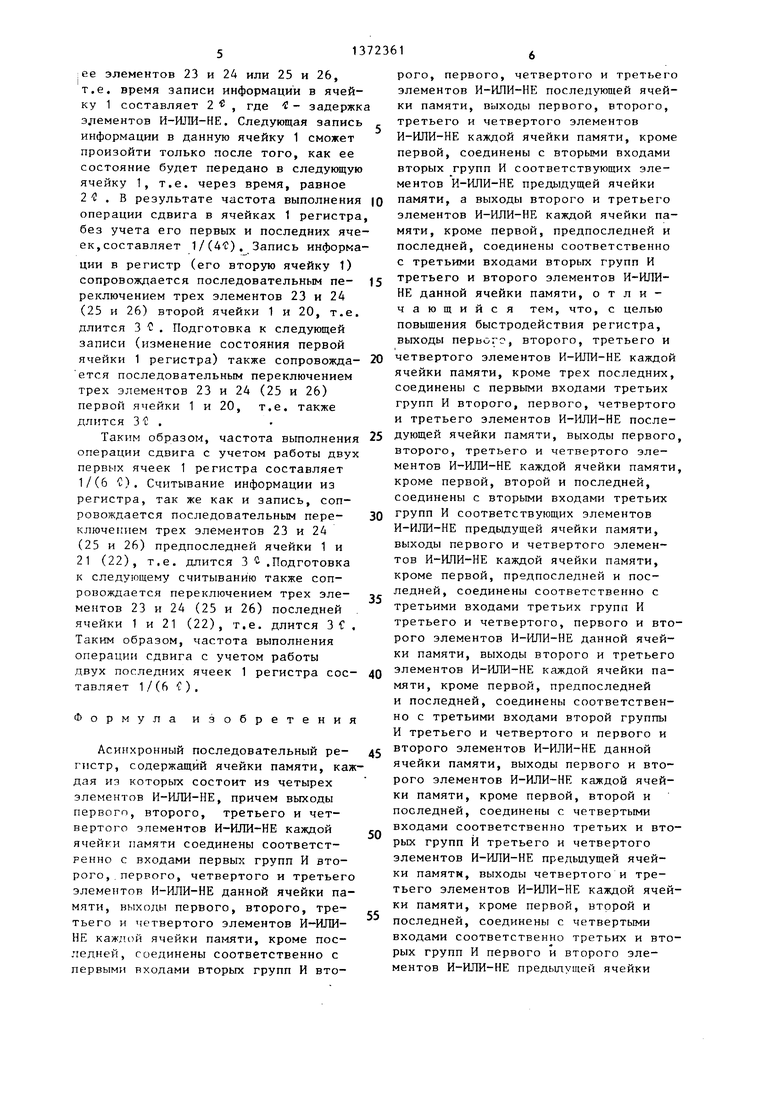

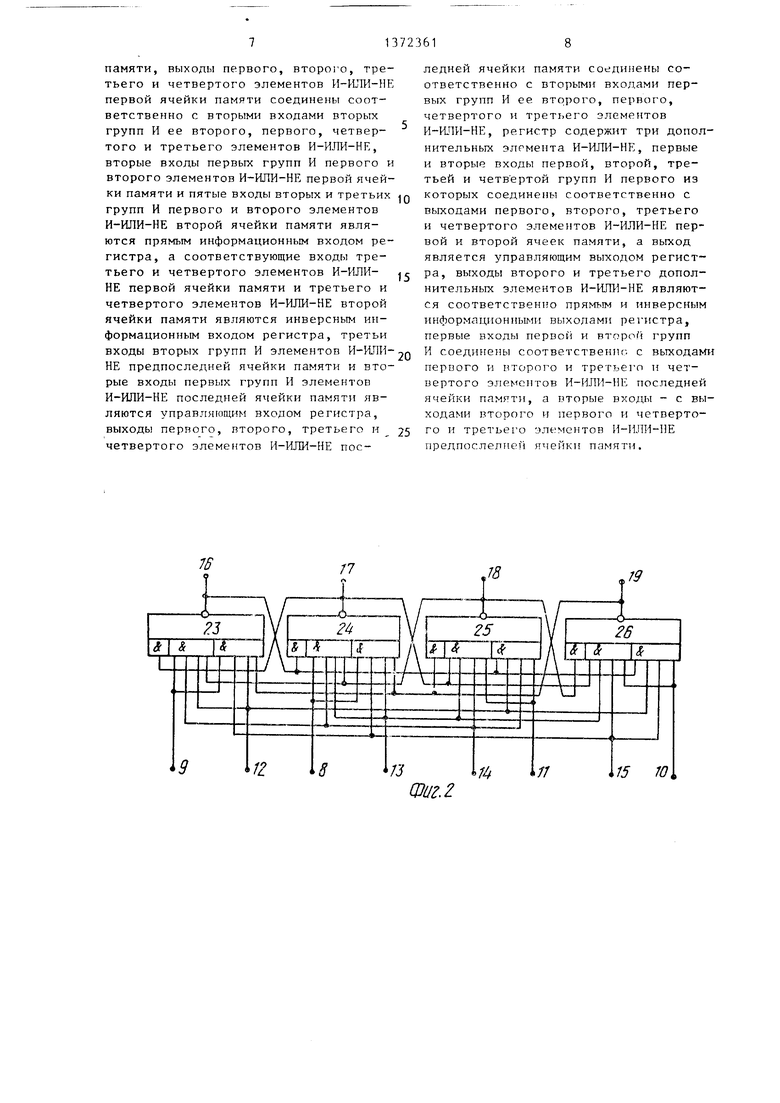

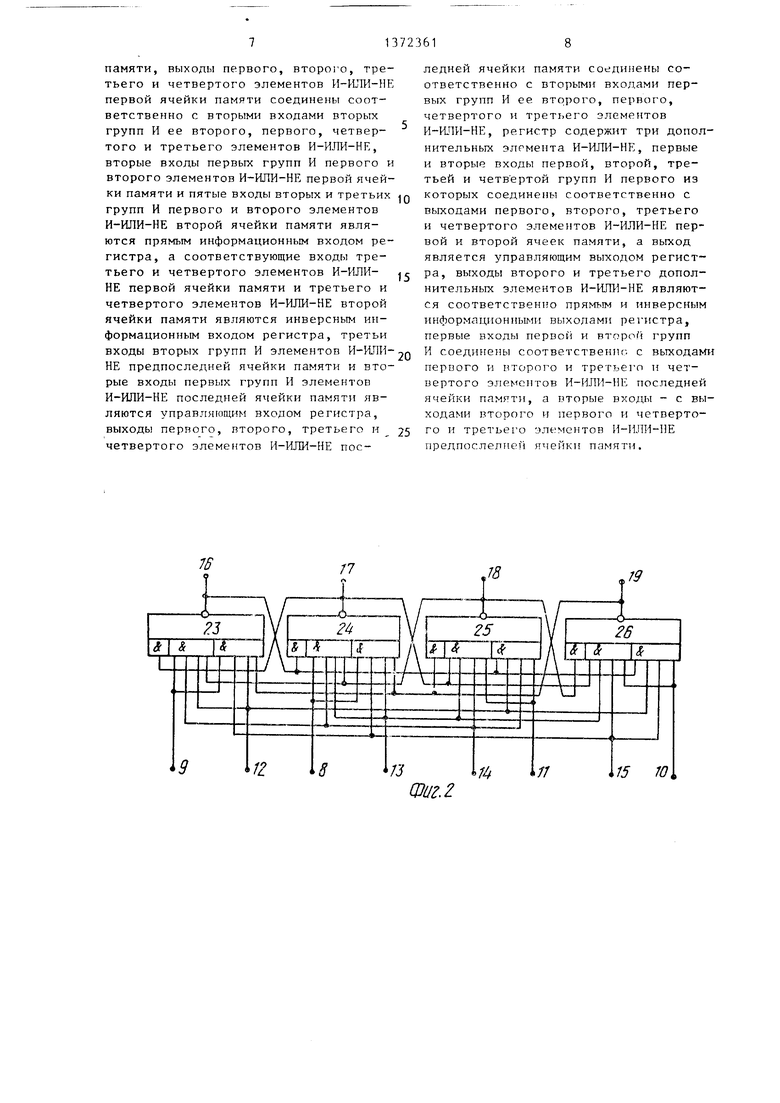

На фиг.1 приведена схема асинхронного последовательного регистра на фиг.2 - схема его ячейки памяти.

Регистр состоит из ячеек 1 памяти и имеет информационные входы 2 и 3 и управляющий выход А, соединяемые с источником информации, информационные выходы 5 и 6 и управляющий вход 7, соединяемые с приемником информации. Каждая ячейка 1 памяти регистра имеет входы 8-15 и выходы 16-19. Регистр содержит дополнительные элементы И-1ПИ-НЕ 20-22, выходы которых являются выходами Д-6 регистра.

Каждая ячейка 1 содержит элементы Р1-Ш1И-ИЕ 23-26, выходы которых являются ее выходами 16-19.

Acи rxpoнный последовательный регистр работает следующим образом.

Каждая ячейка 1 имеет четьфе устойчивых состояния (значения ее выходов 16-19): 0101, 0110, 1001 и 1 О 10 . Г лагодаря блокирующим связям выходов 16-19 последующей ячейки с входами 12-15 данной, изменение состояния данной ячейки становится возможным только после того, как состояния данной и последующей ячеек будут одинаковы. Иначе, говоря, перепись информации с выходов 16-19 предыдущей ячейки в данную через ее входы 8-11 становится возможной только после того, как информация, за0

5

0

5

0

5

0

писанная ранее в данную ячейку, будет переписана в последующую ячейку.

Последовательно соединенные ячейки 1 регистра образуют два канала передачи информации: канал передачи единиц и канал передачи нулей При этом факт передачи порции информации по каждому из этих каналов фиксируется не состоянием ячейки 1 как таковым, а изменением этого состояния. Таким образом, коду 1 соответствует состояние 0101 (0110) ячейки 1, если ее предыдущее состояние было 1001 (1010), и, наоборот: состояние 1001 (1010), если ее предьщу- щее состояние было 0101 (0110). Аналогично коду нуля соответствует состояние 0101 (1001) ячейки 1, если ее предыдущее состояние было 0110, (1010), и, наоборот: состояние 0110 (1010), если ее предьщущее состояние было 0101 (1001) .

Один разряд регистра составляет одна ячейка 1.. В предлагаемом регистре допустима плотная запись информации. Исключение составляют две первые и две последние ячейки 1.

При изменении состояния каждой ячейки 1, кроме первой и последней, переключение пар ее элементов 23, 24 и 25, 26 происходит через транзитное состояние 00, а состояние 11 в этих парах возникнуть не может. Поскольку каждая ячейка 1, кроме первой и последней, изменяет свое состояние при подаче соответствующего количества единичных значений на ее входы 8-15, то воспринимаются только устойчивые состояния соседних в ней ячеек, а их транзитные состояния не воспринимаются, т.е. они не нарушают правильного функционирования регистра.

Элементы 23 и 2А (25 и 26) первой и второй ячеек 1 образуют счетный триггер, построенный по схеме M-S с разнополярным управлением. Когда на обоих входах 2 и 3 регистра имеются значения О, т.е. информация на этих входах отсутствует, первая ячейка 1 устанавливается в такое состояние, что значения на выходах ее элементов 23-26 противоположны значениям на вькодах элементов 23-26 второй ячейки 1. В результате на одном из входов каждой группы И элемента 20 имеется значение О, и на выходе этого элемента, т.е. на выходе 4 регистра, появляется значение 1. Перепись информации из первой ячейки 1 во вторую блокируется при этом нулевыми значениями на входах 2 и 3 регистра.

Приняв единичное значение с выхода 4 регистра источник информации может подать очередной разряд сдвигаемого кода на входы 2 и 3 регистра, т.е. установить на одном из этих входов значение 1, в результате чего изменяется состояние второй ячейки 1 регистра, причем, если передается единица (значение 1 на входе 2 регистра), то изменяются и противоположные значения на выходах элементов 23, 24 второй ячейки 1, а если передается нуль (значение 1 на входе 3 регистра), то изменяются на противоположные значения на выходах ее элементов 25 и 26.

Изменение состояния второй ячейки 1 происходит, если ее предыдущее состояние переписано в третью ячейку 1. Состояние второй ячейки 1, полученное в результате подачи информации на входы 2 и 3 регистра, передается по нему от ячейки к ячейке до тех пор, пока не достигнет его предпоследней ячейки 1. Изменения состояния первой ячейки 1 не происходит из-за того, что в одной из пар ее элементов 23 и 24 или 25 и 26 оно заблокировано единичным значением на входе 2 или 3 регистра, а состояние выходов элементов другой пары противоположно состоянию выходов аналогичных элементов второй ячейки 1 регистра.

В результате изменения состояния второй ячейки 1 регистра на входах

0

5

0

5

0

5

0

5

одной из групп и элемента 20 устанавливаются значения 1, а на выходе этого элемента (выходе 4 регистру) - значение О. Получив это значение, источник информации может снова установить значения О на обоих входах 2 и 3 регистра (снять информацию с его входов) и т.д

Когда на входе 7 регистра имеется значение О, запись информации в предпоследнюю ячейку 1 регистра заблокирована и происходит изменение состояния последней ячейки 1 регистра. В результате значения на выходах элементов 23-26 этих ячеек станут одинаковыми (пары элементен 23, 24 и 25, 26 этих ячеек образуют RS -триггеры, построенные по схеме M-S с разнополярным управлением), и на одном из входов каждой группы И элементов 21 и 22 появится значение О, а на выходах этих элементов (т.е. выходах

5и 6 регистра) - значение 1, информация на этих выходах отсутствует.

Для того, чтобы считать информацию из регистра, приемник должен установить на его входе 7 значение 1, которое блокирует изменение состояния последней ячейки 1 регистра и разрешает запись информации в предпоследнюю его ячейку 1. Если при этом изменятся значения выходов элементов 23 и 24 предпоследней ячейки 1, т.е. очередной разряд сдвигаемого кода имеет единичное значение, то на входах одной из групп И элемента 21 появятся значения 1, а на выходе этого элемента (выходе 5 регистра) - значение О. Если же при этом изменятся значения выходов элементов 25 и 26 предпоследней ячейки 1, т.е. очередной разряд сдвигаемого кода имеет нулевое значение, то на входах одной из групп И элемента 22 появятся значения 1, а на выходе этого элемента (выходе 6 регистра) - значение О.

Получив информацию с выходов 5 и

6регистра, приемник может снова установить значение 1 на его входе 7 и т.д.

Для того, чтобы очистить регистр перед работой, надо изменением значения на его входе 7 считывать из него информацию до тех пор, пока состояния всех его ячеек не станут олииаковыми.

При записи информации в ячейку 1 происходит переключение одной из пар

ее элементов 23 и 24 или 25 и 26, т.е. время записи информации в ячейку 1 составляет 2 , где -С - задержк элементов И-ИЛИ-НЕ. Следующая запись информации в данную ячейку 1 сможет произойти только после того, как ее состояние будет передано в следующую ячейку 1, т.е. через время, равное 2 IJ . В результате частота выполнения операции сдвига в ячейках 1 регистра без учета его первых и последних ячеек, составляет l/CAf). Запись информации в регистр (его вторую ячейку 1) сопровождается последовательным пе- реключением трех элементов 23 и 24 (25 и 26) второй ячейки 1 и 20, т.е. длится 3 . Подготовка к следующей записи (изменение состояния первой ячейки 1 регистра) также сопровожда- ется последовательным переключением трех элементов 23 и 24 (25 и 26) первой ячейки 1 и 20, т.е. также длится 3 С .

Таким образом, частота выполнения операции сдвига с учетом работы двух первых ячеек 1 регистра составляет 1/(6 С). Считывание информации из регистра, так же как и запись, сопровождается последовательным пере- ключемием трех элементов 23 и 24 (25 и 26) предпоследней ячейки 1 и 21 (22), т.е. длится 3 .Подготовка к следующему считыванию также сопровождается переключением трех эле- ментов 23 и 24 (25 и 26) последней ячейки 1 и 21 (22), т.е. длится ЗС . Таким образом, частота выполнения операции сдвига с учетом работы двух последних ячеек 1 регистра сое- тавляет 1 / (6 С) ,

Формула изобретения

Асинхронный последовательный регистр, содержащий ячейки памяти, каждая из которых состоит из четырех элементов И-ШШ-НЕ, причем выходы первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ каждой ячейки памяти соединены соответст- ренно с входами первых групп И второго, первого, четвертого и третьего элементов Н-ИЛИ-НЕ данной ячейки памяти, выходы первого, второго, третьего и четвертого элементов И-ИЛИ- НЕ каждой ячейки па -1яти, кроме последней, соединены соответственно с первыми входами вторых групп И вто

рого, первого, четвертого и третьего элементов И-ИЛИ-НЕ последующей ячейки памяти, выходы первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, соединены с вторыми входами вторых групп И соответствующих элементов И-ИЛИ-НЕ предыдущей ячейки памяти, а выходы второго и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, предпоследней и последней, соединены соответственно с третьими входами вторых групп И третьего и второго элементов И-ИЛИ- НЕ данной ячейки памяти, отличающийся тем, что, с целью повышения быстродействия регистра, выходы первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме трех последних, соединены с первыми входами третьих групп И второго, первого, четвертого и третьего элементов И-ИЛИ-НЕ последующей ячейки памяти, выходы первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, второй и последней, соединены с вторыми входами третьих групп И соответствующих элементов И-ИЛИ-НЕ предыдущей ячейки памяти, выходы первого и четвертого элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, предпоследней и последней, соединены соответственно с третьими входами третьих групп И третьего и четвертого, первого и второго элементов И-ИЛИ-НЕ данной ячейки памяти, выходы второго и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, предпоследней и последней, соединены соответственно с третьими входами второй группы И третьего и четвертого и первого и второго элементов И-ИЛИ-НЕ данной ячейки памяти, выходы первого и второго элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, второй и последней, соединены с четвертыми входами соответственно третьих и вторых групп И третьего и четвертого элементов И-ИЛИ-НЕ предыдущей ячейки памяти, выходы четвертого и третьего элементов И-ИЛИ-НЕ каждой ячейки памяти, кроме первой, второй и последней, соединены с четвертыми входами соответственно третьих и вторых групп И первого и второго элементов И-ИЛИ-НЕ предылущей ячейки

памяти, выходы первого, второго, третьего и четвертого элементов И-ШБ-1-НЕ первой ячейки памяти соединены соответственно с вторыми входами вторых групп И ее второго, первого, четвертого и третьего элементов И-ИЛИ-НЕ, вторые входы первых групп И первого и второго элементов И-ИЛИ-НЕ первой ячейки памяти и пятые входы вторых и третьих групп И первого и второго элементов И-ИЛИ-НЕ второй ячейки памяти являются прямым информационным входом регистра, а соответствующие входы третьего и четвертого элементов И-11ПИ- НЕ первой ячейки памяти и третьего и четвертого элементов И-ИЛИ-НЕ второй ячейки памяти являются инверсным информационным входом регистра, третьи входы вторых групп И элементов И-ИЛИНЕ предпоследней ячейки памяти и вторые входы первых групп И элементов И-ИЛИ-НЕ последней ячейки памяти являются управляющим входом регистра, выходы первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ последней ячейки памяти соединены соответственно с вторыми входами первых групп И ее второго, первого, четвертого и третьего элементов И-ИЛИ-НЕ, регистр содержит три дополнительных элемента И-ИЛИ-НЕ, первые и вторые входы первой, второй, третьей и четвертой групп И первого из которых соединены соответственно с выходами первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ первой и второй ячеек памяти, а выход является управляющим выходом регистра, выходы второго и третьего дополнительных элементов И-ИЛИ-НЕ являются соответственно прямым и инверсным информационными выходами pei-истра, первые входы первой и второй групп И соединены соответственпг. с выходам первого и второго и третьего и четвертого элементов И-ИЛИ-НЕ последней ячейки памяти, а вторые входы - с выходами второго и первого и четвертого и третьего элементов И-ИЛИ-ПЕ предпослелие ячейки памяти.

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-07—Публикация

1985-12-02—Подача