оо

lN3

00 О5 hO

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многразрядных сдвиговых регистров.

Целью изобретения является упрощение устройства.

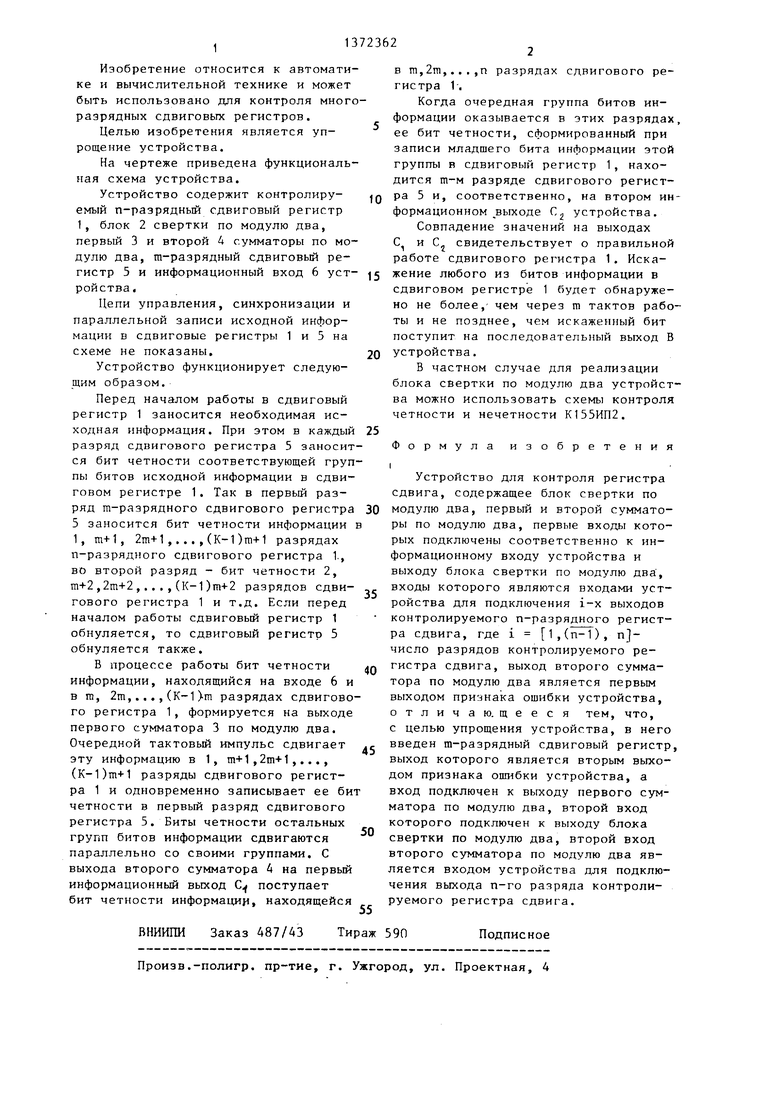

На чертеже приведена функциональная схема устройства.

Устройство содержит контролируемый п-разрядный сдвиговый регистр 1, блок 2 свертки по модулю два, первый 3 и второй А сумматоры по модулю два, т-разрядный сдвиговый регистр 5 и информационный вход 6 устройства ,

Цепи управления, синхронизации и параллельной записи исходной информации в сдвиговые регистры 1 и 5 на схеме не показаны.

Устройство функционирует следующим образом.

Перед началом работы в сдвиговый регистр 1 заносится необходимая исходная информация. При этом в кажды разряд сдвигового регистра 5 заносися бит четности соответствующей групы битов исходной информации в сдвиговом регистре 1. Так в первый разряд т-разрядного сдвигового регистр 5 заносится бит четности информации 1, т+1, 2т+1,...,(К-1)т+1 разрядах п-разрядного сдвигового регистра 1., во второй разряд - бит четности 2, т+2 ,2т+2 ,.. . , (К-1 )in-t-2 разрядов сдвигового регистра 1 и т.д. Если перед началом работы сдвиговый регистр 1 обнуляется, то сдвиговый регистр 5 обнуляется также.

В процессе работы бит четности информации, находящийся на входе 6 в га, 2т,...,(К-1)т разрядах сдвиговго регистра 1, формируется на выход первого сумматора 3 по модулю два. Очередной тактовый импульс сдвигает эту информацию в 1, т+1,2т+1,..., (К-1)т+1 разряды сдвигового регистра 1 и одновременно записывает ее б четности в первый разряд сдвигового регистра 5. Биты четности остальных групп битов информации сдвигаются параллельно со своими группами. С выхода второго сумматора А на первы информационный выход С поступает бит четности информации, находящейс

ВНИИПИ Заказ 487/43

Т

в m,2m,...,n разрядах сдвигового регистра 1.

Когда очередная группа битов информации оказывается в этих разрядах, ее бит четности, сформированный при записи младшего бита информации этой группы в сдвиговый регистр 1, находится т-м разряде сдвигового регист- ра 5 и, соответственно, на втором информационном выходе С2 устройства.

Совпадение значений на выходах

5

0

5

0

5

0

5

0

5

С и С. свидетельствует о правильной работе сдвигового регистра 1. Искажение любого из битов информации в сдвиговом регистре 1 будет обнаружено не более, чем через m тактов работы и не позднее, чем искаженный бит поступит на последовательный выход В устройства.

В частном случае для реализации блока свертки по модулю два устройства можно использовать схемы контроля четности и нечетности К155ИЦ2.

Формула изобретения

I

Устройство для контроля регистра сдвига, содержащее блок свертки по модулю два, первый и второй сумматоры по модулю два, первые входы которых подключены соответственно к информационному входу устройства и выходу блока свертки по модулю два , входы которого являются входами устройства для подключения i-x выходов контролируемого п-разрядного регистра сдвига, где i 1,(п-1), число разрядов контролируемого регистра сдвига, выход второго сумматора по модулю два является первьм выходом признака ошибки устройства, отличаю, щееся тем, что, с целью упрощения устройства, в него введен т-разрядный сдвиговый регистр, выход которого является вторым выходом признака ошибки устройства, а вход подключен к выходу первого сумматора по модулю два, второй вход которого подключен к выходу блока свертки по модулю два, второй вход второго сумматора по модулю два является входом устройства для подключения выхода п-го разряда контролируемого регистра сдвига.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в регистре сдвига | 1990 |

|

SU1756892A1 |

| Устройство для контроля блока сдвиговых регистров | 1985 |

|

SU1285478A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1978 |

|

SU746528A1 |

| Устройство для контроля вывода информации | 1977 |

|

SU658563A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Устройство для контроля регистраСдВигА | 1979 |

|

SU842968A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

Изобретение может быть использовано в антоматике и вычислительной технике для контроля многоразрядных сдвиговых регистров. Цель изобретения - упрощение устройстве. Поставленная цель достигается за счет того, что п разрядов сдвигаемого числа разбиваются на m групп по К разрядов в каждой (К n/m) и четность содержимого каждой группы разрядов контролируется отдельно, В одну группу объединяются разряды сдвигового регистра, номера которых имеют одинаковые остатки от деления на т, причем бит четности каждой группы хранится в разряде т-разрядного сдвигового регистра,номер которого равен соответствующему остатку. Бит четности сдвигается параллельно со сдвигаемой информацией, на выходах С, и С одновременно появляются суммг; по модулю два содержимого разрядов группы и его бит чатности. Несовпадение значенгш на выходах свидетельствует о наличии неисправности. Устройство содержит блок 2 свертки по модулю два, первый 3 и второй 4 сумматоры по модулю два, га-разрядный сдвиговый регистр 5. 1 ил. С (Л

| Селлерс TI | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Мир, 1972, с | |||

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

| Устройство для контроля регистраСдВигА | 1979 |

|

SU842968A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-18—Подача