(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1989 |

|

SU1656591A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Устройство управления блоками памяти | 1988 |

|

SU1562920A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Запоминающее устройство с контролем цепей обнаружения ошибок | 1985 |

|

SU1367046A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах обработки информации. Цель изобретения - повышение быстродействия устройства. Устройство содержит блоки памяти 1, дешифратор 2, элементы ИЛИ 3, элементы И 10, 11. Поставленная цель достигается за счет одновременной записи информации во все блоки памяти. 1 ил.

3Jf

со

00

со

4

4

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах обработки информации.

Цель изобретения - повышение быстродействия устройства.

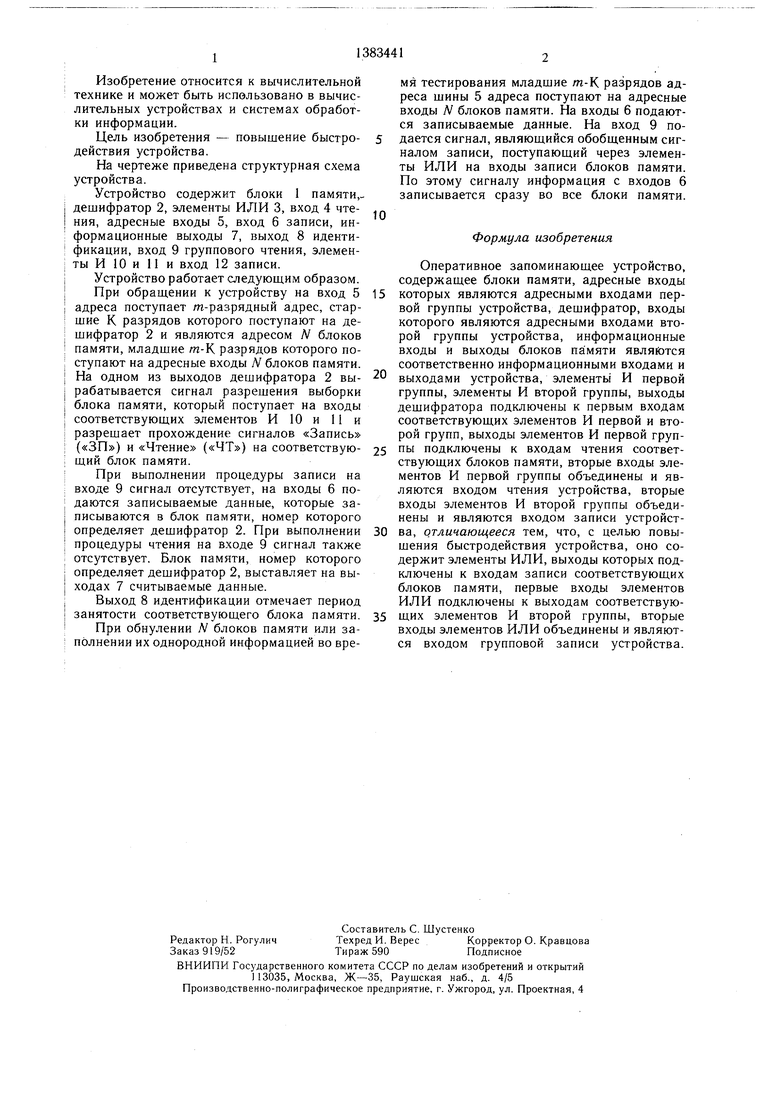

На чертеже приведена структурная схема устройства.

Устройство содержит блоки 1 памяти,- дешифратор 2, элементы ИЛИ 3, вход 4 чтения, адресные входы 5, вход 6 записи, информационные выходы 7, выход 8 идентификации, вход 9 группового чтения, элементы И 10 и 11 и вход 12 записи.

Устройство работает следующим образом.

При обращении к устройству на вход 5 адреса поступает т-разрядный адрес, старшие К разрядов которого поступают на де- щифратор 2 и являются адресом N блоков памяти, младшие т-К разрядов которого поступают на адресные входы Л блоков памяти. На одном из выходов дешифратора 2 вырабатывается сигнал разрешения выборки блока памяти, который поступает на входы соответствующих элементов И 10 и И и разрешает прохождение сигналов «Запись («ЗП) и «Чтение («ЧТ) на соответствующий блок памяти.

При выполнении процедуры записи на входе 9 сигнал отсутствует, на входы 6 подаются записываемые данные, которые записываются в блок памяти, номер которого определяет дешифратор 2. При выполнении процедуры чтения на входе 9 сигнал также отсутствует. Блок памяти, номер которого определяет дешифратор 2, выставляет на выходах 7 считываемые данные.

Выход 8 идентификации отмечает период занятости соответствующего блока памяти.

При обнулении Л блоков памяти или заполнении их однородной информацией во время тестирования младшие т-К. разрядов адреса шины 5 адреса поступают на адресные входы Л блоков памяти. На входы б подаются записываемые данные. На вход 9 подается сигнал, являющийся обобщенным сигналом записи, поступающий через элементы ИЛИ на входы записи блоков памяти. По этому сигналу информация с входов 6 записывается сразу во все блоки памяти.

Формула изобретения

Оперативное запоминающее устройство, содержащее блоки памяти, адресные входы

которых являются адресными входами первой группы устройства, дешифратор, входы которого являются адресными входами второй группы устройства, информационные входы и выходы блоков памяти являются соответственно информационными входами и

выходами устройства, элементь И первой группы, элементы И второй группы, выходы дешифратора подключены к первым входам соответствующих элементов И первой и второй групп, выходы элементов И первой группы подключены к входам чтения соответствующих блоков памяти, вторые входы элементов И первой группы объединены и являются входом чтения устройства, вторые входы элементов И второй группы объединены и являются входом записи устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элементы ИЛИ, выходы которых подключены к входам записи соответствующих блоков памяти, первые входы элементов ИЛИ подключены к выходам соответствующих элементов И второй группы, вторые входы элементов ИЛИ объединены и являются входом групповой записи устройства.

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Майоров С | |||

| А., Новиков Г | |||

| И | |||

| Принципы организации цифровых машин.-Л.: Машиностроение, 1974, с | |||

| Велосипед, приводимый в движение силой тяжести едущего | 1922 |

|

SU380A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1988-03-23—Публикация

1986-05-20—Подача