1

f

со 00 со д N ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки цифровой информации с уплотнением | 1987 |

|

SU1425632A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для задержки цифровой информации с контролем | 1987 |

|

SU1462424A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Последовательное буферное запоминающее устройство | 1986 |

|

SU1332383A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1383326A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено для задержки передаваемой информации в системах цифровой обработки данных. Целью изобретения является расширение области применения устройства путем обеспечения вывода данных как в прямой, так и в обратной последовательности. Устройство содержит счетчик 1 адреса, коммутатор 2, накопитель 3, счетный триггер 4, выходной регистр 5, вход 6 управления последовательностью выдачи данных, вход 7 синхронизации, информационные входы 8 и выходы 9. Устройство обеспечивает задержку передаваемых через накопитель 3 данных на время цикла адресов, определяемого установкой счетчика 1, при возможности в каждом цикле осуществлять чтение данных в обратной последовательности по отношению к последовательности их записи, что позволяет применять устройство, например, для быстрого преобразования Фурье. 2 ил.

/

/

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено для задержки передаваемой информации в системах цифровой обработки данных.

Цель изобретения - расширение области применения устройства путем обеспечения вывода данных как в прямой, так и в обратной последовательности.

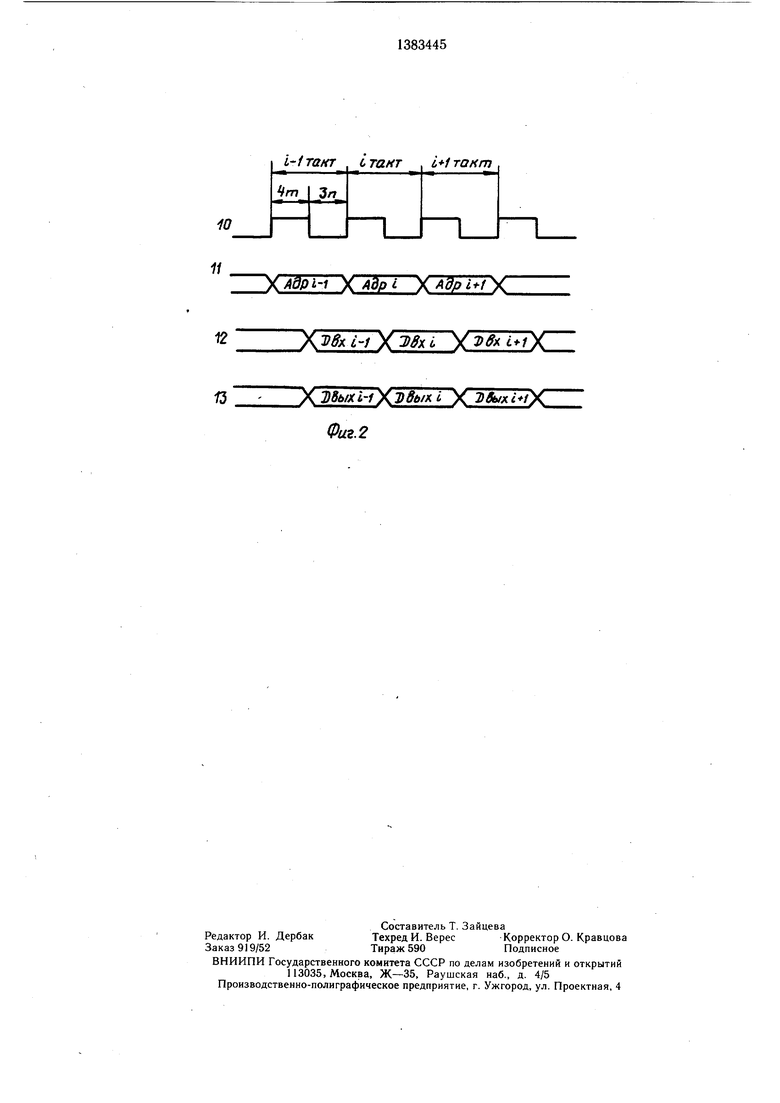

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг. 1) счетчик 1 адреса, коммутатор 2, накопитель 3, счетный триггер 4, выходной регистр 5, вход 6 управления последовательностью выдачи данных, вход 7 синхронизации, информационные входы 8 и выходы 9.

На фис. 2 изображены диаграммы синхроимпульсов 10 на входе 7, сигналов И на адресных входах накопителя 3, сигналов 12 на информационных входах 8 и сигналов 13 на выходах 9 устройства.

Устройство работает следующим образом.

В начальный момент времени происходит обнуление счетчика 1 (фиг. 1). Для организации прямой последовательности выдачи данных на вход 6 подают сигнал логического нуля. При этом триггер 4 удерживается в состоянии логического нуля и коммутатор 2 пропускает адрес с выходов счетчика 1 на адресные входы накопителя 3 без изменения.

Задержка поступающей на входы 8 информации при этом осуществляется следующим образом (фиг. 2).

Сигналы 12 поступают на входы 8, сопровождаясь синхроимпульсами 10 типа «меандр на входе 7, причем во время первой половины такта осуществляется чтение информации, записанной в ячейку накопителя 3 в предыдущем цикле задержки, а во время второй половины такта - запись информации в эту же ячейку, чтение из которой происходит в следующем цикле задержки. Счетчик 1 последовательно перебирает адреса, осуществляя запись слов, поступающих jia входы 8, в ячейки накопителя 3. За п тактов задержки все п слов оказываются последовательно записанными, а п слов предыдущего массива информации в таком же (прямом порядке - считанными из накопителя 3. Фиксация считанного слова в регистре 5 осуществляется задним фронтом синхроимпульсов на входе 7.

Если на вход 6 подают сигнал логической единицы, то триггер 4 не блокирует по своему R-йходу и в конце цикла прямой записи и чтения происходит выдача счет0

5

0

5

0

5

0

5

0

чиком 1 сигнала конца предыдущего цикла, который переключает триггер 4 в состояние логической единицы. При этом коммутатор 2 переключает адресные выходы счетчика 1 таким образом, что вместо адресов Со, GI, 02,...., um-i на адресные входы накопителя 3 поступают адреса ..., а, О, ао.

Во время следующего цикла задержки происходит выдача в обратном порядке формации, записанной в предыдущем цикле (цикле чтения и записи в прямом порядке). В конце цикла занесения информации в обратном порядке снова происходит инвертирование триггера 4. Коммутатор 2 снова пропускает адреса в прямом порядке, при этом снова происходит чтение и запись в прямой последовательности.

Таким образом, постоянно осуществляется чтение в прямой последовательности информации, записанной в обратной последовательности, или чтение в прямой последовательности информации, записанной в предыдущем цикле в обратной последовательности, т. е. в каждом цикле осуществляется чтение информации в обратной (по отношению к последователности записи) последовательности, что позволяет применять устройство для рещения задач цифровой обработки данных.

Формула изобретения

Устройство для задержки цифровой информации, содержащее накопител-ь-счетчик адреса и выходной регистр, выходы которого являются выходами устройства, причем информационные выходы накопителя соединены с информационными входами выходного регистра, управляющий вход которого, вход записи-чтения накопителя и счетный вход счетчика адреса объединены и являются входом синхронизации устройства, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения вывода данных как в прямой, так и в обратной последовательности, в устройство введены счетный триггер и коммутатор, управляющий вход которого подключен к выходу счетного триггера, счетный вход которого соединен с выходом переполнения счетчика адреса, разрядные выходы которого подключены к информационным входам коммутатора, выходы которого соединены с адресными входами накопителя, информационные входы которого являются информационными входами устройства, причем вход блокировки счетного триггера является входом управления последовательностью выдачи данных устройства.

i-/ ra/fT L такт такт

Чт 3/7

10 11

Adf)i-t XAdpi ХАдрПТУ:

12

lfffxi-fyC xi.

iS

DSb/x i-1 X 2 I X 2 л i / Фиг.2

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программируемой задержки информации | 1984 |

|

SU1193653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-13—Подача