со оо о i

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля сохранности информации в блоках постоянной памяти.

Цель изобретения - повышение глубины диагностирования ошибок.

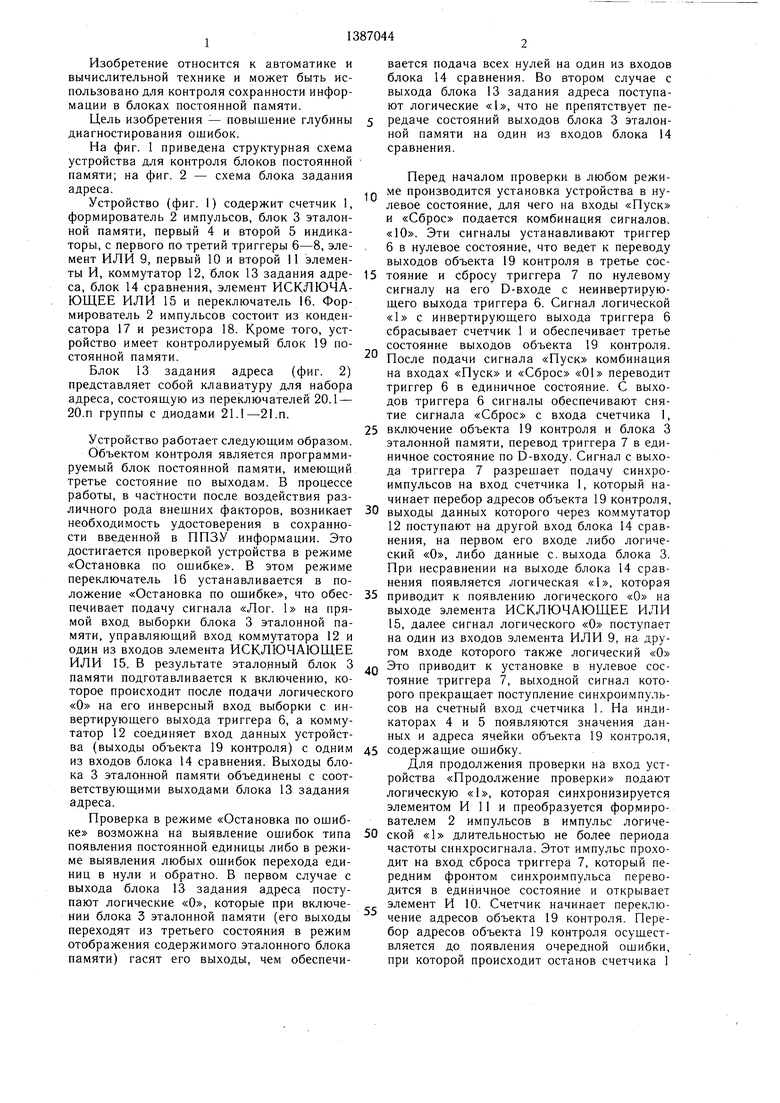

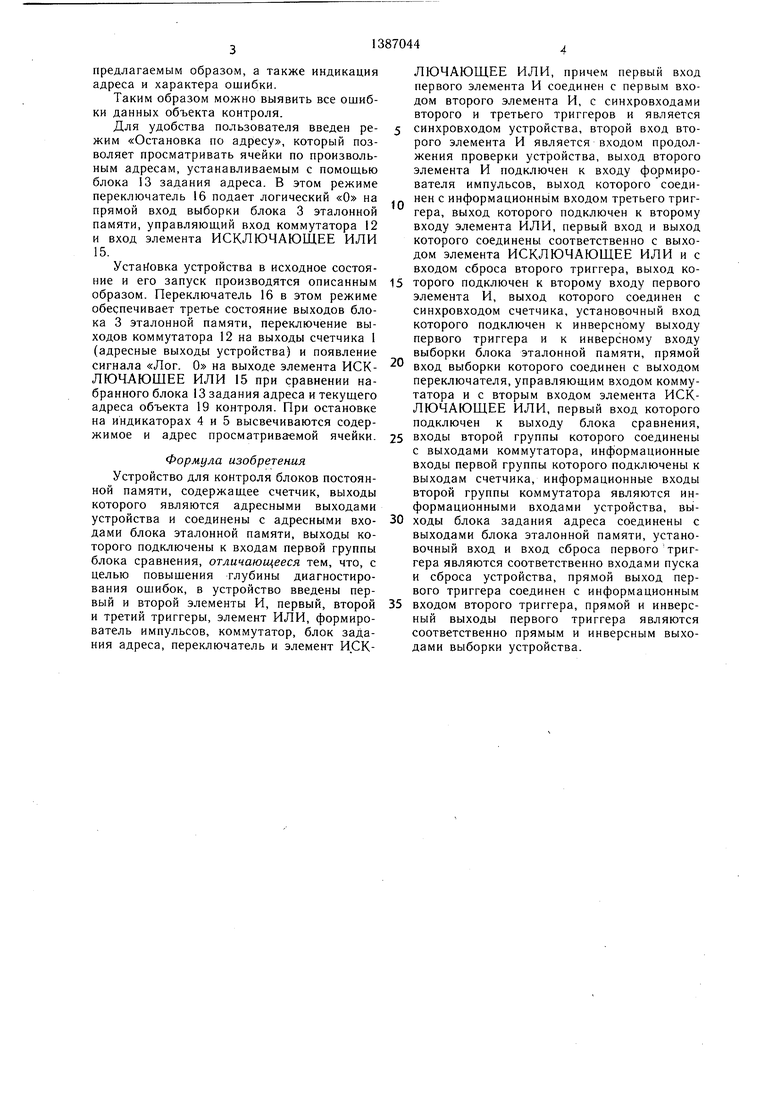

На фиг. 1 приведена структурная схема устройства для контроля блоков постоянной памяти; на фиг. 2 - схема блока задания адреса.

Устройство (фиг. 1) содержит счетчик 1, формирователь 2 импульсов, блок 3 эталонной памяти, первый 4 и второй 5 индикаторы, с первого по третий триггеры 6-8, элемент ИЛИ 9, первый 10 и второй 11 элементы И, коммутатор 12, блок 13 задания адреса, блок 14 сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и переключатель 16. Формирователь 2 импульсов состоит из конденсатора 17 и резистора 18. Кроме того, устройство имеет контролируемый блок 19 постоянной памяти.

Блок 13 задания адреса (фиг. 2) представляет собой клавиатуру для набора адреса, состоящую из переключателей 20.1 - 20.п группы с диодами 21.1-21.п.

Устройство работает следующим образом.

Объектом контроля является программируемый блок постоянной памяти, имеющий третье состояние по выходам. В процессе работы, в частности после воздействия различного рода внешних факторов, возникает необходимость удостоверения в сохранности введенной в ППЗУ информации. Это достигается проверкой устройства в режиме «Остановка по ощибке. В этом режиме переключатель 16 устанавливается в положение «Остановка по ошибке, что обеспечивает подачу сигнала «Лог. 1 на прямой вход выборки блока 3 эталонной памяти, управляющий вход коммутатора 12 и один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15. В результате эталонный блок 3 памяти подготавливается к включению, которое происходит после подачи логического «О на его инверсный вход выборки с инвертирующего выхода триггера 6, а коммутатор 12 соединяет вход данных устройства (выходы объекта 19 контроля) с одним из входов блока 14 сравнения. Выходы блока 3 эталонной памяти объединены с соответствующими выходами блока 13 задания адреса.

Проверка в режиме «Остановка по ощибке возможна на выявление ошибок типа появления постоянной единицы либо в режиме выявления любых ошибок перехода единиц в нули и обратно. В первом случае с выхода блока 13 задания адреса поступают логические «О, которые при включении блока 3 эталонной памяти (его выходы переходят из третьего состояния в режим отображения содержимого эталонного блока памяти) гасят его выходы, чем обеспечивается подача всех нулей на один из входов блока 14 сравнения. Во втором случае с выхода блока 13 задания адреса поступают логические «Ь, что не препятствует пе- редаче состояний выходов блока 3 эталонной памяти на один из входов блока 14 сравнения.

Перед началом проверки в любом режи ме производится установка устройства в нулевое состояние, для чего на входы «Пуск и «Сброс подается комбинация сигналов. «10. Эти сигналы устанавливают триггер 6 в нулевое состояние, что ведет к переводу выходов объекта 19 контроля в третье состояние и сбросу триггера 7 по нулевому сигналу на его D-входе с неинвертирующего выхода триггера 6. Сигнал логической «1 с инвертирующего выхода триггера 6 сбрасывает счетчик 1 и обеспечивает третье состояние выходов объекта 19 контроля.

После подачи сигнала «Пуск комбинация на входах «Пуск и «Сброс «01 переводит триггер 6 в единичное состояние. С выходов триггера 6 сигналы обеспечивают снятие сигнала «Сброс с входа счетчика 1,

5 включение объекта 19 контроля и блока 3 эталонной памяти, перевод триггера 7 в единичное состояние по D-входу. Сигнал с выхода триггера 7 разрешает подачу синхроимпульсов на вход счетчика 1, который начинает перебор адресов объекта 19 контроля,

0 выходы данных которого через коммутатор 12 поступают на другой вход блока 14 сравнения, на первом его входе либо логический «О, либо данные с. выхода блока 3. При несравнении на выходе блока 14 сравнения появляется логическая «1, которая

5 приводит к появлению логического «О на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, далее сигнал логического «О поступает на один из входов элемента ИЛИ 9, на другом входе которого также логический «О

Q Это приводит к установке в нулевое состояние триггера 7, выходной сигнал которого прекращает поступление синхроимпульсов на счетный вход счетчика 1. На индикаторах 4 и 5 появляются значения данных и адреса ячейки объекта 19 контроля,

5 содержащие ощибку.

Для продолжения проверки на вход устройства «Продолжение проверки подают логическую «Ь, которая синхронизируется элементом И 11 и преобразуется формирователем 2 импульсов в импульс логиче0 ской «1 длительностью не более периода частоты синхросигнала. Этот импульс проходит на вход сброса триггера 7, который передним фронтом синхроимпульса переводится в единичное состояние и открывает элемент И 10. Счетчик начинает переключение адресов объекта 19 контроля. Перебор адресов объекта 19 контроля осуществляется до появления очередной ошибки, при которой происходит останов счетчика 1

предлагаемым образом, а также индикация адреса и характера ошибки.

Таким образом можно выявить все ошибки данных объекта контроля.

Для удобства пользователя введен режим «Остановка по адресу, который позволяет просматривать ячейки по произвольным адресам, устанавливаемым с помош,ью блока 13 задания адреса. В этом режиме переключатель 16 подает логический «О на прямой вход выборки блока 3 эталонной памяти, управляюш,ий вход коммутатора 12 и вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15.

Установка устройства в исходное состояние и его запуск производятся описанным образом. Переключатель 16 в этом режиме обеспечивает третье состояние выходов блока 3 эталонной памяти, переключение выходов коммутатора 12 на выходы счетчика 1 (адресные выходы устройства) и появление сигнала «Лог. О на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 при сравнении набранного блока 13 задания адреса и текущего адреса объекта 19 контроля. При остановке на индикаторах 4 и 5 высвечиваются содержимое и адрес просматриваемой ячейки.

Формула изобретения Устройство для контроля блоков постоянной памяти, содержаш,ее счетчик, выходы которого являются адресными выходами устройства и соединены с адресными входами блока эталонной памяти, выходы которого подключены к входам первой группы блока сравнения, отличающееся тем, что, с целью повышения глубины диагностирования ошибок, в устройство введены первый и второй элементы И, первый, второй и третий триггеры, элемент ИЛИ, формирователь импульсов, коммутатор, блок задания адреса, переключатель и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход первого элемента И соединен с первым входом второго элемента И, с синхровходами второго и третьего триггеров и является

синхровходом устройства, второй вход второго элемента И является входом продолжения проверки устройства, выход второго элемента И подключен к входу формирователя импульсов, выход которого соеди нен с информационным входом третьего триггера, выход которого подключен к второму входу элемента ИЛИ, первый вход и выход которого соединены соответственно с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом сброса второго триггера, выход которого подключен к второму входу первого элемента И, выход которого соединен с синхровходом счетчика, установочный вход которого подключен к инверсному выходу первого триггера и к инверсному входу выборки блока эталонной памяти, прямой

вход выборки которого соединен с выходом переключателя, управляющим входом коммутатора и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого подключен к выходу блока сравнения,

5 входы второй группы которого соединены с выходами коммутатора, информационные входы первой группы которого подключены к выходам счетчика, информационные входы второй группы коммутатора являются информационными входами устройства, вы0 ходы блока задания адреса соединены с выходами блока эталонной памяти, установочный вход и вход сброса первого триггера являются соответственно входами пуска и сброса устройства, прямой выход первого триггера соединен с информационным

5 входом второго триггера, прямой и инверсный выходы первого триггера являются соответственно прямым и инверсным выходами выборки устройства.

Син:( о-

Ю

Адрес

y/rfl.wS. i,

п

//7р.

79

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для контроля блоков постоянной памяти | 1990 |

|

SU1795522A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Система управления технологическим процессом дискретного производства | 1984 |

|

SU1251110A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля деятельности оператора | 1984 |

|

SU1203573A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля сохранности информации в блоках постоянной памяти. Целью изобретения является повышение глубины диагностирования ошибок. Устройство содержит блок эталонной памяти, счетчик, формирователь импульсов, блок задания адреса, блок сравнения, коммутатор, переключатель, триггеры, элементы И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, индикаторы. Цель изобретения достигается реализацией в устройстве режимов остановки по ошибке и остановки по заданному адресу. Устройство позволяет последовательно выявлять адреса всех ошибок, имеющихся в контролируемом блоке постоянной памяти. 2 ил.

, Пуск - о CSfloc

п

pffl

/7 U k..ll

фигЛ

го. 2

Ш

fS

Редактор А. Козориз Заказ 1225/50

Составитель О. Исаев

Техред И. ВересКорректор Л. Пилипенко

Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Hetff.

П

Пл

-

4 f

/п

лог:о

-э

| Устройство для контроля постоянной памяти | 1979 |

|

SU769640A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля постоянных блоков памяти | 1980 |

|

SU982097A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-07—Публикация

1986-04-17—Подача