00 00 00

со ел

Изобретение относится к вычислительной технике и может использоваться для контроля блоков .памяти большой разрядности.

Целью изобретения является повышение достоверности контроля блоков памяти, информационная разрядность которых превышает удвоенную разрядность кода адреса.

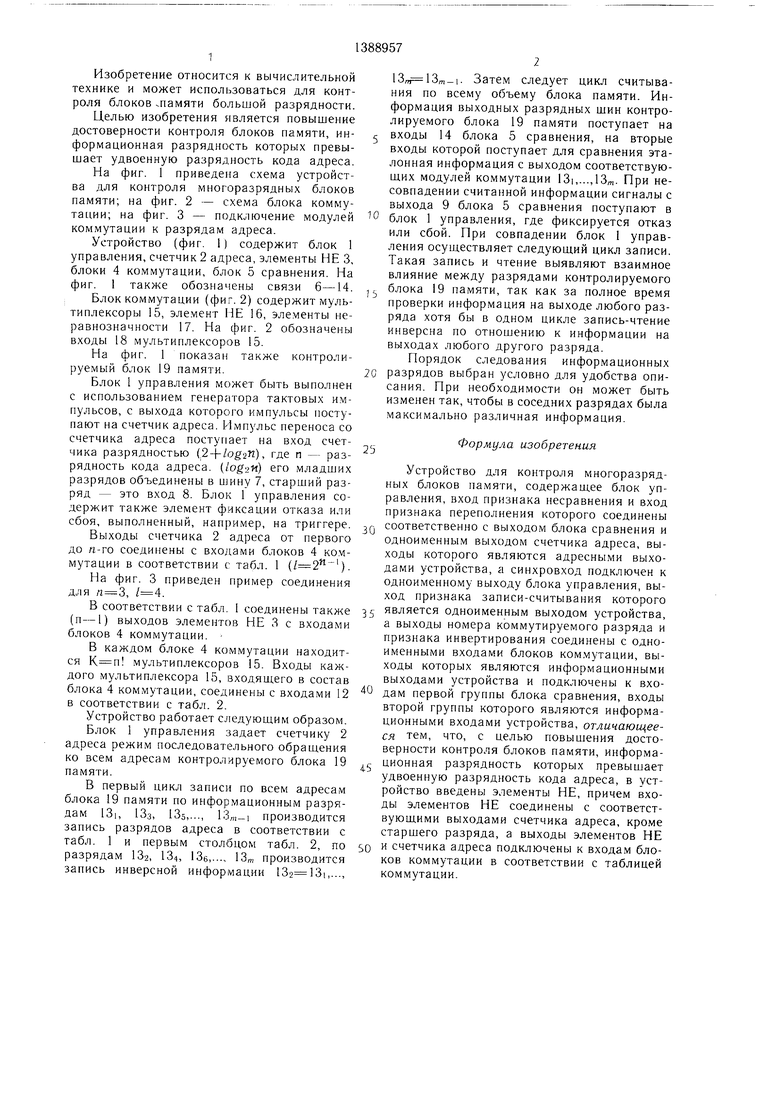

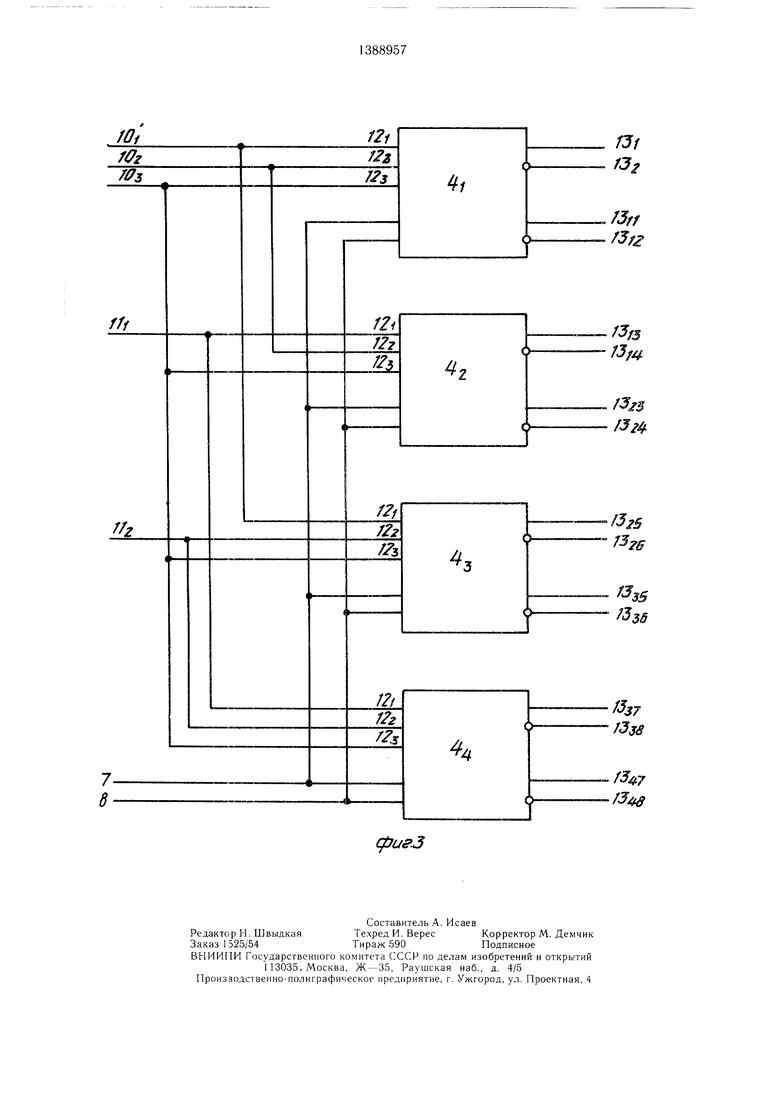

На фиг. 1 приведена схема устройства для контроля многоразрядных блоков памяти; на фиг. 2 - схема блока коммутации; на фиг. 3 - подключение модулей коммутации к разрядам адреса.

Устройство (фиг. 1) содержит блок 1 управления, счетчик 2 адреса, элементы НЕ 3, блоки 4 коммутации, блок 5 сравнения. На фиг. 1 также обозначены связи 6-14.

Блок коммутации (фиг. 2) содержит мультиплексоры 15, элемент НЕ 16, элементы неравнозначности 17. На фиг. 2 обозначены входы 18 мультиплексоров 15.

На фиг. 1 показан также контролируемый блок 19 памяти.

Блок 1 управления может быть выполнен с использованием генератора тактовых импульсов, с выхода которого импульсы поступают на счетчик адреса. Импульс переноса со счетчика адреса поступает на вход счетчика разрядностью (.2-j-/og2K), где п - разрядность кода адреса, (/ogaw) его младших разрядов объединены в шину 7, старший разряд - это вход 8. Блок 1 управления содержит также элемент фиксации отказа или сбоя, выполненный, например, на триггере.

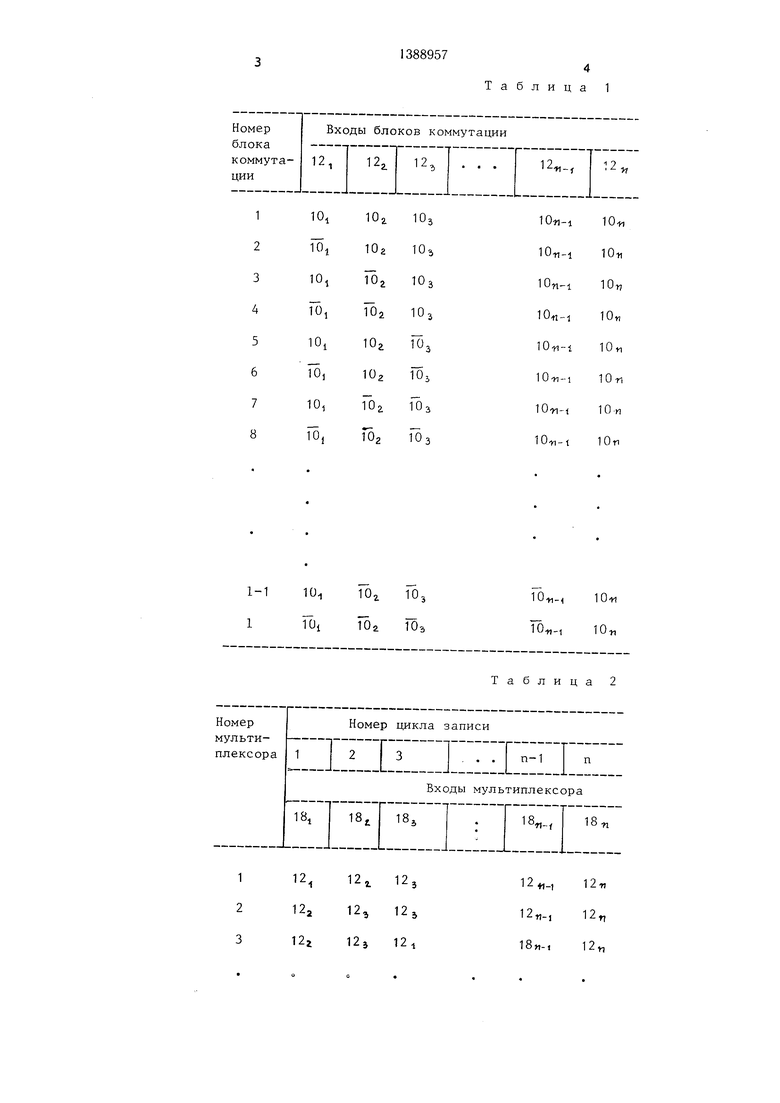

Выходы счетчика 2 адреса от первого до л-го соединены с входами блоков 4 коммутации в соответствии с табл. 1 ().

На фиг. 3 приведен пример соединения для , .

В соответствии с табл. 1 соединены также (п-1) выходов элементов НЕ 3 с входами блоков 4 коммутации.

В каждом блоке 4 коммутации находится мультиплексоров 15. Входы каждого мультиплексора 15, входящего в состав блока 4 коммутации, соединены с входами 12 в соответствии с табл. 2.

Устройство работает следующим образом.

Блок 1 управления задает счетчику 2 адреса режим последовательного обращения ко всем адресам контролируемого блока 19 памяти.

В первый цикл записи по всем адресам блока 19 памяти по информационным разрядам 13i, 13з, 135,..., 13m-i производится запись разрядов адреса в соответствии с табл. 1 и первым столбцом табл. 2, по разрядам 132, 134, 13б,..., 13т производится запись инверсной информации 132 13i,...,

Затем следует цикл считывания по всему объему блока памяти. Информация выходных разрядных шин контролируемого блока 19 памяти поступает на входы 14 блока 5 сравнения, на вторые входы которой поступает для сравнения эталонная информация с выходом соответствующих модулей коммутации 13i,...,13m. При несовпадении считанной информации сигналы с выхода 9 блока 5 сравнения поступают в

0 блок 1 управления, где фиксируется отказ или сбой. При совпадении блок 1 управления осуществляет следующий цикл записи. Такая запись и чтение выявляют взаимное влияние между разрядами контролируемого блока 19 памяти, так как за полное время проверки информация на выходе любого разряда хотя бы в одном цикле запись-чтение инверсна по отношению к информации на выходах любого другого разряда.

Порядок следования информационных

0 разрядов выбран условно для удобства описания. При необходимости он может быть изменен так, чтобы в соседних разрядах была максимально различная информация.

5

25

Формула изобретения

Устройство для контроля многоразрядных блоков памяти, содержащее блок управления, вход признака несравнения и вход признака переполнения которого соединены

Q соответственно с выходо.м блока сравнения и одноименным выходом счетчика адреса, выходы которого являются адресными выходами устройства, а синхровход подключен к одноименному выходу блока управления, выход признака записи-считывания которого

J является одноименным выходом устройства, а выходы номера коммутируемого разряда и признака инвертирования соединены с одноименными входами блоков коммутации, выходы которых являются информационными выходами устройства и подключены к вхо дам первой группы блока сравнения, входы второй группы которого являются информационными входами устройства, отличающееся тем, что, с целью повышения достоверности контроля блоков памяти, информаg ционная разрядность которых превышает удвоенную разрядность кода адреса, в устройство введены элементы НЕ, причем входы элементов НЕ соединены с соответствующими выходами счетчика адреса, кроме старшего разряда, а выходы элементов НЕ

0 и счетчика адреса подключены к входам блоков коммутации в соответствии с таблицей коммутации.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1989 |

|

SU1735907A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков памяти большой разрядности. Целью изобретения является повышение достоверности контроля блоков памяти, информационная разрядность которых превышает удвоенную разрядность кода адреса. Устройство содержит блок управления, счетчик адреса, элементы НЕ, блоки коммутации и блок сравнения. Достижение цели изобретения обусловлено наличием в устройстве блоков коммутации (п-раз- рядность кода адреса), коммутирующих разряды адреса на информационные выходы устройства таким образом, что за полное время проверки информация на выходе любого разряда хотя бы в одном цикле теста будет инверсна по отношению к информации на выходах любого другого разряда, чем обеспечивается полная проверка взаимовлияния разрядов контролируемого блока памяти. 3 ил., 2 табл. 5S

1-110 lOi Юз

lOjЮг Ю;

112,

2122

312г

Ю. Ю-и T0t,-i Ю«

Таблица 2

12з 125 12,

12 t,-, 12 я 12t,-, 12г, 18и-, 12г,

1

12

12,

12, 12

12и-1

Продолжение табл. 2

12,12

12„12,

12,

12,

.г

Wi

fOz

Г03

fff

Иг

7- 8

1

f3f /J/

/J// AJ/Z

/%

/J/4

/J/«

VJ/5

r

/Jji

./J«7 /J

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-15—Публикация

1986-04-07—Подача