со- со

4 Ю

Изобретение относится к вычислительной технике и может использовано при проектировании микропроцессорных систем и микропроцессорных устройств.

Делью изобретения является увеличение быстродействия устройства.

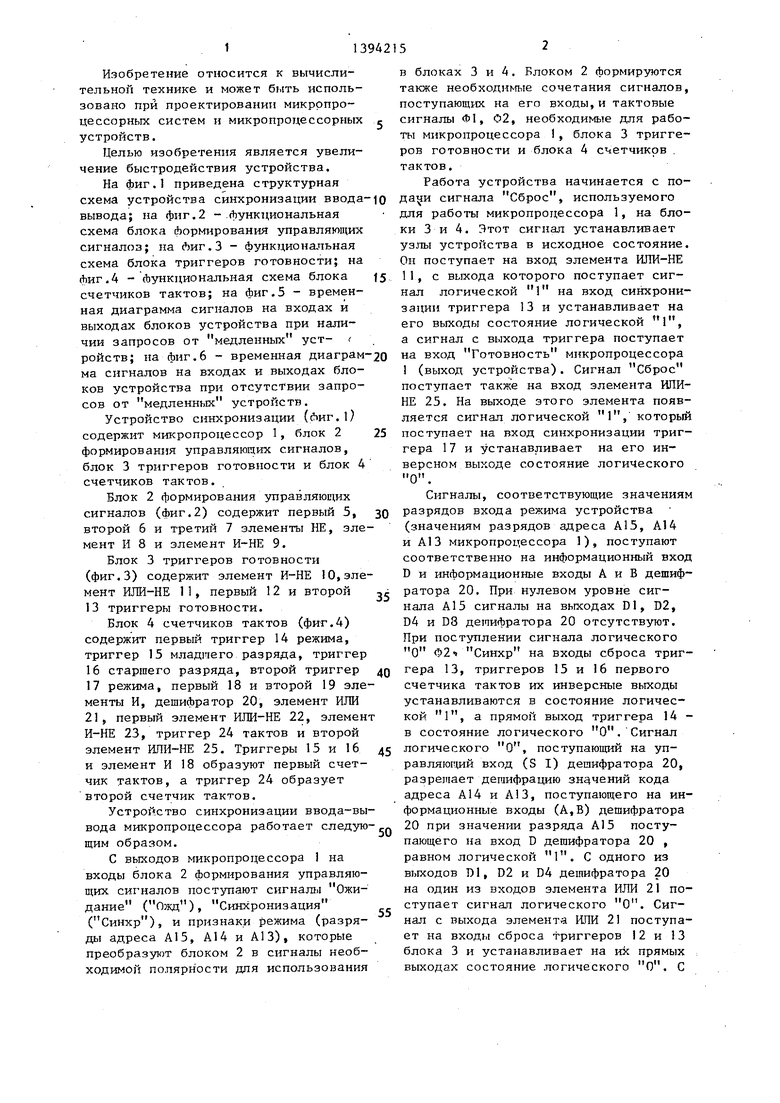

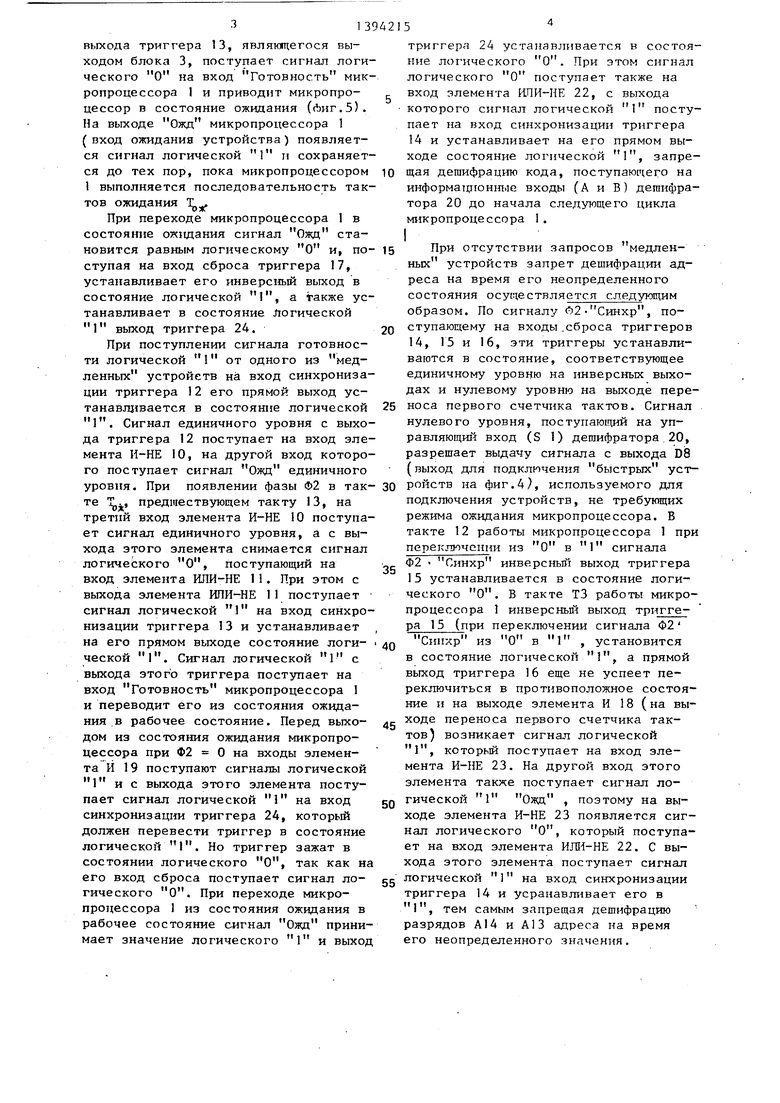

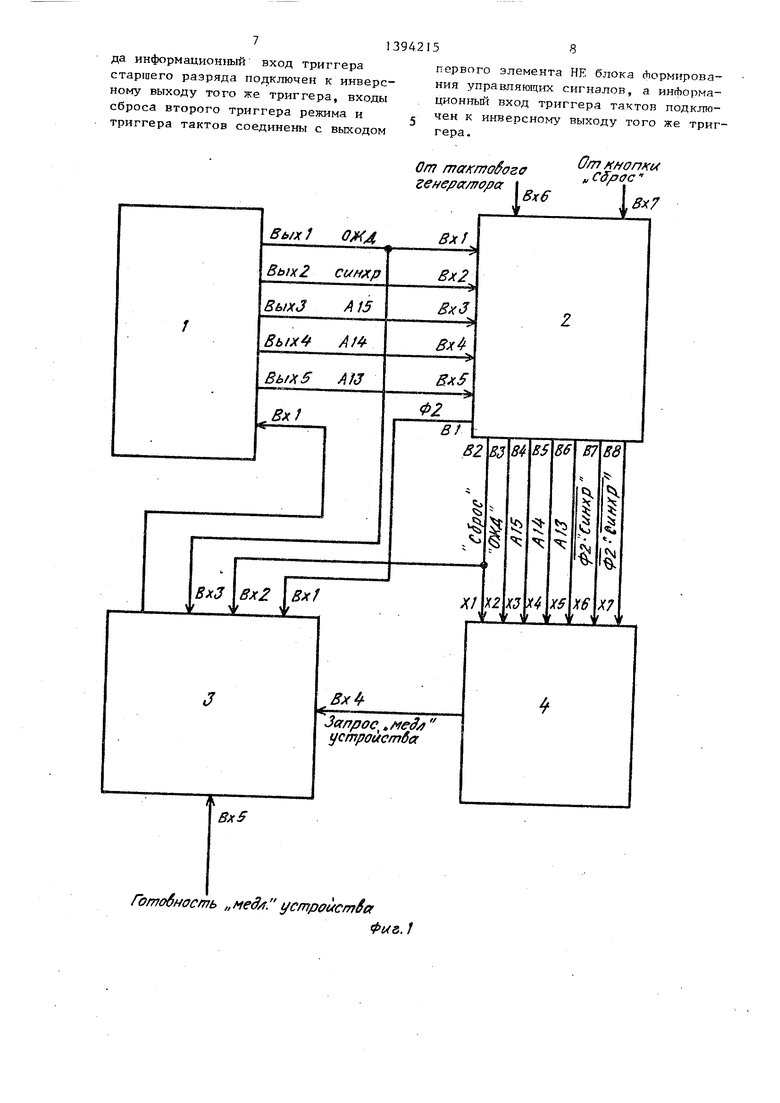

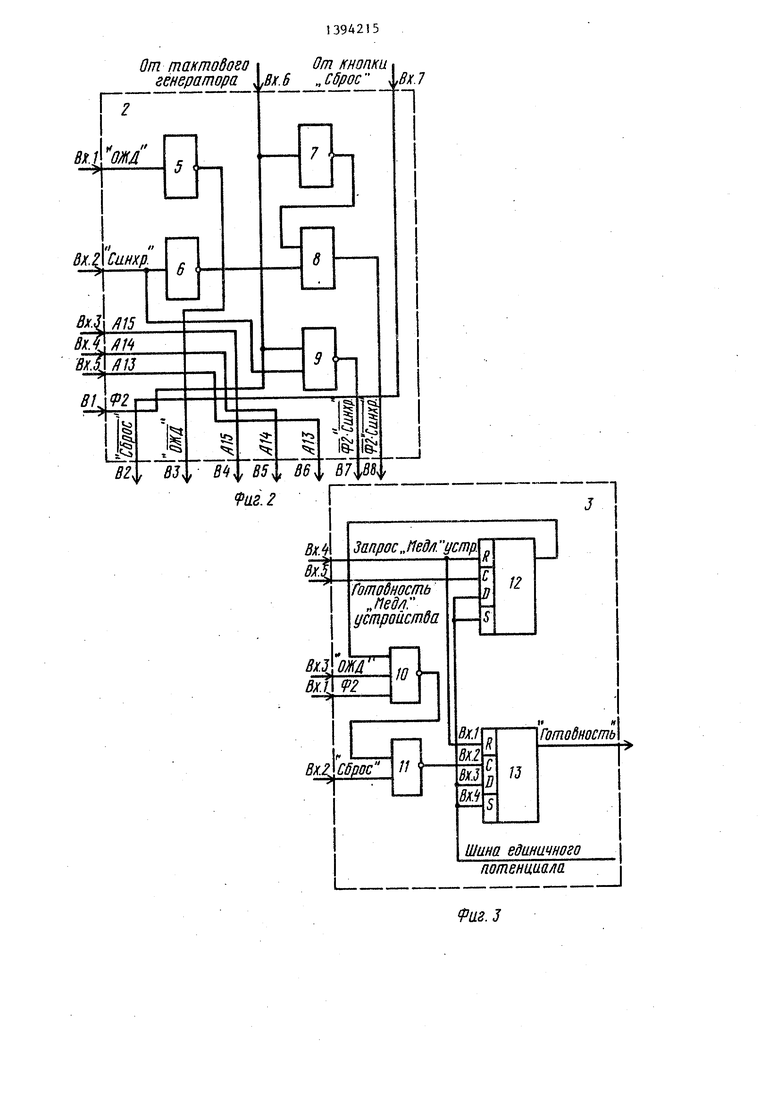

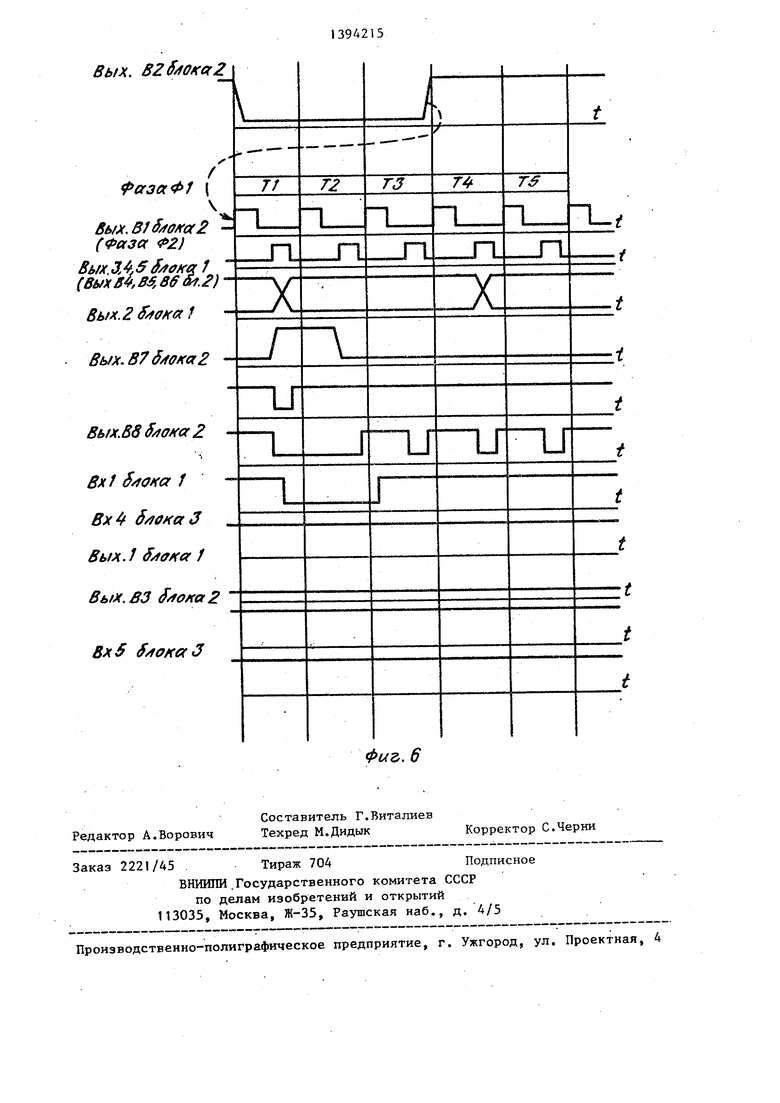

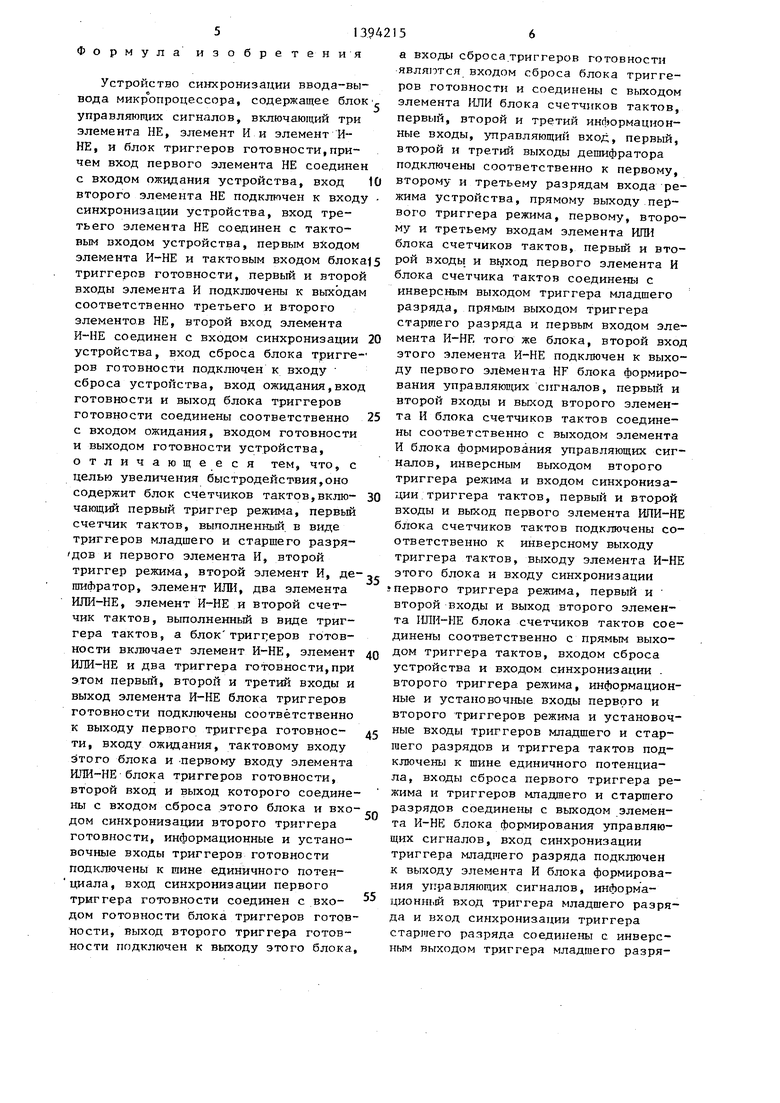

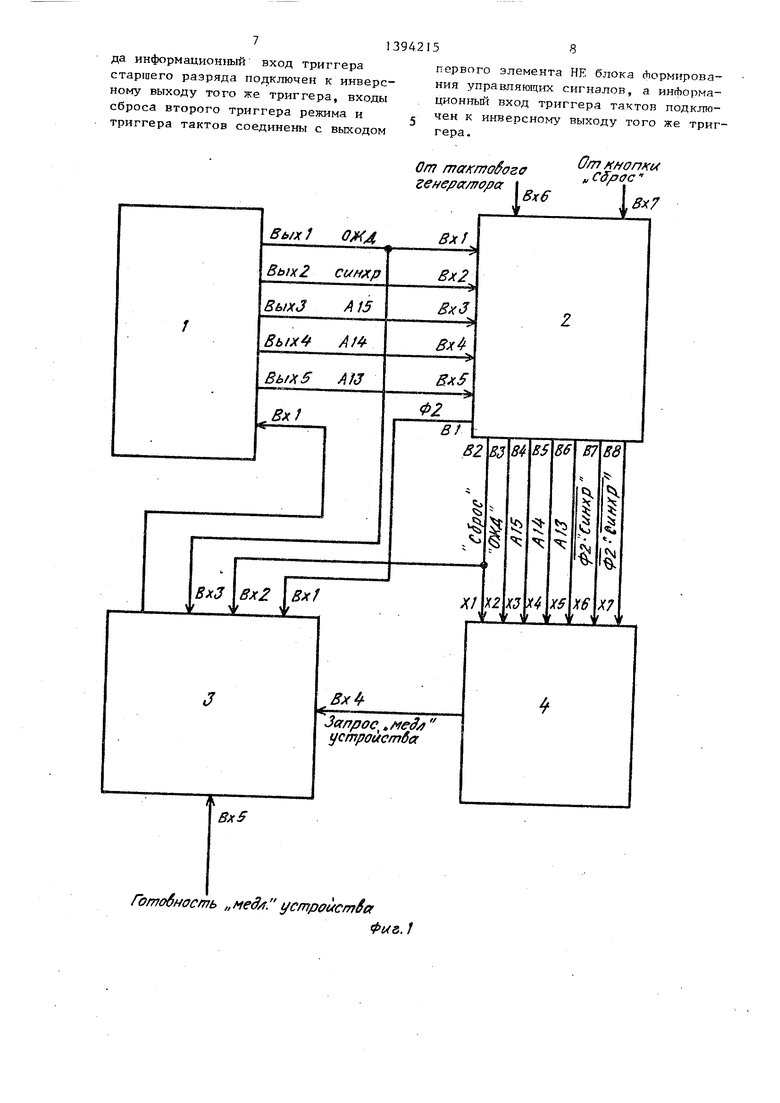

На фиг.1 приведена структурная схема устройства синхронизации ввода вывода; на фиг.2 -.функциональная схема блока формирования управляющих сигналов; на Фиг.З - фунюдиональная схема блока триггеров готовности; на фиг.А - функциональная схема блока счетчиков тактов; на фиг.5 - временная диаграмма сигналов на входах и выходах блоков устройства при наличии запросов от медленных уст- с ройств; на фиг.6 - временная диаграм на сигналов на входах и выходах блоков устройства при отсутствии запросов от медленных устройств.

Устройство синхронизации (биг.1) содержит микропроцессор 1, блок 2 формирования управляющих сигналов, блок 3 триггеров готовности и блок 4 счетчиков тактов.

Блок 2 формирования управляющих сигналов (фиг.2) содержит первый 5, второй 6 и третий 7 элементы НЕ, элемент И 8 и элемент И-НЕ 9.

Блок 3 триггеров готовности (фиг.З) содержит элемент И-НЕ 10,элемент ИЛИ-НЕ 11, первый 12 и второй 13 триггеры готовности.

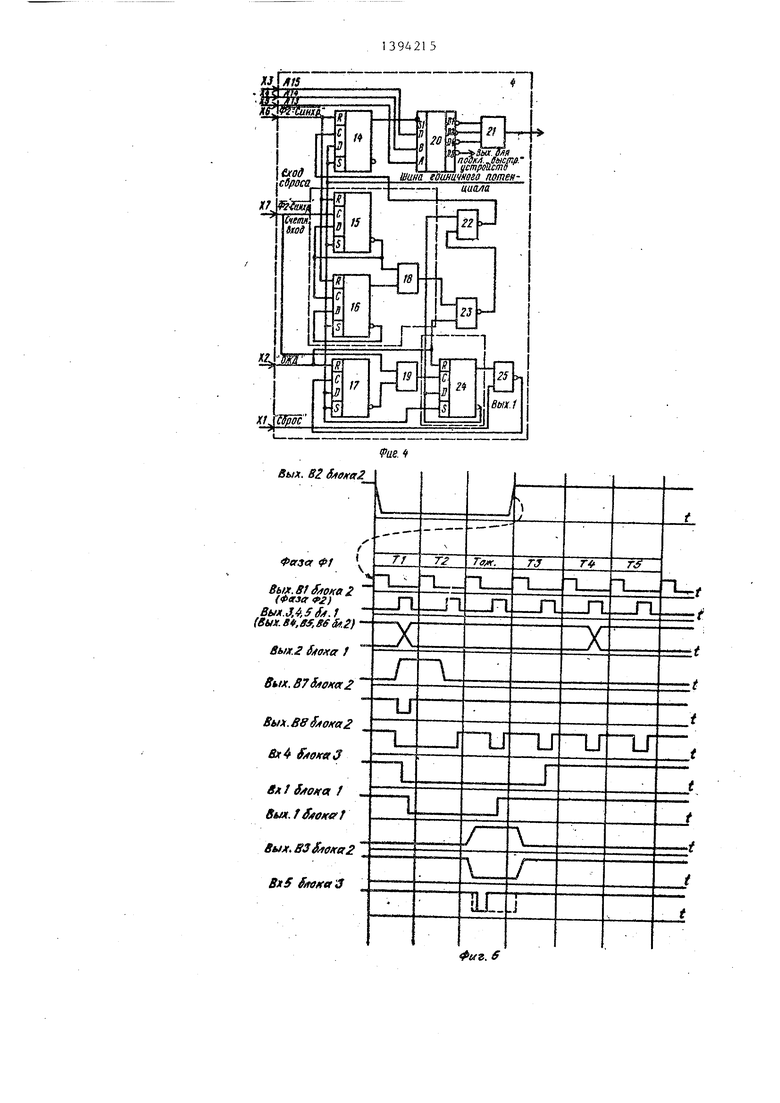

Блок 4 счетчиков тактов (фиг.4) содержит первый триггер 14 режима, триггер 15 младпего разряда, триггер

16старшего разряда, второй триггер

17режима, первый 18 и второй 19 элементы И, дешифратор 20, элемент ИЛИ 21, первый элемент ИЛИ-НЕ 22, элемен И-НЕ 23, триггер 24 тактов и второй элемент ИЛИ-НЕ 25. Триггеры 15 и 16 и элемент И 18 образуют первый счетчик тактов, а триггер 24 образует второй счетчик тактов.

Устройство синхронизации ввода-вывода микропроцессора работает следующим образом.

С выходов микропроцессора 1 на входы блока 2 формирования управляющих сигналов поступают сигнал}. Ожидание (Ожд), Синхронизация (Синхр), и признаки режима (разряды адреса А15, А14 и А13), которые преобразуют блоком 2 в сигналы необходимой полярн ости для использования

О

с

о

5

0

5

в блоках 3 и 4. Блоком 2 формируются также нeoбxoди ыe сочетания сигналов, поступающих на его входы,и тактовые сигналы Ф1, 02, необходимые для работы микропроцессора 1, блока 3 триггеров готовности и блока 4 счетчиков . тактов.

Работа устройства начинается с подари сигнала Сброс, используемого для работы микропроцессора 1, на блоки 3 и 4. Зтот сигнал устанавливает узлы устройства в исходное состояние. Он поступает на вход элемента ИЛИ-НЕ 11, с выхода которого поступает сигнал логической 1 на вход синхронизации триггера 13 и устанавливает на его выходы состояние логической I, а сигнал с выхода триггера поступает на вход Готовность микропроцессора 1 (выход устройства). Сигнал Сброс поступает также на вход элемента ИПИ- НЕ 25. На выходе этого элемента появляется сигнал логической 1, который поступает на вход синхронизации триггера 17 и устанавливает на его инверсном выходе состояние логического О.

Сигналы, соответствующие значениям разрядов входа режима устройства (значениям разрядов адреса А15, А14 и А13 микропроцессора 1), поступают соответственно на информационный вход D и информационные входы А и Б дешифратора 20. При нулевом уровне сигнала А15 сигналы на выходах DI, D2, D4 и D8 дешифратора 20 отсутствуют. При поступлении сигнала логического О Ф2ч Синхр на входы сброса триггера 13, триггеров 15 и 16 первого счетчика тактов их инверсные выходы устанавливаются в состояние логической 1, а прямой выход триггера 14 - в состояние логического О. Сигнал логического О, поступающий на уп- равляюгций вход (S I) дешифратора 20, разрешает дешифрацию значений кода адреса А14 и А13, поступающего на информационные входы (А,Б) дешифратора 20 при значении разряда А15 поступающего на вход D дешифратора 20 , равном логической 1. С одного из выходов D1, D2 и D4 дешифратора 20 на один из входов элемента ИЛИ 21 поступает сигнал логического О. Сигнал с выхода элемента ИЛИ 2 поступает на входы сброса триггеров 12 и 13 блока 3 и устанавливает на их прямых выходах состояние логического О. С

313

выхода триггера 13, являкщегося выходом блока 3, поступает сигнал логического О на вход Готовность микропроцессора 1 и приводит микропро- цессор в состояние ожидания (Лиг.5). На выходе Ожд микропроцессора 1 ( вход ожидания устройства) появляется сигнал логической 1 и сохраняется до тех пор, пока микропроцессором 1 выполняется последовательность тактов ожидания Т

При переходе микропроцессора 1 в состояние ож1щания сигнал Ожд становится равным логическому О и, по- ступая на вход сброса триггера 17, устанавливает его инверсный выход в состояние логической 1, а гакже устанавливает в состояние логической 1 выход триггера 24.

При поступлении сигнала готовности логической 1 от одного из медленных устройств на вход синхронизации триггера 12 его прямой выход ус- танавл51вается в состояние логической 1. Сигнал единичного уровня с выхода триггера 12 поступает на вход элемента И-НЕ 10, на другой вход которого поступает сигнал Ожд единичного уровня. При появлении фазы Ф2 в так- те TJj.,, предшествующем такту 13, на третий вход элемента И-НЕ 10 поступает сигнал единичного уровня, а с выхода этого элемента снимается сигнал логического О, поступающий на вход элемента ИЛИ-НЕ 11. При этом с выхода элемента ИПИ-НЕ 11 поступает сигнал логической 1 на вход синхронизации триггера 13 и устанавливает на его прямом выходе состояние логи- ческой 1. Сигнал логической 1 с выхода этого триггера поступает на вход Готовность микропроцессора 1 и переводит его из состояния ожидания .в рабочее состояние. Перед выхо- дом из состояния ожидания микропроцессора при Ф2 О на входы элемента И 19 поступают сигналы логической 1 и с выхода этого элемента поступает сигнал логической 1 на вход синхронизации триггера 24, который должен перевести триггер в состояние логической 1. Но триггер зажат в состоянии логического О, так как на его вход сброса поступает сигнал ло- гического О. При переходе микропроцессора 1 из состояния ожидания в рабочее состояние сигнал Ожд принимает значение логического 1 и выход

триггера 24 устанавливается в состояние логического О. При этом сигнал логического О поступает также на вход элемента ИПИ-НЕ 22, с выхода которого сигнал логической 1 поступает на вход синхронизации триггера

14и устанавливает на его прямом выходе состояние логической 1, запрещая дешифрацию кода, поступающего на информац1ЮНШ)1е входы (А и В) дешифратора 20 до начала следующего цикла микропроцессора 1.

I

При отсутствии запросов медленных устройств запрет дешифрации адреса на время его неопределенного состояния осуществляется следующим образом. По сигналу й2- Синхр, поступающему на входы .сброса триггеров 14, 15 и 16, эти триггеры устанавливаются в состояние, соответствующее единичному уровню на инверсных выходах и нулевому уровню на выходе переноса первого счетчика тактов. Сигнал нулевого уровня, поступающий на управляющий вход (S 1) дешифратора.20, разрешает выдачу сигнала с выхода D8 (выход для подключения быстрых устройств на фиг.4), используемого для подключения устройств, не требующих режима ожидания микропроцессора. В такте 12 работы микропроцессора 1 при переключении из О в 1 сигнала Ф2 Синхр инверсньш выход триггера

15устанавливается в состояние логического О. В такте ТЗ работы микропроцессора 1 инверсньш выход триггера 15 (при переключении сигнала Ф2

Синхр из О в 1 , установится в состояние логической 1, а прямой выход триггера 16 еще не успеет переключиться в противоположное состояние и на выходе элемента И 18 (на выходе переноса первого счетчика тактов) возникает сигнал логической 1, которьй поступает на вход элемента И-НЕ 23. На другой вход этого элемента также поступает сигнал логической 1 Ожд , поэтому на выходе элемента И-НЕ 23 появляется сигнал логического О, который поступает на вход элемента ИЛИ-НЕ 22. С выхода этого элемента поступает сигнал логической 1 на вход синхронизации триггера 14 и усранавливает его в 1, тем самым запрещая дешифрацию разрядов А14 и А13 адреса на время его неопределенного значения.

Формула изобретен и я

Устройство синхронизации ввода-вывода микрЪпроцессора, содержащее блок управляющих сигналов, включающий три элемента НЕ, элемент И и элемент И- НЕ, и блок триггеров готовности,причем вход первого элемента НЕ соединен с входом ожидания устройства, вход второго элемента НЕ подключен к входу синхронизации устройства, вход третьего элемента НЕ соединен с тактовым входом устройства, первым входом элемента И-НЕ и тактовым входом блока триггеров готовности, первьй и второй входы элемента И подключены к выходам соответственно третьего и второго элементов НЕ, второй вход элемента И-НЕ соединен с входом синхронизации устройства, вход сброса блока триггеров готовности подключен к входу сброса устройства, вход ожидания,вход готовности и выход блока триггеров готовности соединены соответственно с входом ожидания, входом готовности и выходом готовности устройства, отличающееся тем, что, с целью увеличения быстродействия,оно содержит блок счетчиков тактов,вклю- чающий первый триггер режима, первый счетчик тактов, выполненный в виде триггеров младшего и старшего разря- дов и первого элемента И, второй триггер режима, второй элемент И, дешифратор, элемент ИЛ1, два элемента ИЛИ-НЕ, элемент И-НЕ и второй счетчик тактов, выполненный в виде триггера тактов, а блок тригг;еров готовности включает элемент И-НЕ, элемент ИЛИ-НЕ и два триггера готовности,при этом первьш, второй и третий входы и выход элемента И-НЕ блока триггеров готовности подключены соответственно к выходу первого триггера готовнос- ти, входу ожидания, тактовому входу этого блока и -первому входу элемента ИЛИ-НЕ блока триггеров готовности, второй вход и выход которого соединены с входом сброса этого блока и входом синхронизации второго триггера готовности, информационные и установочные входы триггеров готовности подключены к шине единичного потен- циала, вход синхронизации первого триггера готовности соединен с входом готовности блока триггеров готовности, выход второго триггера готовности подключен к выходу этого блока

с 0 з

0

а входы сброса триггеров готовности являются входом сброса блока триггеров готовности и соединены с выходом элемента ИЛИ блока счетчиков тактов, первый, второй и третий информационные входы, управляющий вход, первый, второй и третий выходы дешифратора подключены соответственно к первому, второму и третьему разрядам входа режима устройства, прямому выходу первого триггера режима, первому, второму и третьему входам элемента fOTi блока счетчиков тактов, первый и второй входы и выход первого элемента И блока счетчика тактов соединены с инверсным выходом триггера младшего разряда, прямым выходом триггера старшего разряда и первым входом элемента И-НЕ того же блока, второй вход этого элемента И-НЕ подключен к выходу первого элемента HF блока формирования управляющих сигналов, первьй и второй входы и выход второго элемента И блока счетчиков тактов соединены соответственно с выходом элемента И блока формирования з Т равляющих сигналов, инверсным выходом второго триггера режима и входом синхронизации Триггера тактов, первый и второй входы и выход первого элемента ИПИ-НЕ блока счетчиков тактов подключены соответственно к инверсному выходу триггера тактов, выходу элемента И-НЕ этого блока и входу синхронизации первого триггера режима, первый и второй входы и выход второго элемента ИЛИ-НЕ блока счетчиков тактов соединены соответственно с прямым выходом триггера тактов, входом сброса устройства и входом синхронизации . второго триггера режима, информационные и установочные входы первого и второго триггеров режима и установочные входы триггеров младшего и старшего разрядов и триггера тактов подключены к шине единичного потенциала, входы сброса первого триггера режима и триггеров младшего и старшего разрядов соединены с выходом элемента И-НЕ блока формирования управляющих сигналов, вход синхронизации триггера младшего разряда подключен к выходу элемента И блока формирования управляющих сигналов, информационный вход триггера младшего разряда и вход синхронизации триггера старшего разряда соединены с инверсным выходом триггера младшего разря71394215

да информационный вход триггера первого элемента НЕ блока Лормнрова

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Трехканальное устройство для управления синхронизацией микропроцессорной системы | 1985 |

|

SU1352475A1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании микропроцессорных систем (ШС) и микропроцес сорн1.1Х устройств (МПУ). Целью изобретения является увеличение быстродействия устройства. С этой целью в устройство, содержащее блок управляющих сигналов, включакнций три элемента НЕ, элемент И и элемент И-НЕ, и блок триггеров готовности, введен блок счетчиков тактов, включакяций первый триггер режима, первый счетчик тактов, выполненный в виде триггеров младпего и старшего разрядов и первого элемента И, второй триггер режима, второй элемент И, дешифратор, элемент ИЛИ, два элемента ИЛИ-НЕ, элемент И- НЕ и второй счетчик тактов, выполнен- ньй в виде триггера тактов, а блок триггеров готовности включает элемент. И-НЕ, элемент ИЛИ-НЕ и два триггера готовности, 6 ил. с S (Л

старшего разряда подключен к инверсному выходу того же триггера, входы сброса второго триггера режима и триггера тактов соединены с выходом

Вь/х1 ОМ4

BbixZ симхр

BbixJ А /5

Вых А/

BbfX5 AfJ

Sxf

ВхЗ

Вх2

Sxf

Залрос л еЗ устройства

Готобность „ мев/f. ycmpoucmSa

ния управлякнцих сигналов, а информа- ционньш вход триггера тактов подк.пю- с чен к инверсному выходу того же триггера.

0/П МОПК{( „ Cf/УОС

Isx7

Bxf

Вх2

SxJ

Вх

В.х5

--

Ф2

Bf

S2

BJ

84

B5

66

i

X5

и

XS

Xf

X

.1

От тактобоео генератора ,

От кнопт fBx.6 Сброс ,

Лг

wt

от

Вх.

i

Синхр

Af.c

/7/5

М

i

512

2: Ч

§:

В2.

(

84 f В6 .,

te f

г

аж41 Щ

Вх.

Вх.П V2

Bi(.2 f6poc

М7

1

а 1

Г1

Запрос „Пед/i. устр.

Готовность . устроттба

12

W

Вх.1

Готвдность

7/

Вк2

Вх.5

/J

Шина единичного

потени.иам

Раг.З

0WS. 6

| ПРИЕМНАЯ КАМЕРА ВЕРТИКАЛЬНО-ШПИНДЕЛЬНОЙ ХЛОПКОУБОРОЧНОЙ МАШИНЫ | 0 |

|

SU204784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Коффрон Дк | |||

| Технические средства микропроцессорных систем | |||

| Практичес- кий курс | |||

| М.: Мир, 1983, с | |||

| Устройство непрерывного автоматического тормоза с сжатым воздухом | 1921 |

|

SU191A1 |

Авторы

Даты

1988-05-07—Публикация

1985-12-29—Подача