t

г

/) С

14

ких секций 1, каждая из которых содержит регистр 2 адреса с адресными входами 3, дешифраторы 4 и 5, входящие соответственно в первьй 6 и второй 7 блоки памяти, регистр 8 слова с информационными входами 9 и выхода- Ми 10, элементы ИЛИ 11, сумматоры 12, 13 и 14 по модулю два, две группы элементов И 15, 16, два элемента НЕ 17, 18 и элемент И 19 с выходом ,20. Информация одновременно записыва835

ется в блоки 6 и 7, Считанная информация проверяется на четность с помощью сумматоров 12-14. В зависимости от результата контроля в регистр 8 записывается информация из того блока 6 или 7 памяти, в котором нет сбоев ипи отказов. При наличии сбоя или отказа- в одних и тех же ячейках обоих блоков 6 и 7 памяти на выход 20 выдается сигнал о недостоверное™ ти информахщи. 1.ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Запоминающее устройство с обнаружением ошибок | 1987 |

|

SU1425790A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ИНФОРМАЦИОННОГО ТРАКТА «ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОМАНД — ПРОЦЕССОР» | 1973 |

|

SU408309A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1605239A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено при конструировании резервированных ОЗУ и ПЗУ.. Цель изобретения - ловышение надежности устройства. Устройство состоит из несколь

ИзoбpJEтeниe относится к вычислительной технике и может быть применено при конструировании резервированных ОЗУ и ПЗУ.

Цель изобретения - повышение надежности устройства.

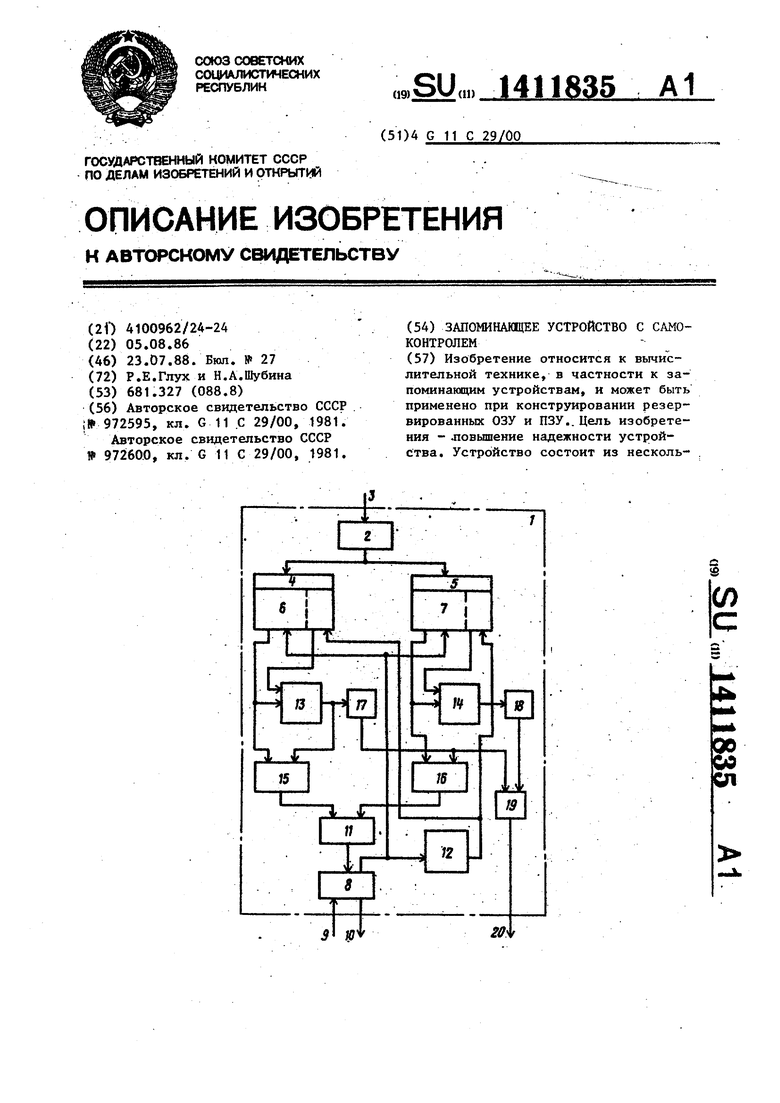

На чертеже изображена функциональная схема предложенного устройства.

Устройство может быть разделено на .несколько секций 1, каждая из которых содержит регистр 2 адреса -с адресными входами 3, первый 4 и второй 5 дешифраторы, входящие соответственно в первьй 6 и второй 7 блоки памяти, регистр 8 слова с информационными входами 9 и выходами 10, элементы ИЛИ 11, первый 12j второй 13 и третий 14 сумматоры по модулю два, первую 15 и вторую 16 группы элементов И, первый 17 и второй 18 элементы НЕ и элемент И 19 с выходом 20.

В качестве блоков 6 и 7 памяти могут быть применены либо блоки ОЗУ, либо блоки ПЗУ.

Устройство работает следующим образом.

Информация одновременно записывается и считьтается с обоих блоков 6 и 7. Один разряд всех ячеек обоих блоков 6 и 7 является контрольным и в него записывается (или заранее заносится при программировании в случае выполнения блоков 6 и 7 ПЗУ) сумма по модулю два содержимого всех разрядов данной ячейки. При каждом чтении информация, считанная из каждого блока 6 и 7, проверяется на четность. В зависимости от результа- та проверки в регистр 8 записьшается

. содержимое ячейки из первого 6 ипи второго 7 блока памяти. Таким образом осуществляется исправление информации. 5 Обращение к ячейкам накопителей

6и 7 .осуществляется по адресу, заданному в регистре 2 после дешифрации его на дешифраторах 4 и 5.

При записи информация по входу fO 9 поступает на .регистр 8, с которого передается на информационные входьг jблоков 6 и 7 и на входы сумматора 12 Сумма по модулю два содержимого всех разрядов информации с выхода 5 сумматора 12 поступает на контрольные входы блоков 6 и 7.

При чтении информация с информа- , ционных и контрольного выходов блоков 6 и 7 поступает на входы соот- 20 ветственно сумматоров 13 и 14, а с информационных выходов блоков 6 и

7- соответственно уа входы элементов И 15 и 16. При правильной работе, например, блока 6 с выхода сум5 матора 13 на входы элементов И 15 поступает сигнал, разрешамций передачу информационного слова из блока 6 через элементы ИЛИ 11 в регистр 8.

8противном случае с выхода суммато- 0 ра 13 через элемент НЕ 17 на входы

элементов И 16 поступает сигнал, разрешающий передачу информационного слова ий блока 7 в регистр 8. Таким образом, при каждом обращении 5 устройству при наличии сбоя или отказа конкретной ячейки блока 6 на выход 10 устройства информация поступает с аналогичной ячейки блока 7. При этом при наличии сбоя или от31411835

ока 6 или блока 7 сигнал с соответс.твухидего из сумматоили 14 через элементы НЕ 17 поступает соответственно на , или второй вход элемента ри одновременном сбое или отобоих блоках 6 и 7 по одноу адресу на выходе 20 появлягнал о недостоверности инфор- ю а выходах 10 устройства.

большой разрядности.- например троении многоразрядных ПЗУ манд на интегральных микросхечи р вх л л в м р гр п эл вы мя вы ма к к вт да в су с гр ры и вх вт по то ды со то по ст ся ин

мах, имеющих ограниченное количество разрядов, такие ЗУ секционированы и число секций 1 равно отношению общей разрядности ЗУ к разрядности одИой секций. В этом случае построение каждой секции 1 по предлагаемой схеме позволяет резко повысить надежность ЗУ, так как в каждой секции по каждому адресу возможно независимое переключение ячеек блоков 6 и 7, чем обеспечивается поэлементное резервирование ячеек ЗУ, содержащего комплект блоков 6 и 7, и тем самым повьшение надежности устройства, в том числе при построении ПЗУ.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее первый и второй блоки памяти, регистр слова, первьгй сумматор по модулю два, элементы ИЛИ, элемент И и регистр адреса, выходы которого подключены к .ад- ресньм входам nepStoro и второго блоков памяти, информационные входы которых соединены с первым выходом

регистра слова, разряды первого информационного входа которого подключены к выходам элементов ИЛИ, вторые информационный вход и выход регистра слова являются информационными входом и выходом устройства, отличающееся тем, что, с целью повышения надежности устройства-, в него введены второй и третий сумматоры по-модулю два, первьй и второй элементы НЕ, первая и вторая группы эл.ементов И, выходы которых подключены соответственно к входам элементов ИЛИ, причем контрольные выходы первого и второго блоков памяти соединены соответственно с первыми входами второго и третьего сумт маторов по модулю два, вторые входы которых подключены соответственно к информационным выходам первого и второго блоков памяти и первым входам элементов И соответственно первой и второй групп, выходы второго сумматора по модулю два соединены с вторыми входами элементов И первой группы и входом первого элемента НЕ, выход которого подключен -к вторым входам элементов И второй группы и первым входам элемента И, второй вход которого соединен с выходов второго элемента НЕ, вход ко торого подключен к выходу третьего сумматора по модулю два, контрольные вхо- ды первого и второго блоков памяти соединены с выходом первого сумматора по модулю два, входы которого подключены к одним из выходов регистра слова, выход элемента И является выходом сигнала недостоверности информации устройства.

| Авторское свидетельство СССР | |||

| Программируемое постоянное запоминающее устройство | 1981 |

|

SU972595A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-23—Публикация

1986-08-05—Подача