Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем управления , например , шахтными манипуляторами, суммарный ток питания которых при одновременном подключении всех каналов (модулей) к источнику питания может оказаться большим, чем его прецельное значение, допустимое по требованиям искробезопасности.

Цель изобретения - сокращение энергопотребления микропроцессорной системы.

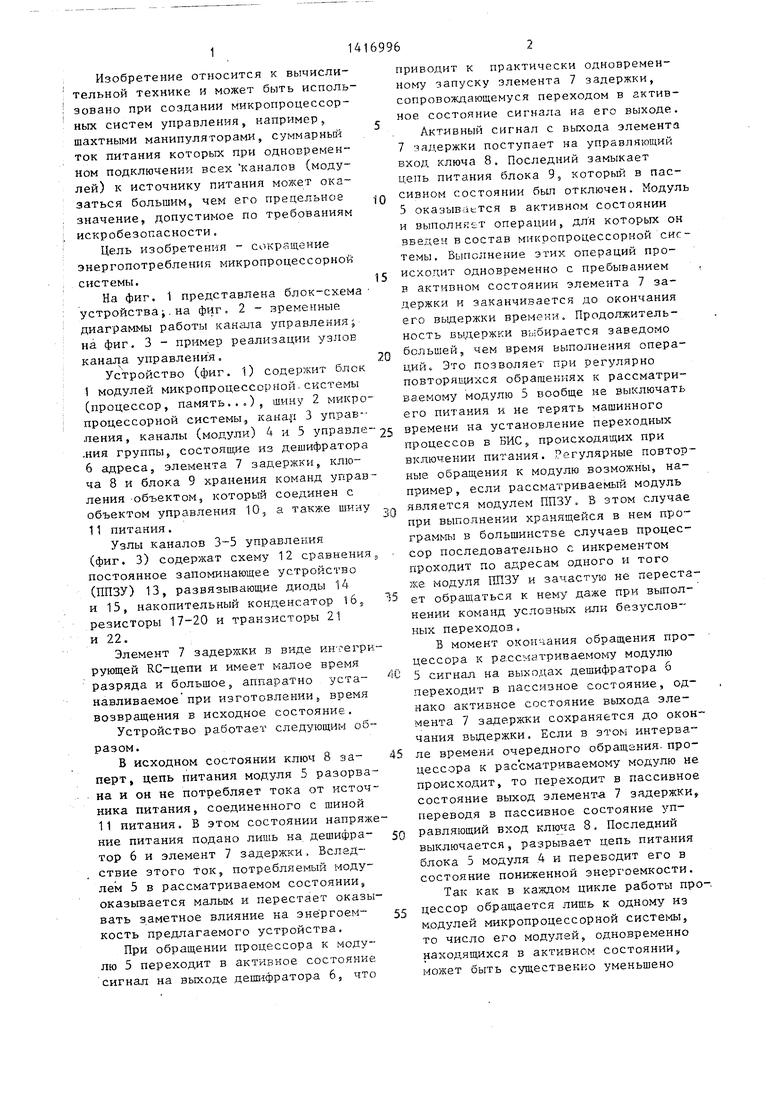

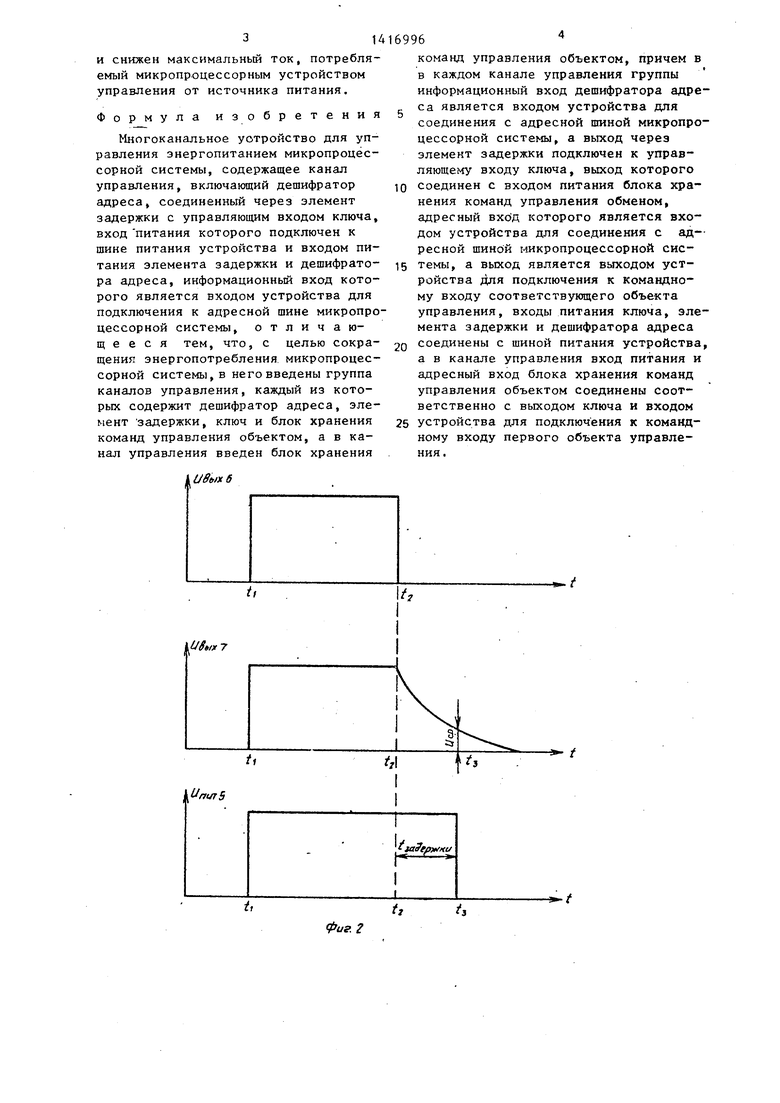

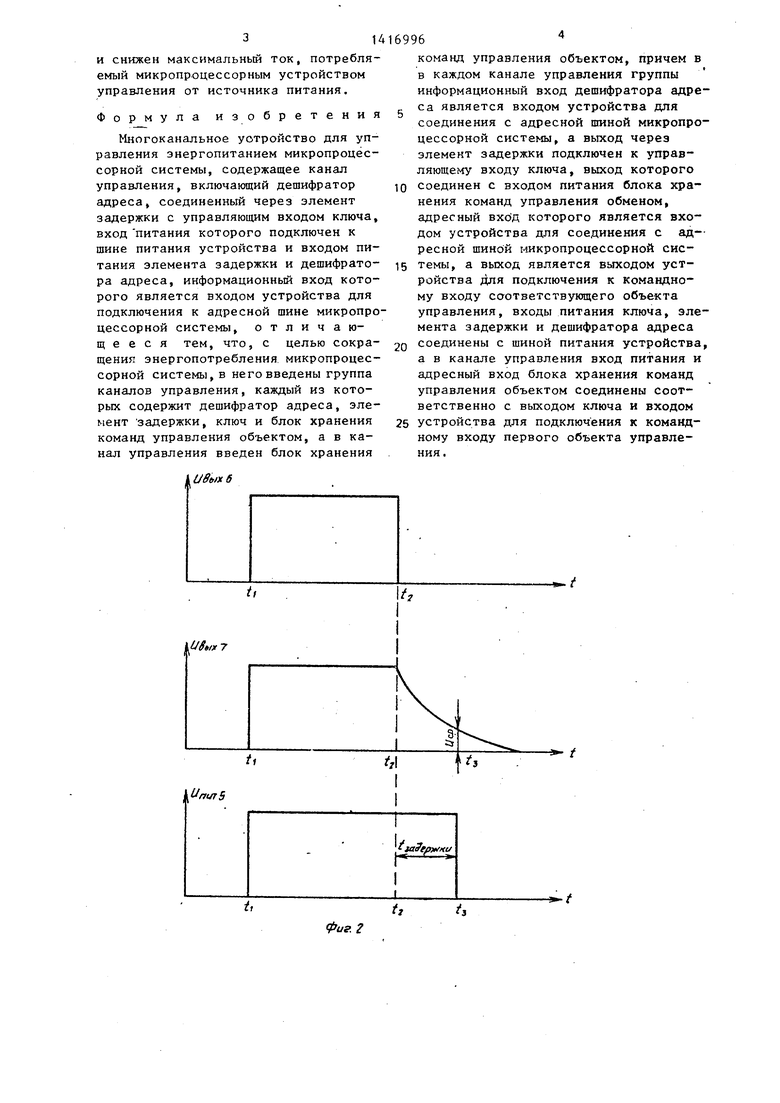

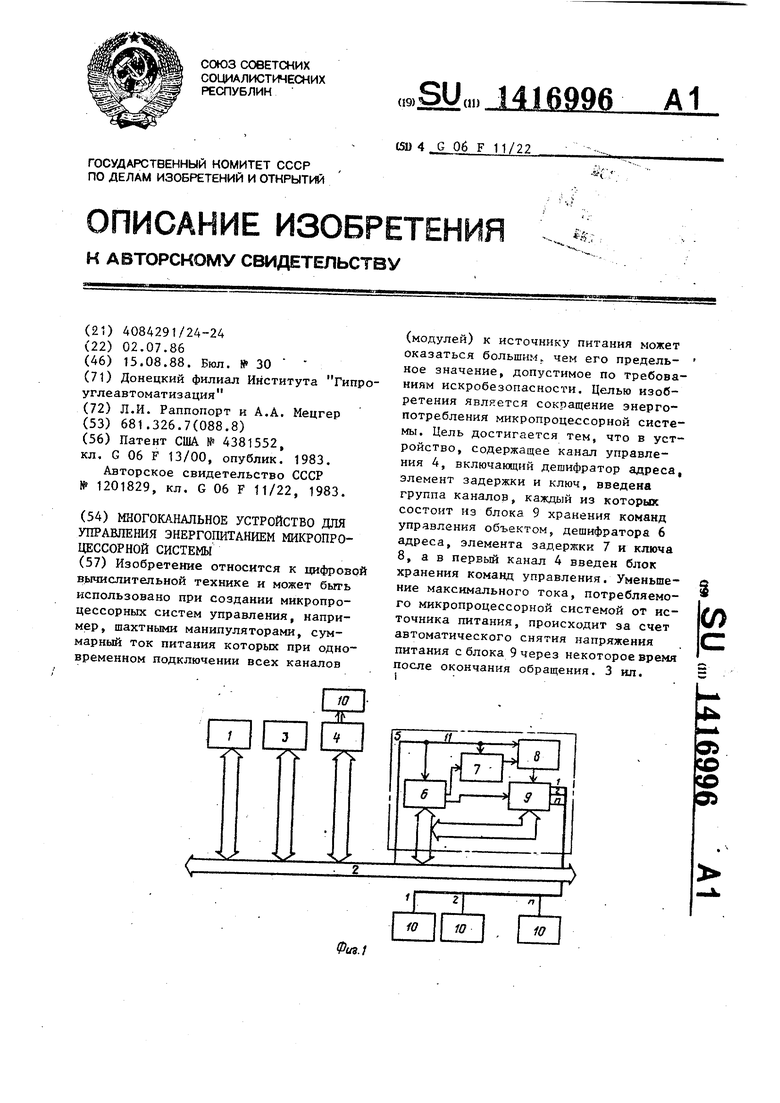

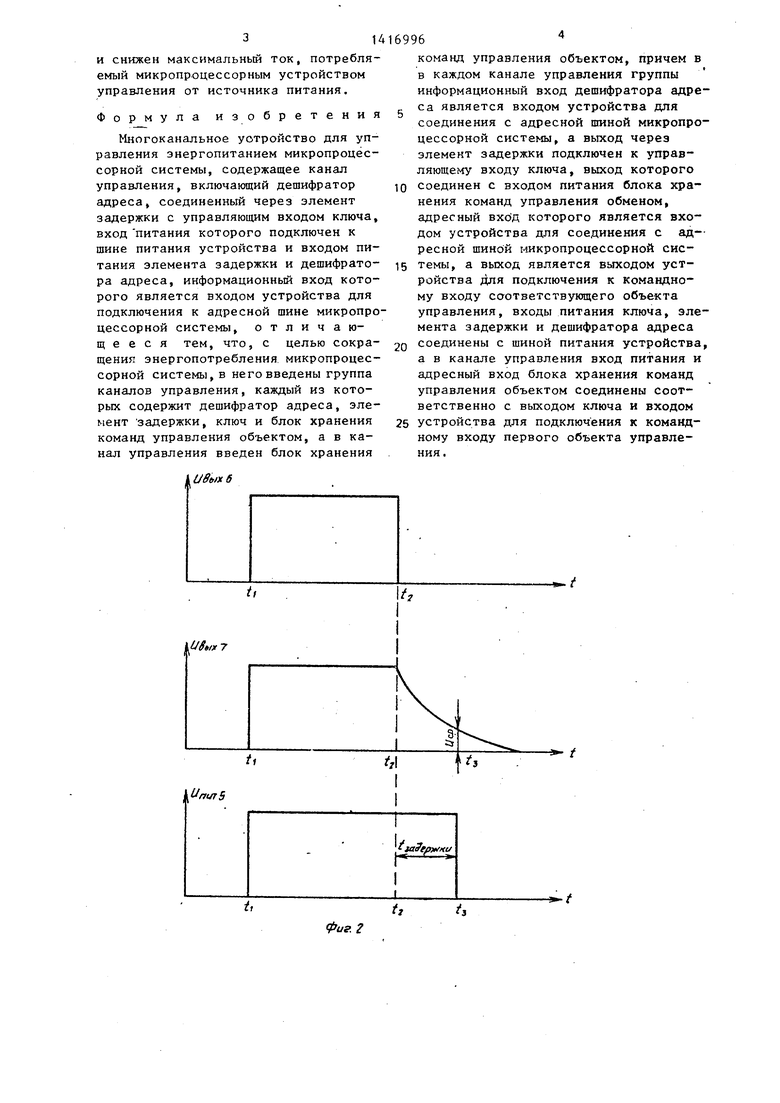

На фиг. 1 представлена блок-схема устройстваi,на фиг. 2 - временные диаграммы работы канала управления j на фиг. 3 - пример реализации узлов канала управления,

Устройство (фиг. 1) содержит блок

Iмодулей микропроцессорной.системы (процессор, память...), шину 2 микропроцессорной системы, кака|1 3 управ-- ления, каналы (модули) 4 и 5 управле .НИН группы, состоящие из дешифратора

6 адреса, элемента 7 задержки, ключа 8 и блока 9 хранения команд управления -объектом, который соединен с объектом управления 10, а также шину

I1питания.

Узлы каналов 3-5 управления (фиг. 3) содержат схему 12 сравнения постоянное запоминающее устройство (ППЗУ) 13, развязывающие диоды 14 и 15, накопительный конденсатор 6,. резисторы 17-20 и транзисторы 21 и 22.

Элемент 7 задержки в виде интегрирующей RC-цепи и имеет малое время разряда и большое, аппаратно уста- навливаемое при изготовлении, время возвращения в исходное состояние.

Устройство работает следующим образом.

В исходном состоянии ключ 8 за- перт, цепь питания модуля 5 разорвана и он не потребляет тока от источника питания, соединенного с шиной 11 питания. В этом состоянии напряжение питания подано лишь на дешифра- тор 6 и элемент 7 задержки. Вследствие этого ток, потребляемый модулем 5 в рассматриваемом состоянии оказывается малым и перестает оказывать з.аиетное влияние на энёргоем- кость предлагаемого устройства.

При обращении процессора к модулю 5 переходит в активное состояние сигнал на выходе дешифратора 6, что

приводит к практически одновремен- Hosry запуску элемента 7 задержки, сопровождающемуся переходом в активное состояние сигнала на его выходе.

Активный сигнал с выхода элемента 7 задержки поступает на управляющий вход ключа 8. Последний замыкает цепь питания блока 9, который в пассивном состоянии бьт отключен. Модул 5 оказывается в активном состоянии и выполняет операции, для которых он введен в состав микропроцессорной системы. Выполнение этих операций происходит одновременно с пребыванием в активном состоянии элемента 7 задержки, и заканчивается до окончания его выдержки времени. Продолжительность выдержки выбирается заведомо большей, чем время выполнения операций Это позволяет при регулярно повторящихся обращениях к рассматриваемому модулю 5 вообще не выключать его питания и не терять машинного времени на установление переходных процессов в БИСj происходящих при включении питания. Регулярные повторные обращения к модулю возможны, например , если рассматриваемый модуль является модулем ППЗУ. В этом случае при выполнении хранящейся в нем про граммы в большинстве случаев процессор последовательно с инкрементом проходит по адресам одного и того 7хе модуля ППЗУ и зачастую не перестает обращаться к нему даже при выполнении команд условных или безусловных переходов.

В момент окончания обращения процессора к ра.ссматриваемому модулю 5 сигнал на вь5ходах дешифратора б переходит в пассивное состояние, однако активное состояние выхода элемента 7 задержки сохраняется до окончания выдержки. Если в этом интервале времени очередного обращения, процессора к рассматриваемому модулю не происходит, то переходит в пассивное состояние выход элемент-а 7 задержки, переводя в пассивное состояние управляющий вход ключа 8, Последний выключается, разрывает цепь питания блока 5 модуля .4 и переводит его в состояние пониженной энергоемкости.

Так как в каждом цикле работы про цессор обращается лишь к одному из модулей микропроцессорной системы, то число его модулей, одновременно находяшд1хся в активном состоянииj, может быть существенно уменьшено

314

и снижен максимальный ток, потребляемый микропроцессорным устройством управления от источника питания.

Формула изобретения

Многоканальное устройство для управления энергопитанием микропроцессорной системы, содержащее канал управления, включающий дешифратор адреса, соединенный через элемент задержки с управляющим входом ключа, вход питания которого подключен к шине питания устройства и входом питания элемента задержки и дешифратора адреса, информационный вход которого является входом устройства для подключения к адресной щине микропроцессорной системы, отличающееся тем, что, с целью сокращения энергопотребления микропроцессорной системы, в него введены группа каналов управления, каждый из которых содержит дешифратор адреса, элемент задержки, ключ и блок хранения команд управления объектом, а в канал управления введен блок хранения

ив1,1Х б

10

6996

команд управления объектом, причем в в каждом канале управления группы информационный вход дешифратора адреса является входом устройства для соединения с адресной шиной микропроцессорной системы, а выход через элемент задержки подключен к управляющему входу ключа, выход которого соединен с входом питания блока хранения команд управления обменом, адресный вхЬд которого является входом устройства для соединения с ад-- ресной шиной микропроцессорной системы, а выход является выходом устройства для подключения к командному входу соответствующего объекта управления, входы питания ключа, элемента задержки и дешифратора адреса соединены с шиной питания устройства, а в канале управления вход питания и адресный вход блока хранения команд управления объектом соединены соответственно с выходом ключа и входом 25 устройства для подключения к командному входу первого объекта управления.

15

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для контроля данных электронной вычислительной машины при прерываниях питания | 1983 |

|

SU1129615A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

Изобретение относятся к цифровой вычислительной технике и может быть использовано при создании микропроцессорных систем управления, например, шахтными манипуляторами, суммарный ток питания которых при одновременном подключении всех каналов (модулей) к источнику питания может оказаться большим,, чем его предельное значение, допустимое по требованиям искробезопасности. Целью изобретения является сокращение энергопотребления микропроцессорной системы. Цель достигается тем, что в устройство, содержащее канал управления 4, включающий дешифратор адреса, элемент задержки и ключ, введена группа каналов, каждый из которых состоит из блока 9 хранения команд управления объектом, дешифратора 6 адреса, элемента задержки 7 и ключа 8, а в первый канал 4 введен блок хранения команд управления. Уменьшение максимального тока, потребляемого микропроцессорной системой от источника питания, происходит за счет автоматического снятия напряжения питания с блока 9 через некоторое время после окончания обращения. 3 ил. W

| Патент США № 4381552, кл, G 06 F 13/00, опублик | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для управления энергопитанием микропроцессорной системы | 1983 |

|

SU1201829A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1986-07-02—Подача