Я

&

(Л

с:

00 ts9 СЛ СЛ «

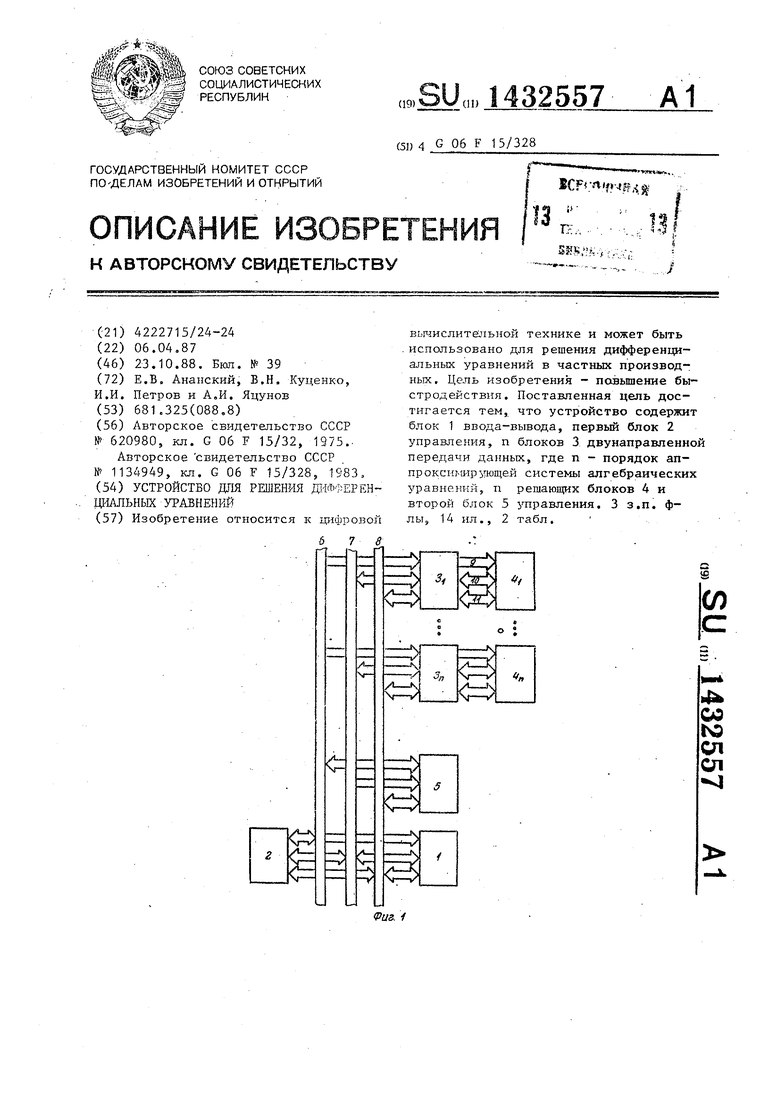

Изобретение относится к дм(|1рово1 вьгчпслитолыю-и технике к устройствам для обрабо 1 ки дифрО1 ых данных и может . использовано для репюпи ; Д1 ффе - ренциа.иьпьк ураппепий в производных ,

Цель изобретенмя - понышепне би- стродействия устройства,

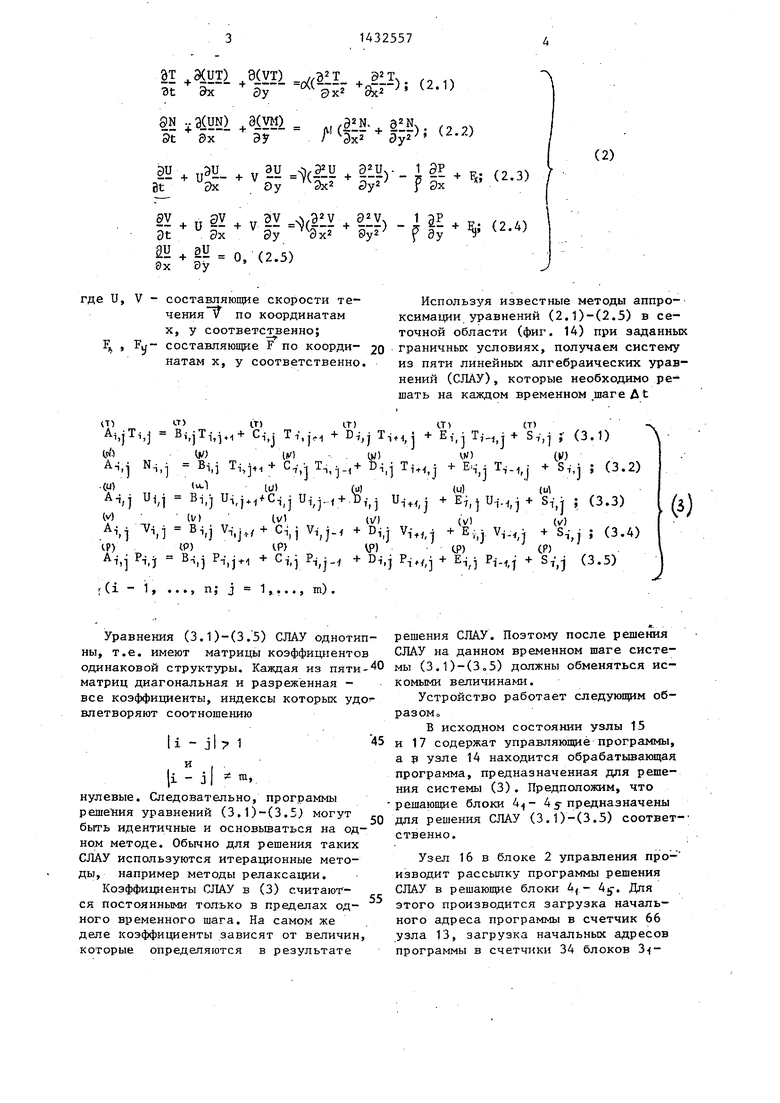

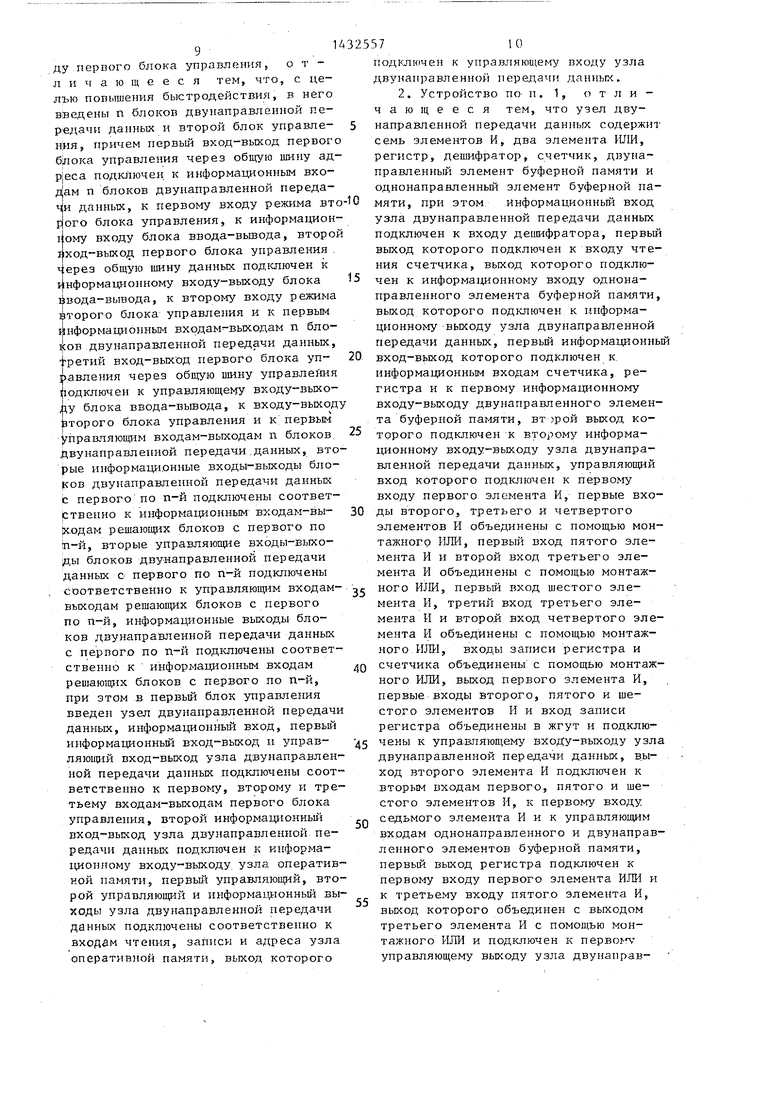

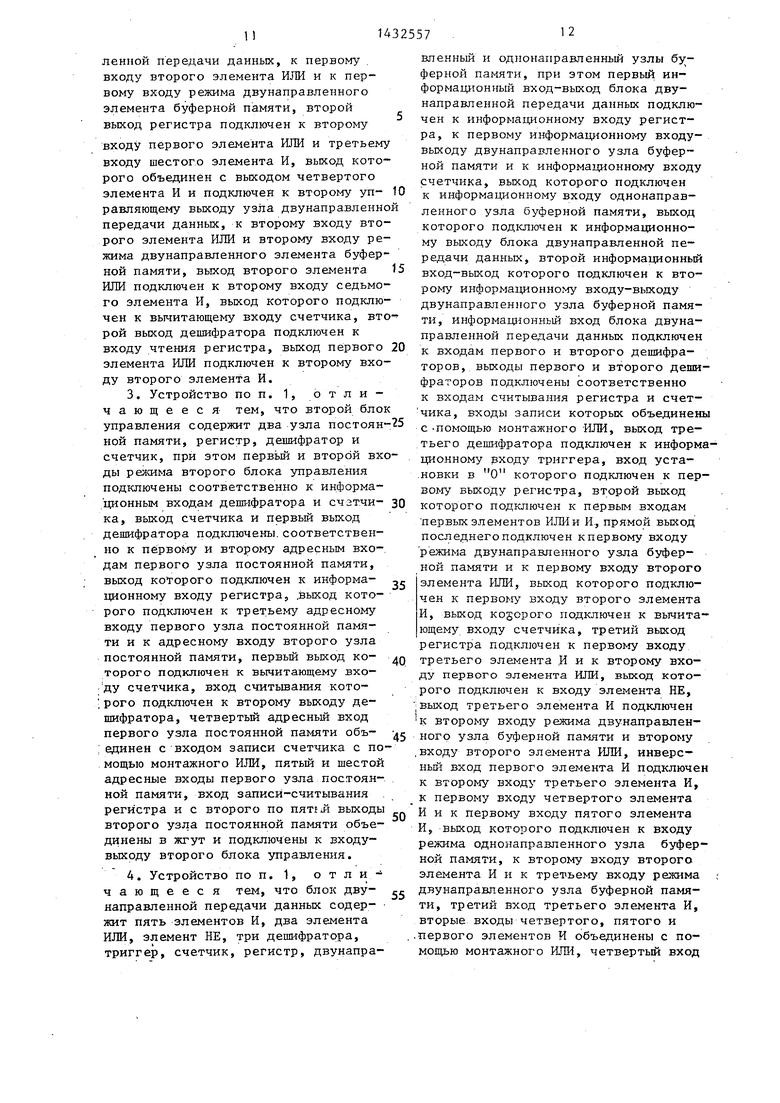

На фиг, 1 приведена схемгх предла- г аемого устройства; па фиг. 2 - схема первого блока управления; па фиг, 3 - схема решающего блока; па фиг, 4 - схема второго блока управления; па- фиг 5 - схема блока двула1 равлеи)1ой передач даппых; па фиг. 6 - схема реи зющего узла; па фиг, 7 - с;хема ysjia постоянпой памяти; на фиг, 8 - схема узла оперативпой пам;):ти; па фиг, 9 - схема узла приоритетного

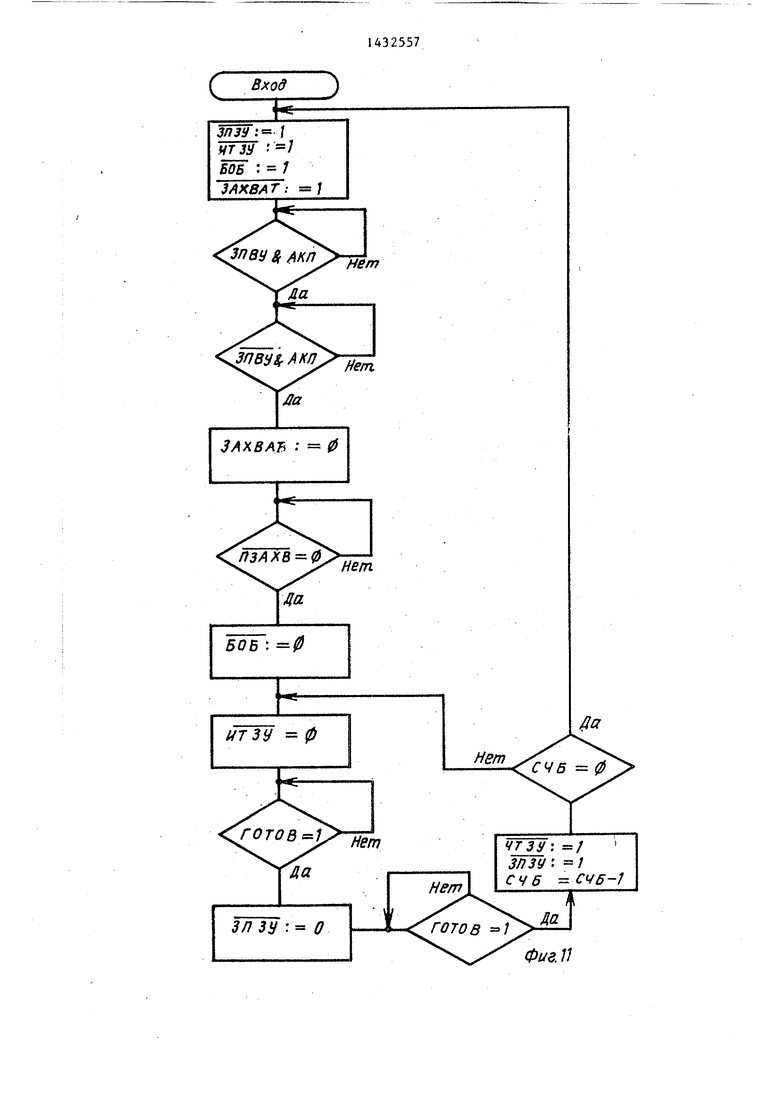

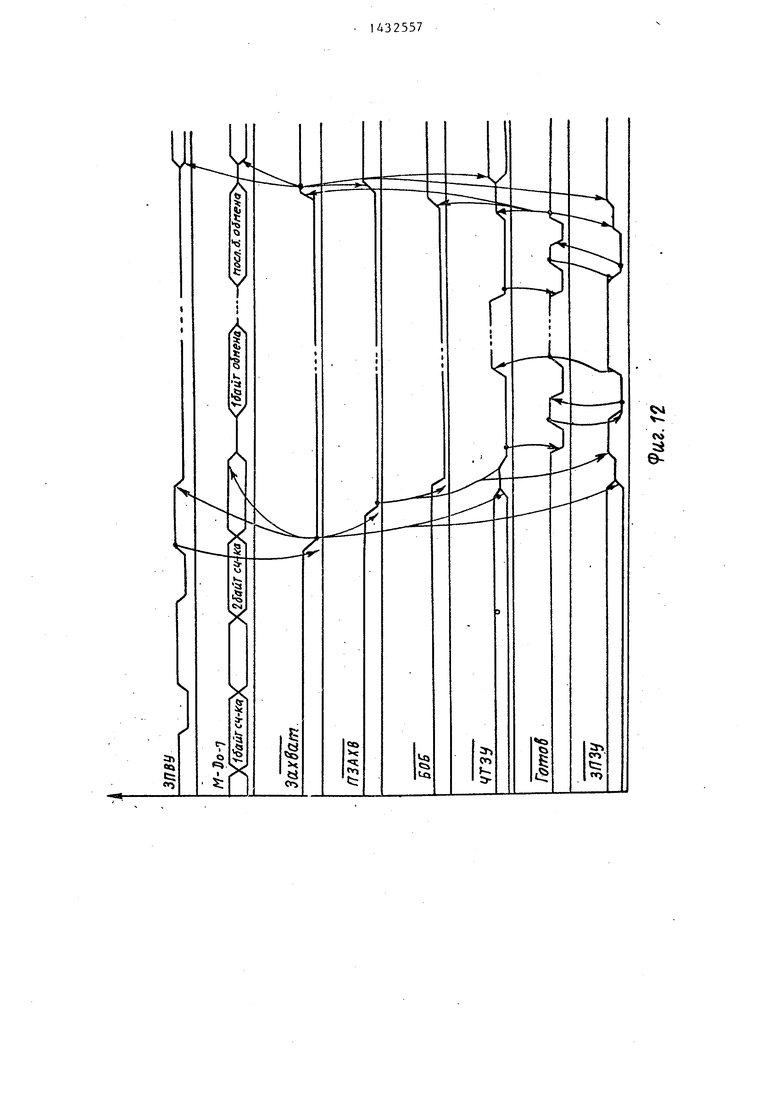

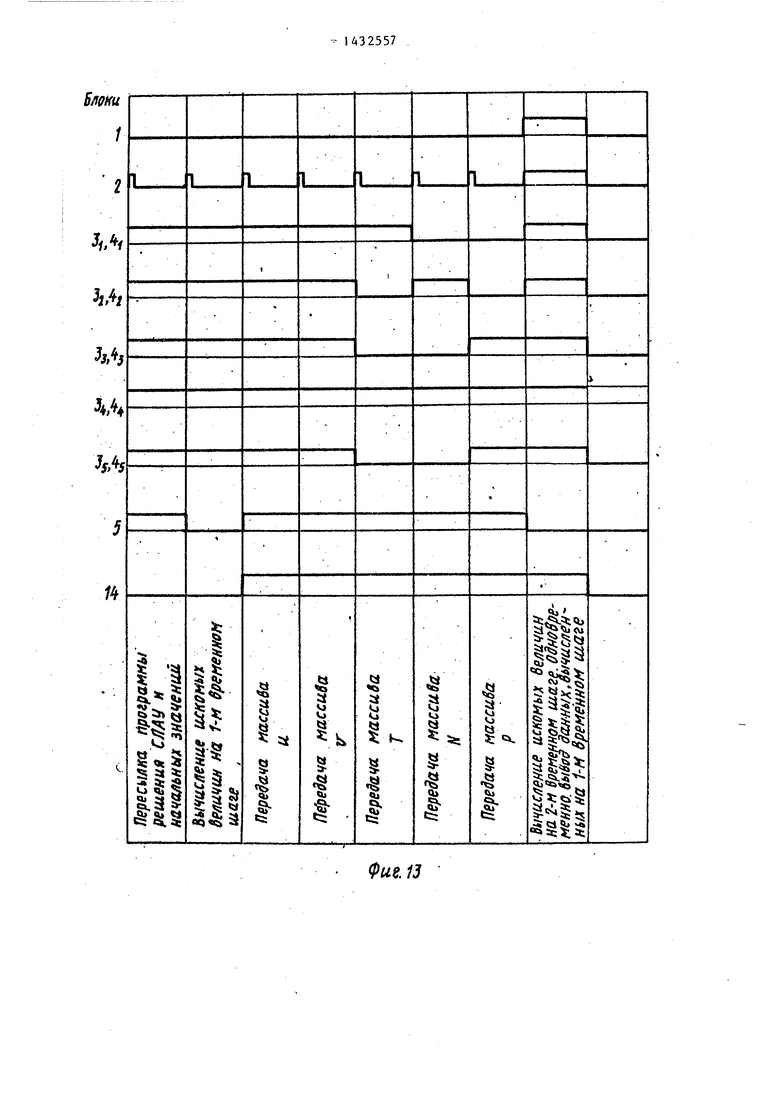

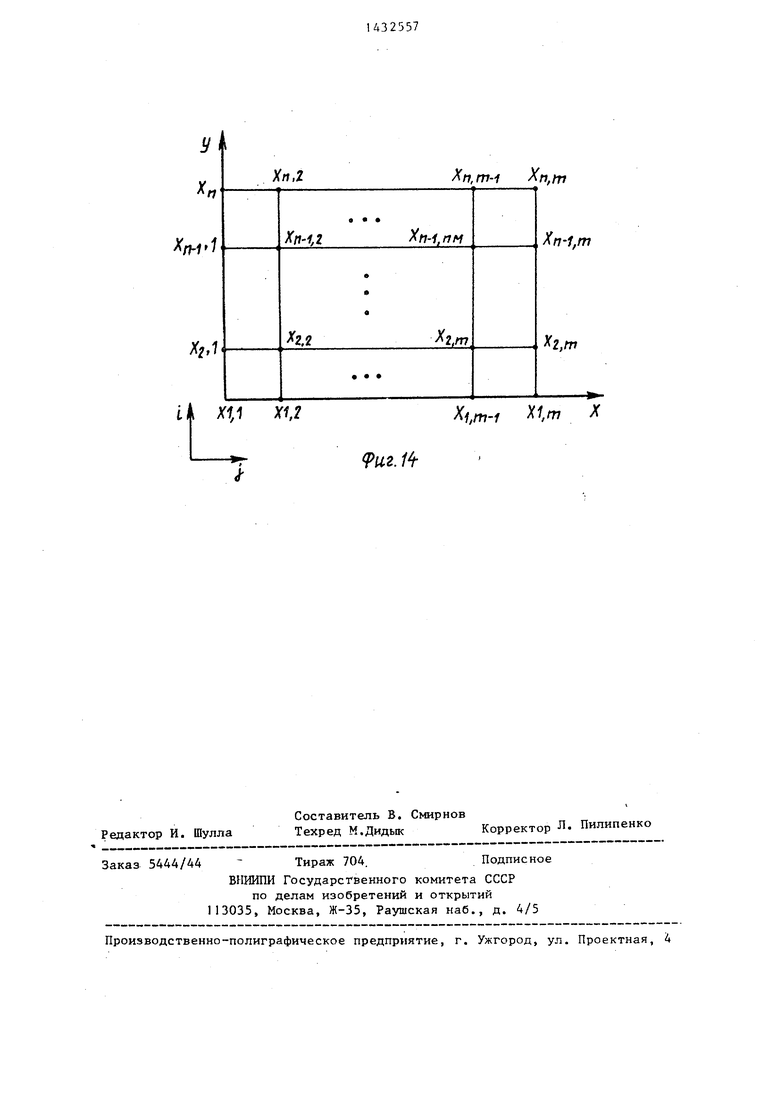

прерывания; па фиг, 10 - схема узла двупаправленпо11 передачи даш-ых первого блока управления; па фиг, 11 - алгоритм работы второго блока управ- лепил; па фиг о 12 - вреке 111ая диаг- рамма работы второго блока уиравле- . па. фиг о 13 - диагрп 1ма aajiH ro™ сти ресурсов устройства; па 1А область .моделирования.

Устройство для решепия диффереп- 11;иальн. ураЕпеш- й содержит бл.ок 1 ввода-вывода первый блок 2 управле у,11я, блоки 3i-- 3,, двупаправленной передачи данных,, pemaioiipie блоки 4i , втор oil 5 управления, системные .адресные аии-Я) 6, дву1гаправленные сис .{емные ииформлщ1ОГ1Пые 7 н управляющие 8 .юипы, адресные иг-ппл 9; дву.г(апрг1влен ные информационные iimi-ibi 10, ynpaBj/Hio- ш,ие :ш1нь1 11.

. о

Блок 2 управ.11ения содержит узел

45

приоритетного прерыванияз узел ij двунаправленной передач: дл;);.п.,п. узел 14 оперативной памяти, ysej 15 по.;:то-- яиной памяти и решающий узел 16,

Решаютщй блок 4 соде. узел 17 постоя п ой паЕ-зяти, узел 18 оператив - пой паюгги и решаюшт1й узе.л 19.

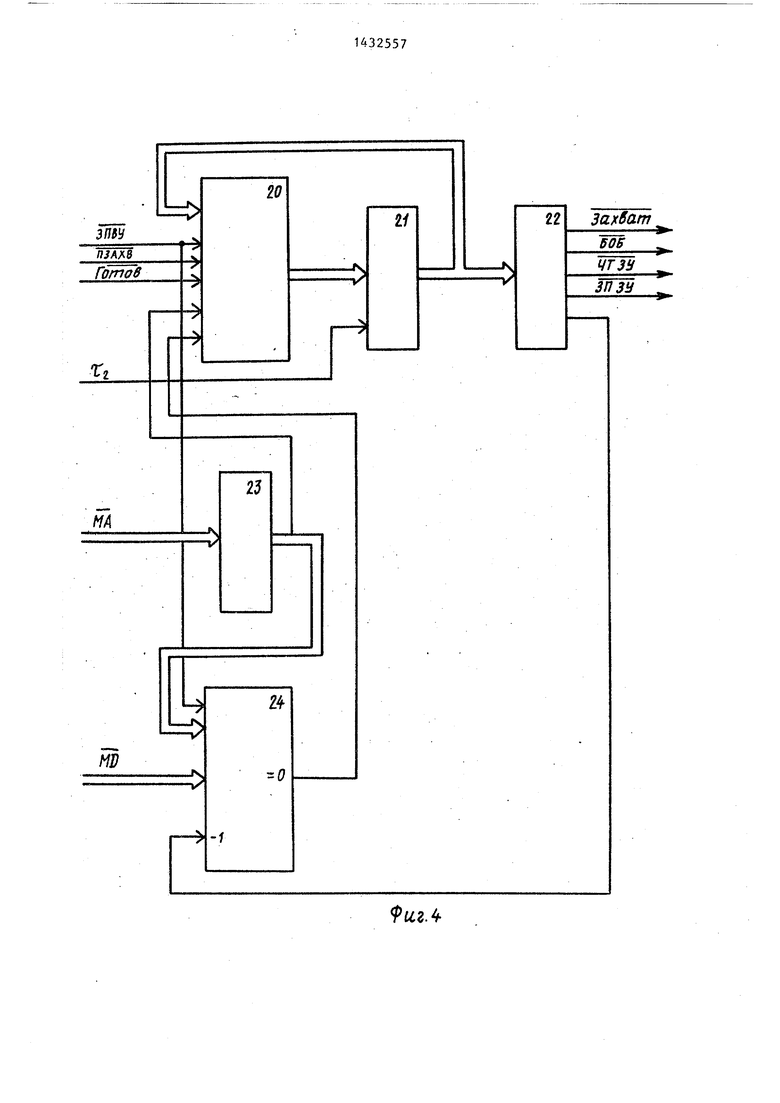

Клок 5 управления содержит первьш узел 20 постоян1Ю1( памяти, регистр 21 второй узел 22 постоянпой памяти, дешифратор 23 (адреса) и счетчик .

Блок 3 двунаправлеппой иередачи . данных содержит с первого по пяты;; элементы И 25-29, первый 30 и второй 31 деишфраторы (адреса), первьй эле- - мент ИЛИ 32, двунаправленный узел 33 буферной памяти, счетчик 34, триггер 35, второй элемент ПЛК 36, регистр

37, однонаправленр1ыГ1 учел 38 буферной памяти, трет1и) дептфратор 39 (адреса) и элемент НЕ 40.

Решающий узел 16 (19) содержит формирователь 41 тактовых импульсов, решающий элемент 42, буфер 43 адреса и контроллер 44 шины.,

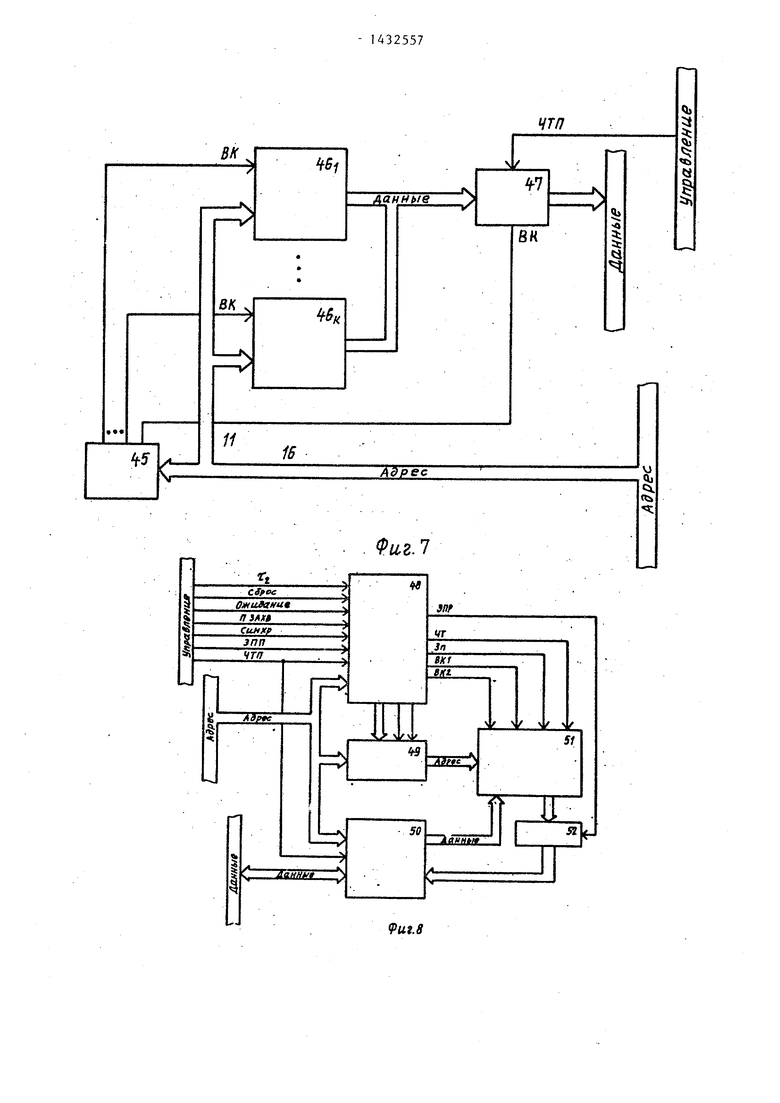

Узел 15 (17) постоянной памяти содержит се.лектор 45 , накопители 46i-46|i, и буфер 47 данных.

Узел 14 (18) оперативной памяти содержит формирователь 48 управляющих сигналов, мультиплексор 49 адреса, буфер 50 данных, накопит«шь 51 и рег истр 52.

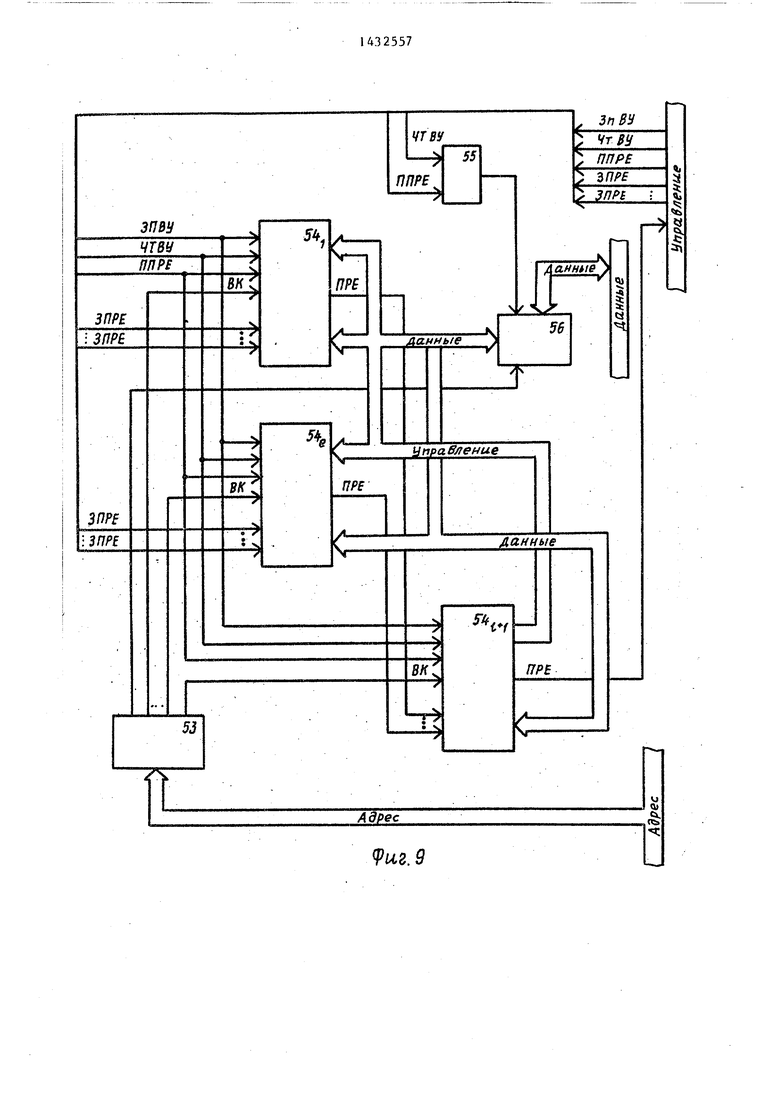

Узел 12 приоритетного прерывания coдepжJят селектор 53 адреса, элементы 54-,-54..,( приоритетного прерывани г, элемент ИГШ. 55 и буфер 56 данных.

Узел 13 двунаправленной передачи данных содержит семь элементов И 57- 63, регистр 64, дешифратор 65 (адреса), счетчик 66, два элемента ШШ 67 и 68, двунаправ.леиный 69 и од- нонаправлеиньй 70 элементы буферной памяти.

Pacct-ютрим работу устройства на примере решепия системы д;ифференци- альпьк уравнений в частных производ- i,K, состоя.щей из уравнений тепло- f jacconepeHoca, Навье-Стокса и урав- .ле.ния н:ера.зрывности для несжимаемой яагдкости

|1 ..H. ,XVT) о(ДТ;

1 4.7.(Г) ,(О

-

Q

45

JL,. (Vu)V -. - Г,

где Т - температура; J: - время;

V - вектор скорости течения; сУ - коэффициент температуропроводности;

N - кондентрация коклоне.чта; 1 коэффидиент диффузии; V- кинематическая вязкость; р - плотность жидкости; Р - давление; F - вектор объемной силы; символ дивергенции; V - символ градиента; Д - оператор Лапласа. Перепишем (1) в скалярном виде для случая двухмерных декартовых координат

);a.i)

3t Эх

|r);a.i)

4

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1305710A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1330635A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1322308A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для решения дифференциальных уравнений | 1986 |

|

SU1383391A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

Изобретение относится к цифровой б 7 S вьгчислнте льной технике и может быть . использоварю для решения дифференциальных уравнений в частных производных. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство содержит блок 1 ввода-вывода, первый блок 2 управления, п блоков 3 двунаправленной передачи данных, где п - порядок ап- проксимирмющей системы алгебраических уравнений, и решающих блоков 4 и второй блок 5 управления. 3 з.п. ф- лы, 14 ил., 2 табл.

S)N .-эсш) +91М ., .. . ,„ „,

St Эх %УА Эх - 2.2)

„эу..,|У.,р.р.. |.р,(..з,

° g f - Ir-i

эи .

Эу где и, V - составляющие скорости те- Используя известные методы аппро- чения V по координатам ксимации уравнений (2.1)-(2.5) в се- X, у соответственно; точной области (фиг. 14) при заданных F , Fy- составляющие F по коорди- 20 граничных условиях, получаем систему натам X, у соответственно. из пяти линейных алгебраических уравнений (СЛАУ), которые необходимо решать на каждом временном ,шаге At

01

а

IT)

I1.Г)(.1 1(.Т)-V

4jTi,j Bi,jTi,n+ C,-,j Ti,j, + D-i,j TS.,J + Ei,j T,,j+ S,,j ; (3.1) Л

(.Л Ui ) (ft . ) viJ) (/)

AH,-J N, Bi, Ti,.,4- C,.,:j T,,.,+ D,.j Ti,,,j + T.,,| -f S-;,j ; (3.2)

W) (ul(u) (u

A-i,| U,-j Bi,j U,,j.,4C,j Ui,.-f .Ъ,- j U,.,.,j + E, UT.,.J ; (3.3)

lv Ivl n/) (V) J)

Ai, i,j Bi,j V,-j,, + Cn,j V,., + Di,j Vi,,4 + E-;v V.,; + S,-,j ; (3.4)

IP) IP) IP) VP) tp) tP)

i PM B4,j P,j., + Ci, P,.|. Ч- D.j P,,,j + E PT.,, + S,;-j (3.5)

(i - 1, ..., n; j 1,..., m).

Уравнения (3.1)-(3. 5) СЛАУ однотипны, т.е. имеют матрицы коэффициентов одинаковой структуры. Каждая из пяти- О матриц диагональная и разреженная - все коэффициенты, индексы которых удо - влетворяют соотношению

i - jb 1

и I .

ji - Л .

нулевые. Следовательно, программы решения уравнений (3,1)-(3.5 могут быть идентичные и основьюаться на одном методе. Обычно для решения таких СЛАУ испапьзуются итерационные методы, например методы релаксации.

Коэффициенты СЛАУ в (3) считаются постоянными только в пределах одного временного шага. На самом же деле коэффициенты зависят от величин, которые определяются в результате

(b)

решения СЛАУ. Поэтому после решения СЛАУ на данном временном шаге системы (3.1)-(3„5) должны обменяться искомыми величинами.

Устройство работает следующим образом

В исходном состоянии узлы 15 и 17 содержат управляющие программы, а р узле 14 находится обрабатывающая программа, предназначенная для решения системы (3). Предположим, что решающие блоки 45 предназначены для решения СЛАУ (3.1)-(3.5) соответственно.

Узел 16 в блоке 2 управления про- изводит рассыпку программы решения СЛАУ в решаюш е блоки 4 - 45-. Дпя этого производится загрузка начального адреса программы в счетчик 66 узла 13, загрузка начальных адресов программы в счетчики 34 блоков 3-(

Получив сообщение о завершении

. вычислений первого временного шага приемом соответствующих сигналов Запрос прерьшания (ЗПРЕ, -ЗПРЕ,,-) , блок 2 управления приступает к орга- низации обмена информацией между решющими блоками 4, Например, чтобы пе-

редать массив значений U-jJ (i Г,

. . П

П; j 1;

m) блок 2 управПру выполнении функ1ц и обмена с .узлом 18 решающего блока 4 сигнал ЗАХВАТ .поступает в узел 19 решающего блока 4. После получения П ЗАХВ из

0

5

о 0

5

ления производит загрузку адресов расположения массива U-; 4 в счетчике 34 блоков ЗУ и счетчике 66 узла 13, настраивает блок 3 на режим чтения из узла 18 решающего блока 4 , блоки 3, 3j, Зд 3j-и узеа13 настраивает на режим записи в узле 18 решающих блоков 4 , 4 , 4 и 45 и узле 14 блока управления соответственно, в счетчик 24 блока 5 управления заносит число п « т, равное величине массива U 4.. После этого блок 5 управления обеспечивает быструю передачу информации из узла 18 решающего блока 4 одновременно в узлы 18 решающих блоков 4, , 4д и kg, Аналогичным образом производится обменN

остальными величинами ( ; Vvv ;

р- 1i7 ij

1, M,J)

После всех обменов информацией блок 2 управления аналогично запускает программы в решающих блоках kf для выполнения следую Г его итерационного цикла и так продолжается вычисление заданного числа шагов. После этого полученная информация из узла 14 выводится в блок 1 ввода-вьшода.

-ч

Настройка блока 3 двунаправленной

передачи данных производится от узла

16 блока 2 управления путем записи в

.регистр 37 требуемого кода согласно

табл. 1.

шины 11 элементы И 25 и 26 и узлы 33 и 38 подготовлены к работе.

Кроме загрузки регистра 37.перед началом обмена с узлом 14 узел 18 за

гружает в счетчик 34 начальный адрес узла .18. Обмен начинается с вьщачи сигнала БОБ (быстрый обмен). В этом случае элемент И 29 вьщает сигнал разрешения в узел 38, который подключает адрес с выхода счетчика 34 к магистрали адреса локальной шины, и в узел 33, которьш соединяет магистраль данных системной и локальной шин. Если выполняется запись информации, то системный сигнал Запись ЗУ (ЗП ЗУ) через элемент И27 проходит на локальную линию ЗП ЗУ и в т же время ориентирует узел 33 направлении системная магистраль данных - локальная магистраль данных. Если выполняется чтение узла 18, то системньш сигнал ЧТ ЗУ передается на локальную линию ЧТ ЗУ через элемент 26. В обеих этих операциях локальная линия ГОТОВ подключается через элемент 25 к системной линии ГОТОВ для анализа в узел 16 блока 2 управления.

По заднему фронту каждого импульса ЧТ ЗУ или ЗП ЗУ вырабатывается сигнал на входе счетчика 34, чтобы каждое следующее обращение к узлу .18 производилось по следующему по порядку адресу (здесь учитывается, что шина адреса инверсная). Это обеспечивается элементом ИЛИ 36 и элеметом 28.

Триггер 35 и дешифратор 39 (адре- са) обеспечивают возможность узлу 19 решающего блока сообщить узлу 16 блока 2 управления с помощью сигнала ЗПРЕ ,. о завершении текущего

617,, 15)

задания.

Настройка узла 13 двунаправленной передачи данных производится узлом 1 блока 2 управления путем записи в ре гистр 64. т ребуемого кода согласно табл. 2,

Та б лица 2

При этом элемент ИЛИ 67 вырабаты- вает разрешающий сигнал на элемент И 58. Кроме того, в счетчик 66 должен

0

5

0

5

5

0

0

0

5

быть загружен начальный адрес массива данных, которьй считывается из узла 14 или записывается в него.

Во время быстрого обмена, управляемого блоком 5 управления, выраба- тывается потенциал БОБ, с помощью которого элементом И 58 вырабатывается разрешение для прохождения cи J aJIoв ЧТ ЗУ через элемент И 59 или ЗП ЗУ через элемент И 60 соответственно при чтении информации или записи информации. Кроме того, выход элемента И 58 разрешает работу элементов 69 и 70.

После чтения или записи очередного байта информации из содержимого счетчика 66 вычитается единица, что соответствует приращению адреса по отношению к адресации узла 16.

При работе с узлом 14 непосредственно узлом 16 обнуляется регистр 64 и сигнал БОБ отсутствз ет. В этом случае сигналы ЧТ ЗУ, ЗП ЗУ поступают в узел 14 через элементы И 61 и 62 соответственно.

изобретения

ду,первого блока управления, отличающееся тем, что, с не- лью повышения быстродействия, в него введены п блоков двунаправленной передачи данных и второй блок управления, причем первый вход-выход первого блока управления через общую шину ад- pjeca подключен, к информационным вхо- п блоков двунаправленной переда- Ци данных, к первому входу режима вто Fjoro блока управления, к информацион- ijoMy входу блока ввода-вьшода, второй 1|ход-выхо первого блока управления . ереэ общую шину данных подключен к р нформационному входу-выходу блока вода-вывода, к второму входу режима

J Toporo блока управления и к первым нформационным входам выходам п блоков двунаправленной передачи данных, третий вход-выход первого блока уп- | авления через общую ишну управлеУшя Подключен к управляющему входу-выхо- блока ввода-вывода, к входу-выход JBToporo блока управления и к первым управляющим входам-выходам п блоков, йвунаправленной передачи.данных, вторые информаци.онные входы-выходы блоков двунаправленной передачи данных с первого по п-й подключены соответ- ртвепно к информационным входам вы- 5х,одам решающих блоков с первого по Т1-й, вторые управляюБще входы- выхо- ды блоков двунаправленной передачи данных с первого по п-й подключены соответственно к управляющем входам- выходам решаюи их блоков с первого по п-й, информационные выходы блоков двунаправленной передачи данных с первого по п-й подключены соответственно к информационным входам решаю1цих блоков с первого по п-й, при этом .в первый блок управления введен узел двунаправленной передачи данных, информационный вход, первый информационньй вход-выход и управляющий вход-выход узла двунаправленной передачи данных подключены соответственно к первому, второму и третьему входам-выходам первого блока управления, второй информационны вход-выход узла двунаправленной передачи данных подключен к информа- i oHJTOMy входу-выходу узла оперативной памяти, первьш управляющий, второй управляющий и информационный выходы узла двунаправленной передачи данных подключены соответственно к входам чтения, записи и адреса узла оперативной памяти, выход которого

0

5

0,

5

255710

подключен к управляющему входу узла двунаправленной передачи данных.,

35

40

45

50

55

ленной передачи данных, к первому . входу второго элемента ИЛИ и к первому входу режима двунаправленного элемента буферной памяти, второй выход регистра подключен к второму входу первого элемента ИЛИ и третьему входу шестого элемента И, выход кото рого объединен с выходом четвертого элемента И и подключен к второму уп- равляющему выходу узла двунаправленно передачи данных, к второму входу второго элемента ИЛИ и второму входу режима двунаправленного элемента буферной памяти, выход второго элемента ИЛИ подключен к второму входу седьмого элемента И, выход которого подключен к вычитающему входу счетчика, вто рой выход дешифратора подключен к входу чтения регистра, выход первого элемента ИЛИ подключен к второму входу второго элемента И,

ду счетчика, вход считьшания кото- , рого подключен к второму выходу дешифратора, четвертый адресный вход первого узла постоянной памяти объ- ;единен с входом записи счетчика с помощью монтажного ИЛИ, пятый и шестой адресные входы первого узла постоянной памяти, вход записи-считывания регистра и с второго по пят1й выходы второго узла постоянной памяти объединены в жгут и подключены к входу- выходу второго блока управления.

0 5 0

5 Ос Q

0

вленньш и однонаправленный узлы бу;- ферной памяти, при этом первый ин- формациониьш вход-выход блока двунаправленной передачи данных подключен к информационному входу регистра, к первому информационному входу- выходу двунаправленного узла буферной памяти и к информационному входу счетчика, выход которого подключен к информационному входу однонаправленного узла буферной памяти, выход которого подключен к информационному вькоду блока двунаправленной передачи данных, второй информационный вход-выход которого подключен к второму информационному входу-выходу двунаправленного узла буферной памяти, информац1{онный вход блока двунаправленной передачи данных подключен к входам первого и второго дешифраторов, выходы первого и второго дешифраторов подключены соответственно к входам считывания регистра и счет-

чика, входы записи которых объединены с-помощью монтажного -ИЛИ, выход третьего дешифратора подключен к информационному входу триггера, вход уста- .новки в О которого подключен к пер- выходу регистра, второй выход которого подключен к первым входам первых элементов ИЛИ и И., прямой выход последнего подключен к первому входу режима двунаправленного узла буферной памяти и к первому входу второго элемента ИЛИ, выход которого подключен к первому входу второго элемента И, выход которого подключен к вычитающему входу счетчика, третий выход регистра подключен к первому входу третьего элемента .И и к второму входу первого элемента ИЛИ, выход которого подключен к входу элемента НЕ,

|выход третьего элемента И подключен

к второму входу режима двунаправленного узла буферной памяти и второму

.входу второго элемента ИЛИ, инверс- ньш вход первого элемента И подключен к второму входу третьего элемента И, к первому входу четвертого элемента И и к первому входу пятого элемента И, выход которого подключен к входу режима однонаправленного узла буферной памяти, к второму входу второго элемента И и к третьему входу режима двунаправленного узла буферной памяти, третий вход третьего элемента И, вторые входы четвертого, пятого и

.первого элементов И объединены с помощью монтажного ИШ1, четвертый вход

третьего элемента И третьи входы четвертого, первого элементаИ ипя того элементов И объединены с помощью монтажного ИЛИ, выход четвертого элемента И, пятый.вход третьего элемента И, четвертый вход первого элемента И, третий вход третьего элемента И, вход записи регистра и выход триггера объединены в жгут и подключены к первому управляющему входу- выходу блока двунаправленной переда

чи данных, четвертый вход четвертого элемента И, выход третьего элемента И, четверть вход третьего элемента И, прямой выход первого элемента И, выход элемента НЕ, четвертьй, пя- тьш, шестой выходы регистра, вход третьего дешифратора и синхровход триггера объединены в жгут и подключены к второму управляющему входу- выходу блока двунаправленной передачи данных.

зт

ПЗЛ)(В

Готов

т

0

За}(бйт Jos WJ JrTJy

и.гЛ

блок коммуfTJauuu.3

fstnot

«4

Рмг.5

CSpoc Готовн

3ct)cff ПРЕ Cmpoff сост

2

Г/

Г2

г

Готод

СЗЬос

CuHXf

Адрес

3

)

ПЗАХВ

44

ПЗАХВ

ППРЕ

чтву

Данные j

Ожидание

Синхр

9и.г.6

Системна магистраль

B/f

чтп

7

ъ

«

8К

«

PU9.8

зпву

ЧТВУ

ППР

вк

ПРВ

ЗПР

зпре

Л,

в

V

ВК

/7Я

зт

ЗПРЕ

-г

ЗпВУ ЧтВУ

пире гпрЕ

ЗПР

анные

t)

Аанние

56

:

ш

I

«

Ч

г

Управление

данные

вк:

f7P

Л

Адрес

и

9иг,9

Готов

57

грГ

БОБ

ЦГЗУ

59

о

- Щ

Bit65

МА

KFii

romoS

t

чтзу

ЗПЗУ

69

Мй

67

ftJ

LJr

551

НА

Л

Фиг. 10

( Вход 3

Е

Ula

ЗАХВАЪ 0

нет.

БОБ :

//75У

J Ji r ff

Да

//f/77

ЧТЗУ: / ЗЛЗУ: /

ГУ 5

ФигЛ

v

СЧ

5J

еФие.13

U Xf,1 XI.2

l,m-i ,tn X

9иг. /4

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-06—Подача