t

СП

О9 4:

сд

сд

Изобретение относится к вычислительной технике и может быть использовано для контроля хода программы цифровых ЭВМ.

Целью из,обретения является повышение оперативности контроля.

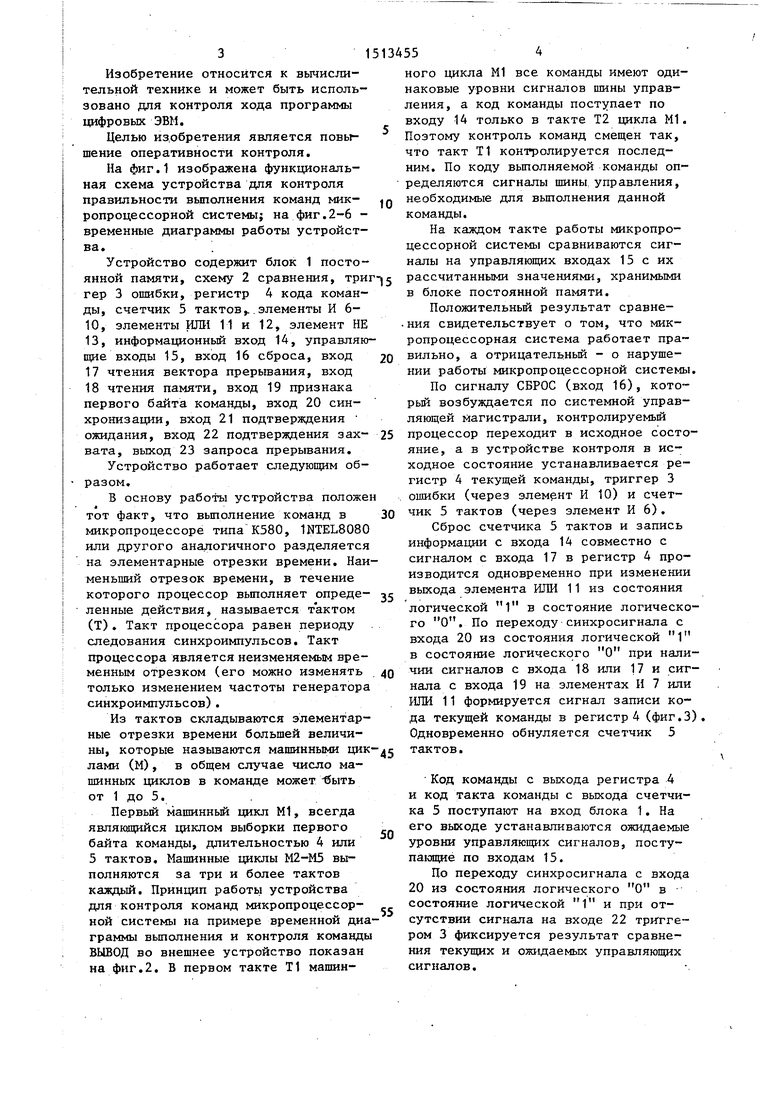

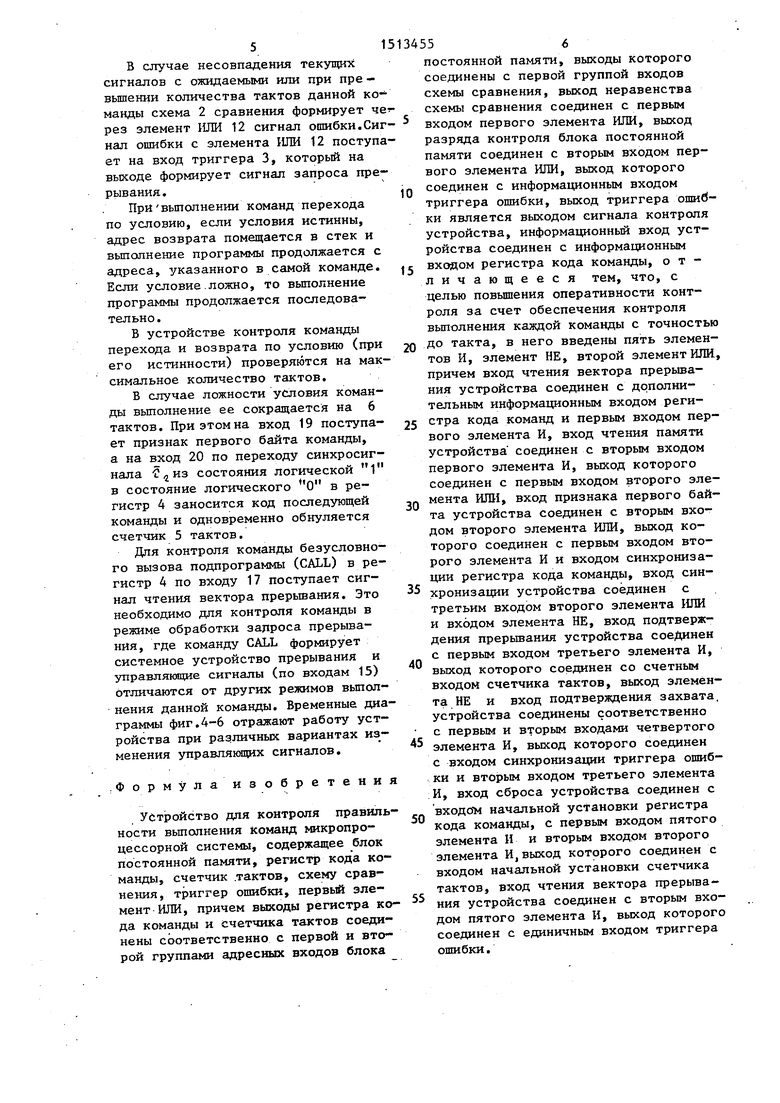

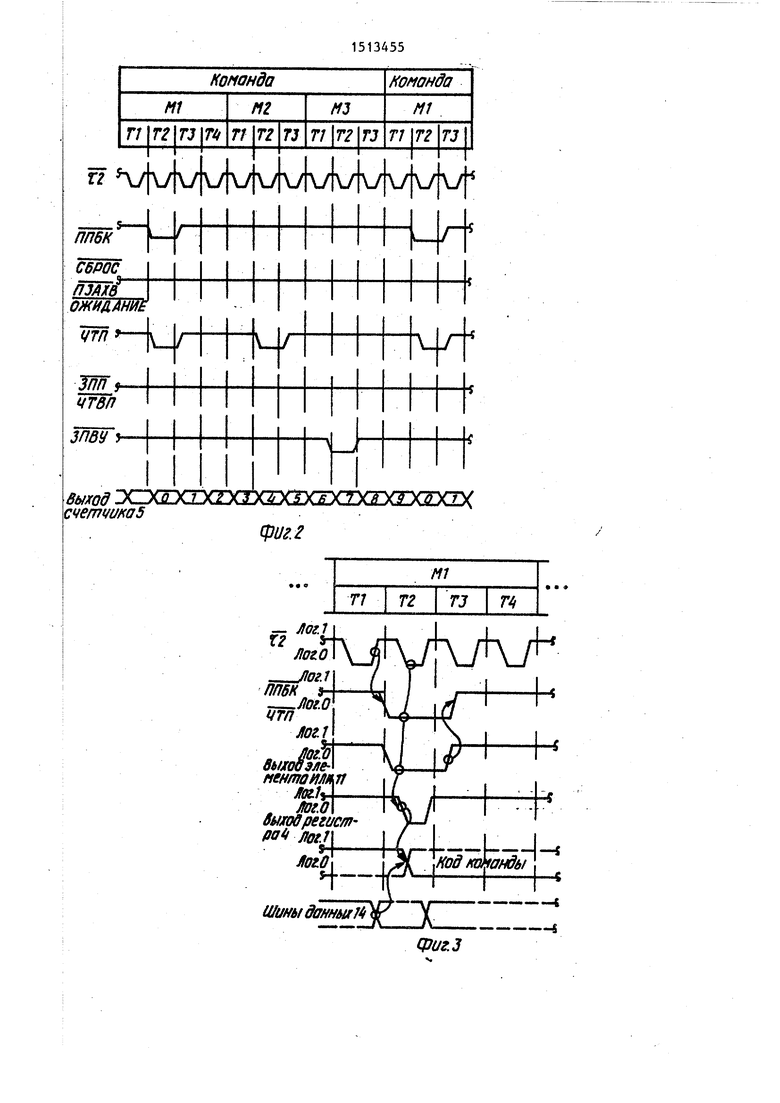

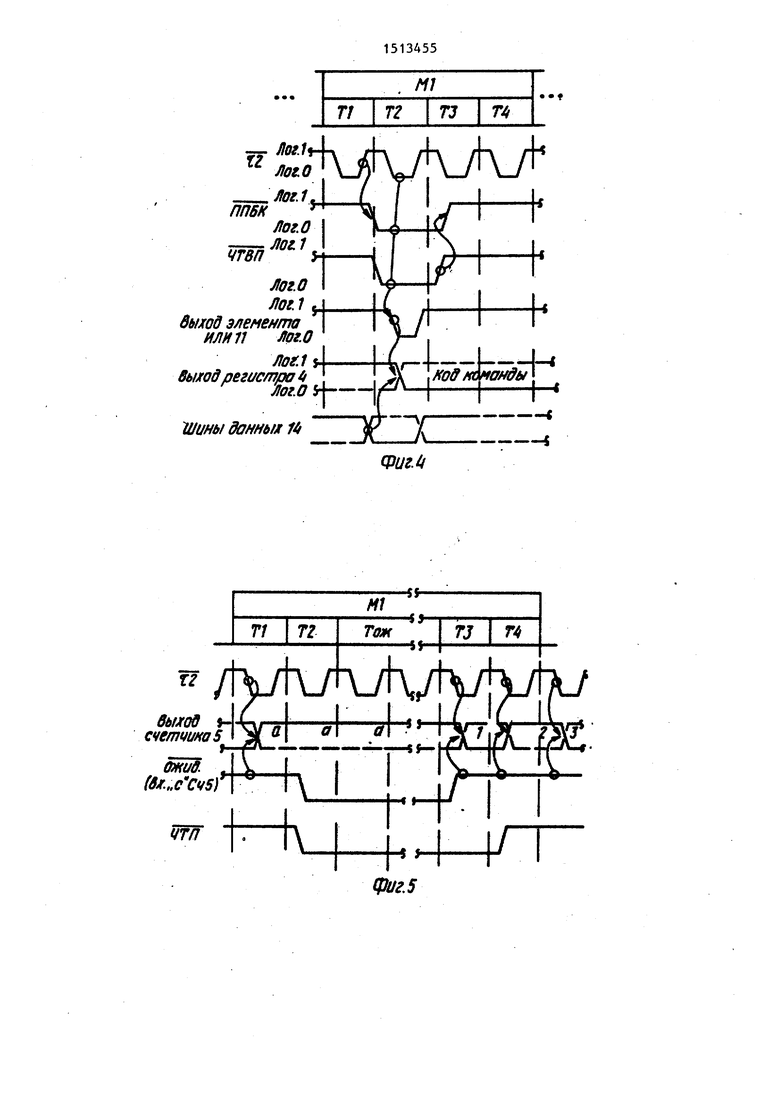

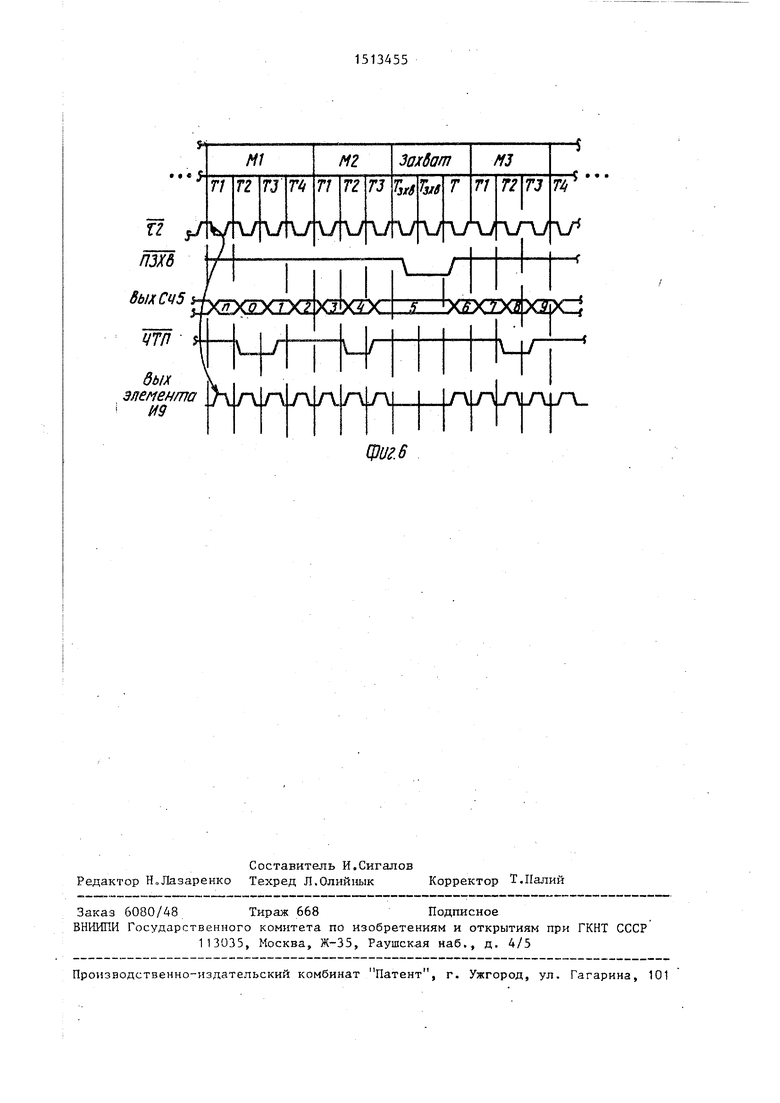

На фиг.1 изображена функциональная схема устройства для контроля правильности выполнения команд микропроцессорной системы; на фиг.2-6 - временные диаграммы работы устройства.

Устройство содержит блок 1 постоянной памяти, схему 2 сравнения, триг гер 3 ошибки, регистр 4 кода команды, счетчик 5 тактов,, .элементы И 6- 10, элементы ИЛИ 11 и 12, элемент НЕ 13, информационньш вход 14, управлякг

5

0

ного цикла Ml все команды имеют одинаковые уровни сигналов шины управления, а код команды поступает по входу 14 только в такте Т2 цикла Ml. Поэтому контроль команд смещен так, что такт Т1 контролируется последним. По коду вьшолняемой команды определяются сигналы шины управления, необходимые для выполнения данной команды.

На каждом такте работы микропроцессорной системы сравниваются сигналы на управляющих входах 15 с их рассчитанными значениями, хранимыми в блоке постоянной памяти.

Положительньй результат сравне- ния свидетельствует о том, что микропроцессорная система работает пра

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля хода программы | 1987 |

|

SU1451703A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

Изобретение относится к вычислительной технике и может быть использовано для синтаксического контроля выполнения команд микропроцессорной системы. Цель изобретения - повышение оперативности контроля за счет обеспечения контроля выполнения каждой команды с точностью до такта. Устройство содержит блок 1 постоянной памяти, схему 2 сравнения, триггер 3 ошибки, регистр 4 кода команды, счетчик 5, элементы И 6-10, элементы ИЛИ 11 и 12, элемент НЕ 13. Использование устройства позволяет расширить возможности по обнаружению ошибок хода программы с точностью до неправильно выполненной команды. 6 ил.

щие входы 15, вход 16 сброса, вход

17чтения вектора прерьтания, вход

18чтения памяти, вход 19 признака первого байта команды, вход 20 синхронизации, вход 21 подтверждения ожидания, вход 22 подтверждения захвата, выход 23 запроса прерывания.

Устройство работает следующим образом.

В основу работы устройства положе

тот факт, что выполнение команд в микропроцессоре типа К580, 1NTEL8080 или другого аналогичного разделяется на элементарные отрезки времени. Наименьший отрезок времени, в течение которого процессор выполняет опреде- ленные действия, называется тактом (Т). Такт процессора равен периоду следования синхроимпульсов. Такт процессора является неизменяемым временным отрезком (его можно изменять только изменением частоты генератора синхроимпульсов).

Из тактов складываются элементарные отрезки времени большей величины, которые назьшаются машинными цик лами (М), в общем случае число машинных циклов в команде может -быть от 1 до 5.

Первый машинньй цикл Ml, всегда являющийся циклом выборки первого байта команды, длительностью 4 или 5 тактов. Машинные циклы М2-М5 выполняются за три и более тактов каждый. Принцип работы устройства для контроля команд микропроцессорной системы на примере временной диаграммы выполнения и контроля команды ВЫВОД во внешнее устройство показан на фиг.2. В первом такте Т1 машин

ВИЛЬНО, а отрицательньй - о нарушении работы микропроцессорной системы. По сигналу СБРОС (вход 16), кото- рьй возбуждается по системной управляющей магистрали, контролируемьм процессор переходит в исходное состо05 О

0

5

яние, а в устройстве контроля в исходное состояние устанавливается регистр 4 текущей команды, триггер 3 ошибки (через элемент И 10) и счетчик 5 тактов (через элемент И 6).

Сброс счетчика 5 тактов и запись информации с входа 14 совместно с сигналом с входа 17 в регистр 4 производится одновременно при изменении выхода элемента ИЛИ 11 из состояния

логической 1 в состояние логического О. По переходу синхросигнала с входа 20 из состояния логической 1 в состояние логического О при наличии сигналов с входа 18 или 17 и сигнала с входа 19 на элементах И 7 или ИЛИ 11 формируется сигнал записи кода текущей команды в регистр 4 (фиг.З). Одновременно обнуляется счетчик 5 тактов.

Код команды с выхода регистра 4 и код такта команды с выхода счетчика 5 поступают на вход блока 1. На его выходе устанавливаются ожидаемые уровни управляющих сигналов, поступающие по входам 15.

По переходу синхросигнала с входа 20 из состояния логического О в состояние логической 1 и при отсутствии сигнала на входе 22 триггером 3 фиксируется результат сравнения текущих и ошщаемых управляющих сигналов.

в случае несовпадения текущих сигналов с ожидаемыми или при пре - вышении количества тактов данной команды схема 2 сравнения формирует ч рез элемент ИЛИ 12 сигнал ошибки.Синал ошибки с элемента ИЛИ 12 поступет на вход триггера 3, которьй на выходе формирует сигнал запроса прерывания.

ПрИ выполнении команд перехода по условию, если условия истинны, адрес возврата помещается в стек и вьшолнение программы продолжается с адреса, указанного в самой команде. Если условие.ложно, то вьшолнение программы продолжается последовательно.

В устройстве контроля команды перехода и возврата по условию (при его истинности) проверяются на максимальное количество тактов.

В случае ложности условия команды вьшолнение ее сокращается на 6 тактов. При этом на вход 19 поступает признак первого байта команды, а на вход 20 по переходу синхросигнала L из состояния логической 1 в состояние логического 0 в регистр 4 заносится код последующей команды и одновременно обнуляется счетчик 5 тактов.

Для контроля команды безусловного вызова подпрограммы (CALL) в регистр 4 по входу 17 поступает сигнал чтения вектора прерьшания. Это необходимо для контроля команды в режиме обработки запроса прерывания, где команду CALL формирует системное устройство прерывания и управляющие сигналы (по входам 15) отличаются от других режимов вьтол- нения данной команды. Временные диаграммы фиг.4-6 отражают работу устройства при различных вариантах изменения управлянщих сигналов.

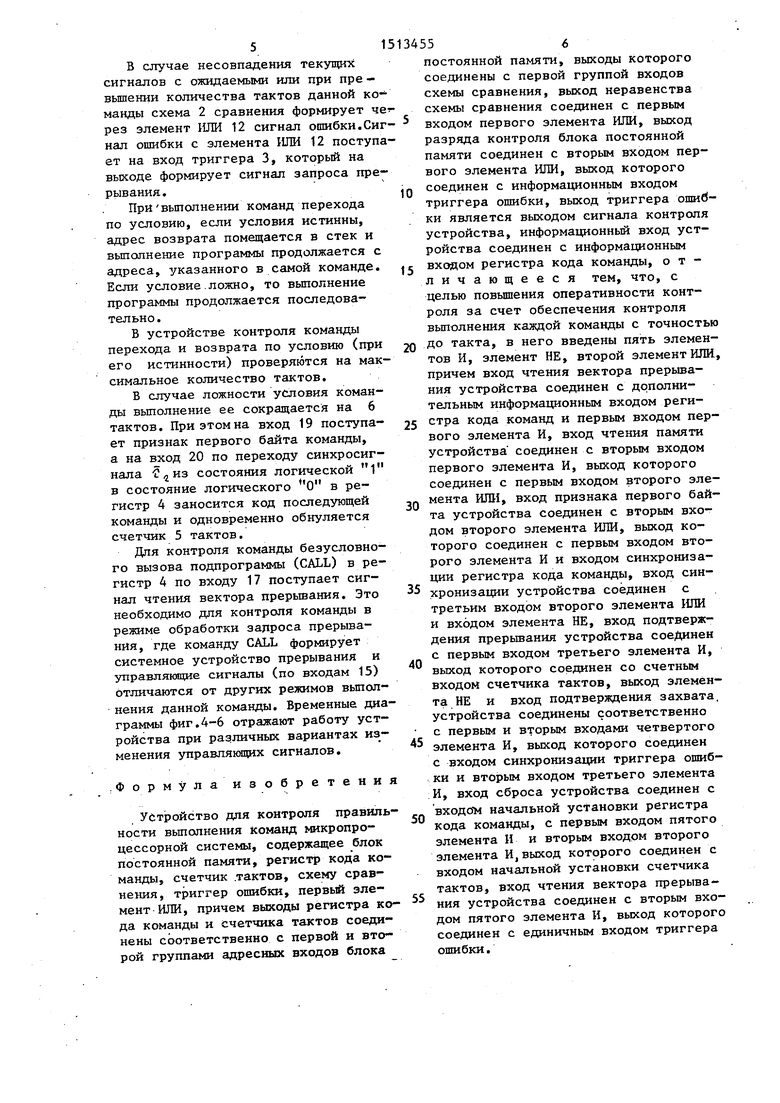

.Формула изобретения

Устройство для контроля правильности вьшолнения команд микропроцессорной системы, содержащее блок постоянной памяти, регистр кода команды, счетчик .тактов, схему сравнения, триггер ошибки, первый элемент ИЛИ, причем выходы регистра кода команды и счетчика тактов соединены соответственно с первой и второй группами адресных входов блока

- 10

15

20

25

134556

постоянной памяти, выходы которого соединены с первой группой входов схемы сравнения, выход неравенства схемы сравнения соединен с первым входом первого элемента ИЛИ, выход разряда контроля блока постоянной памяти соединен с вторым входом первого элемента ИЛИ, выход которого соединен с информационным входом триггера ошибки, выход триггера ошибки является выходом сигнала контроля устройства, информационньш вход устройства соединен с информационным входом регистра кода команды, отличающееся тем, что, с целью повышения оперативности контроля за счет обеспечения контроля выполнения каждой команды с точностью до такта, в него введены пять элементов И, элемент НЕ, второй элемент ИЛИ, причем вход чтения вектора прерывания устройства соединен с дополнительным информационным входом регистра кода команд и первым входом первого элемента И, вход чтения памяти устройства соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, вход признака первого байта устройства соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И и входом синхронизации регистра кода команды, вход синхронизации устройства соединен с третьим входом второго элемента ИЛИ и входом элемента НЕ, вход подтверждения прерывания устройства соединен с первым входом третьего элемента И, выход которого соединен со счетным входом счетчика тактов, выход элемента НЕ и вход подтверждения захвата, устройства соединены соответственно с первым и вторым входами четвертого элемента И, выход которого соединен с входом синхронизации триггера ошибки и вторым входом третьего элемента И, вход сброса устройства соединен с входом начальной установки регистра кода команды, с первым входом пятого элемента И и вторым входом второго элемента И,выход которого соединен с входом начальной установки счетчика тактов, вход чтения вектора прерывания устройства соединен с вторым входом пятого элемента И, выход которого соединен с единичным входом триггера ошибки.

30

35

40

45

50

55

Команда

Ml

т

мз

Т2

TJ

fit

T1

тг

73

Т1 Т2

Vy|vt 7| 7

-г

вшод cvemw ffS

фиг. 2

- ш,

Лого

/1ог.1

ППбК

Q7n

, Ш,0 выходрегис/п- ffff Лог.г

Шиныданнш

номонда

т

ТЗ

Т1

тг

73

-г

Фиг,3

F

Ттк

Лог.1 Лог. О Лог.1

Лог. О

.О Лог.1

выход элемента или 11 лрг.О

Ло.1 я

Выходрегис/nfxj лог.О 5

WuHbi данных /4

12

вылод счет WHO 5

ФкиО. (SJF...C CVS}

WfT

фиг,5

Ц) и г. 6

| Авторское свидетельство, СССР № 1019451, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-11-17—Подача