fiaMHTH соединены с выходами второго |соммугатора, входы первой и второй Групп которого соединены соответст- Ьенно с выходами второго регистра и соответствующими выходами первого регистра, управляюп1ий вход второго |соммутатора соединен с вторым управ- ,|п;яющкм входом первого блока памяти

и седьмым выходом блока управления, третий вход которого соединен с выходом вычитающего счетчика, ирформа- ционные входы второго регистра соединены с одними из входов первого коммутатора, четвертый вход блока управления прдключен к установочному входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Устройство для сопряжения | 1985 |

|

SU1278861A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

I 1

I Изобрет ёние относится к вычисли- {тельной технике,

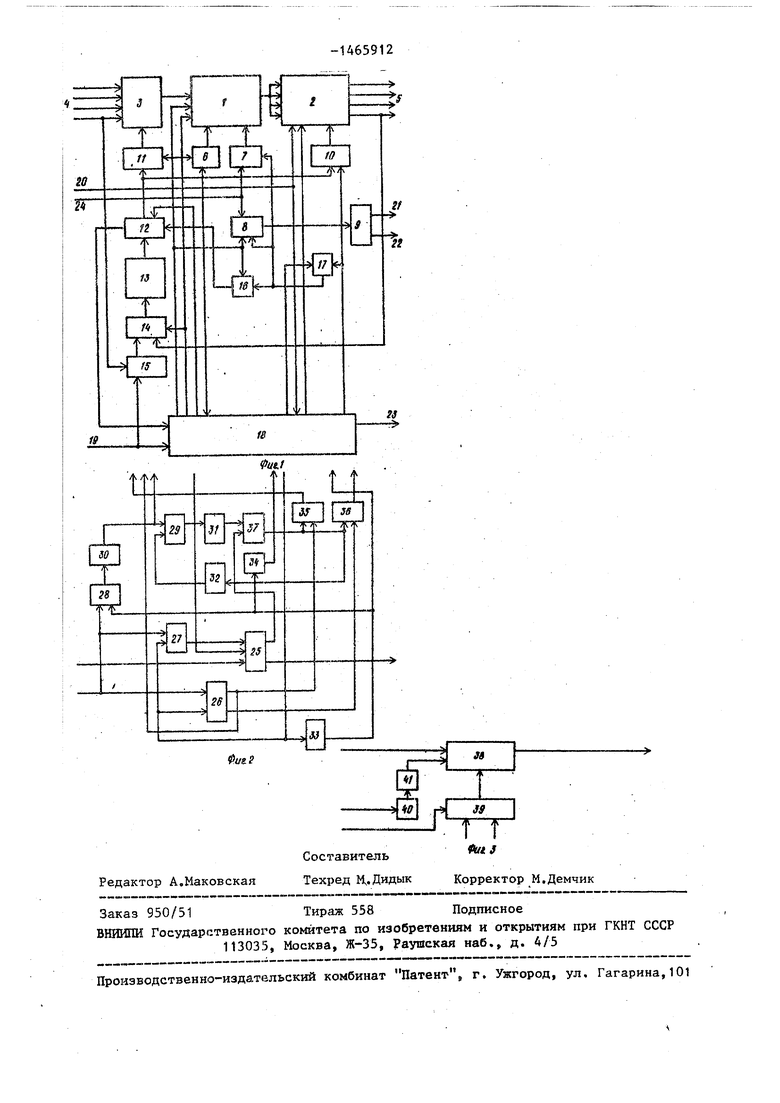

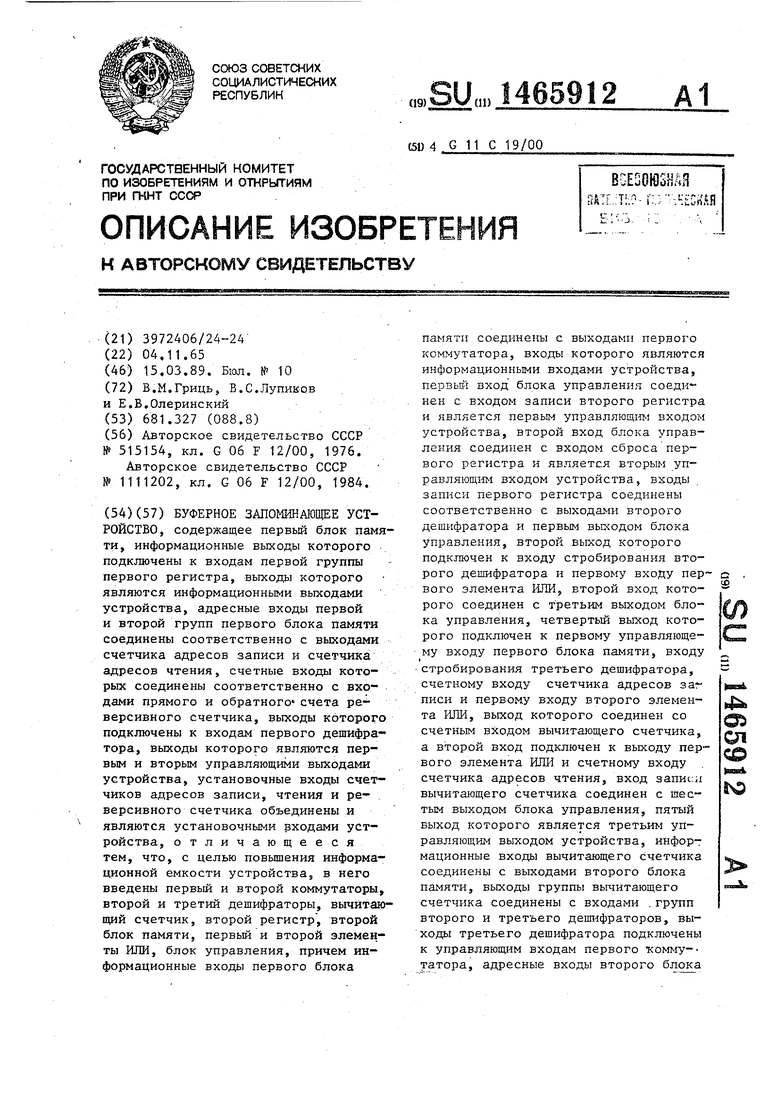

I Цель изобретения повышение ин- |формационной емкости устройства. I На фиГв1 приведена структурная схема буферного запоминеоощего |ройства; на фиг.2 - структурная схе |ма блока управления; на фиг.З - то- же, блока пакяти.

I Устройство содержит первый блок 1 памяти, первый регистр 2, первьй коммутатор 3, информационные входы i4 и выходы 5j счетчик 6 адресов за- писи, счетчик 7 адресов .чтения, рб; версивный счетчик 8, первый 9, вто рой 10 и третий 11 дешифраторы, ВЫ читающий счетчик 12, второй блок 13 Iпамяти, второй коммутатор 14, второ регистр 15, второй 16 к первый 17 элементы ИЛИ, блок 18 утфавления, входы 19,;,20 управления,, выходы 21 23 управления, вход 24 установки, I В одном из вариантов блок 18 управления может содержать триггеры 25, 26, элементы WE 27-29 элементы 30-34 задержки, элементы 35-37,

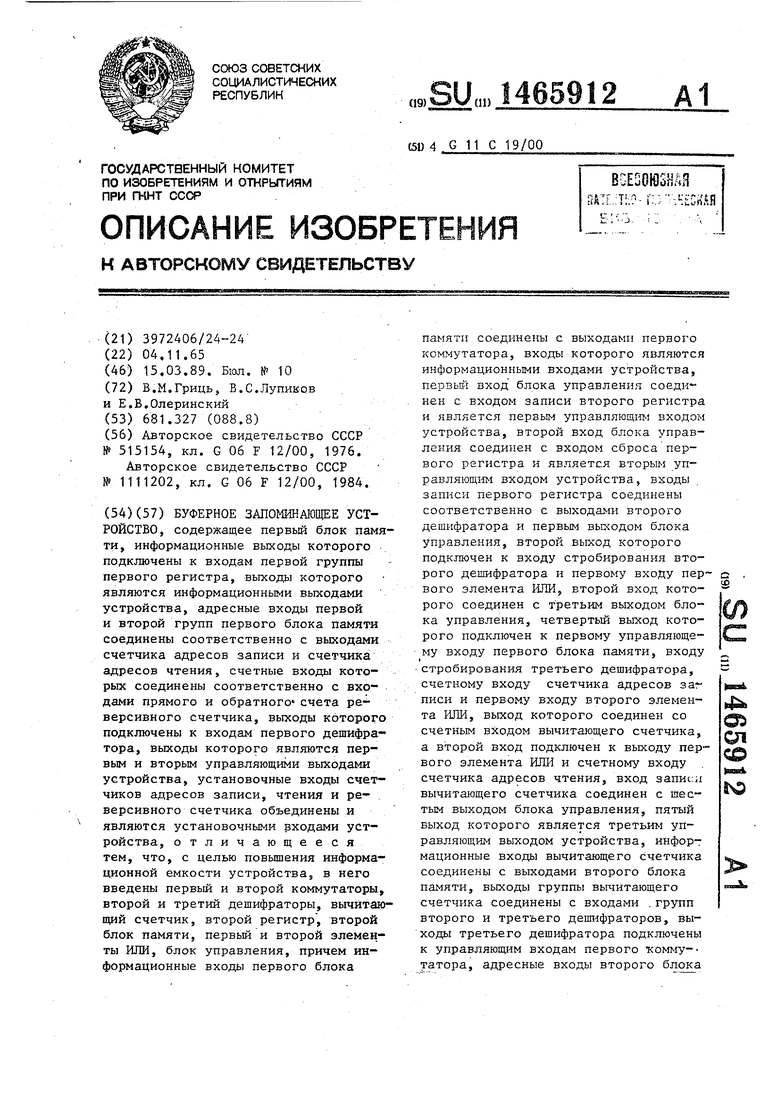

В одном из вариантов блок 1 памя ти может содержать накопитель 38, коммутатор 39, элемент 40 задержки и формирователь 41,

Устройство работает следующим образом.

Перед началом работы сигналом по входу 24 установки счетчики 6-8 и триггер 25 блока 18 управления устанавливаются в нулевое состояние.

Высокий уровень на выходе 23 упг равления устройства свидетельствует о том, что устройство готово к выпонению одной из Д5УХ операций запис данных или чтения данныгс. Низкий.

0

5

0

5

0

5

0

уровень сигнала на выходе 23 свидетельствует о том, что устройство занято выполнением операции и обращение к нему запрещено,

Сигнгиш на выходах 21 и 22 управления устройства, т.е. на выходах дешифратора 9, являются сигналами состояния блока памяти - пуст и заполнен соответственно.

При выполнении операции записи записываемые данные поступают на входы 4 устройства в сопровождении сигнала запроса на входе 19. Сигнал запроса на входе 19 переписывает данные с первой группы входов 4 (код адреса объекта) в регистр 15 и пос- тупает на вход блока 18 управления, где устанавливает в единичное состояние триггер 26 и, проходя через элемент ШШ 27, устанавливает в единичное состояние триггер 25. Сигнал запроса записи поступает также на вход элемента, ШШ 28 блока 18 управления и, проходя элемент 30 задержки, на вход записи счетчика 12. По этому сигналу в счетчик 12 записывается код длины сообщения, подлежащего записи в блок 1 памяти. Коды длины сообщения считываются из блока 13 памяти (постоянное запоминающее устройство) по адресу, хранящемуся на выходах регистра 15, через открытый для не го в данный момент коммутатор J14. Сигнал на выходе элемента 30 задержки, проходя через элемент ИЛИ 29, элемент 31 задержки, элементы И 37, 35, поступает на вход управления блока 1 памяти и на вход стро- бирования дешифратора 11, выходной Сигнал которого подключает соответствующую группу входов 4 через комму

3

татор 3 к информационным, входам блока 1 памяти. Высокий уровень сигнал на прямом выходе триггера 25 подклю чает к адресным входам накопителя 38 блока 1 памяти через коммутатор за выходы счетчика 6 адресов записи Сигнал на входе управления блока 1 памяти, проходя через элемент АО задержки и формирователь 41, осущест- .вляет запись в накопитель данных по адресу, сформированному на счетчике 6. Задрим фронтом сигнала на выходе элемента И 35 производится модификация (добавляется единица) счетчик 6 адресов записи и счетчика 8 объем Задним фронтом этого сигнала, проходящего через элемент ИЛИ 18, производится модификация (вычитается единица) счетчика 12. Сигнал на выходе элемента И 37, проходя через элемен 32 задержки, элемент ИЛИ 29, вызывае появление на выходе элемента И 35 следующего сигнала опроса дешифратора 11, по которому затем производится запись в блок 1 памяти данных с второй группы входов 4. Запись данных в этом случае производится аналогично описанному вьше. Циклы записи повторяются до тех пор, пока на

выходе заема счетчика 12 не появится сигнал, который установит в нулевое состояние триггер 25 блока 18 управления, высокий уровень сигнала на выходе которого свидетельствует о готовности устройства к выполнению следующей операции записи или чтения данных.

При вычислении операции чтения данных сигнал запроса поступает на вход 20 устройства, по которому производится сброс в нулевое состояние

0

5

0

триггера 2, установка в единичное состояние триггера 25 и в нулевое состояние - триггера 26 блока 18 управления. Низкий уровень сигнала на прямом выходе триггера 26 подключает через коммутатор 39 к адресным вхддам накопителя 38 выходы счетчика 7 адресов чтения. Сигнал с входа 20, проходя элемент 33 задержки, осуществляет запись считанной из блока 1 памяти первой части сообщения (адресный признак) в первую группу разрядов регистра 2, выходные сигналы с которых через открытый для них кЬг-шутатор 14 поступают на адресные входы блока 13 памяти. Сигнал с выхода элемента 30 задержки переписывает считанный из блока 13 памяти код длины сообщения с счетчик 12, после чего сигналом с выхода элемента 34 з.адержки через элементы ИЛИ 16, 17 производится модификация счетчика 7 адресов чтения (добавляется

5 единица), счетчика 8 (вычитается единица) и счетчика 12 (вычитается единица). Сигнал с.выхода элемента 30 задержки через элемент ИЛИ 29, элемент 31 задержки, элементы И 37,

0 36 воздействует на вход стробирования дешифратора 10, выхрдной сигнал которого записывает следующую часть со- . общения во вторую грз ппу разрядов регистра 2, после чего производится

5 аналогичная описанной вьше модификация содержимого счетчиков 7, 8, 12. Процесс чтения послед тощих частей сообщения продолжается до появления сигнала на выходе заема счетчика

0 12, который сбросит в исходное состояние триггер 25 блока 18 управления.

Редактор А.Маковская

Техред Мч.Дидык Корректор М.Демчик

Заказ 950/51Тир 1ж 558 Подписное

ВНИШШ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина,101

| Буферное запоминающее устройство | 1974 |

|

SU515154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-15—Публикация

1985-11-04—Подача