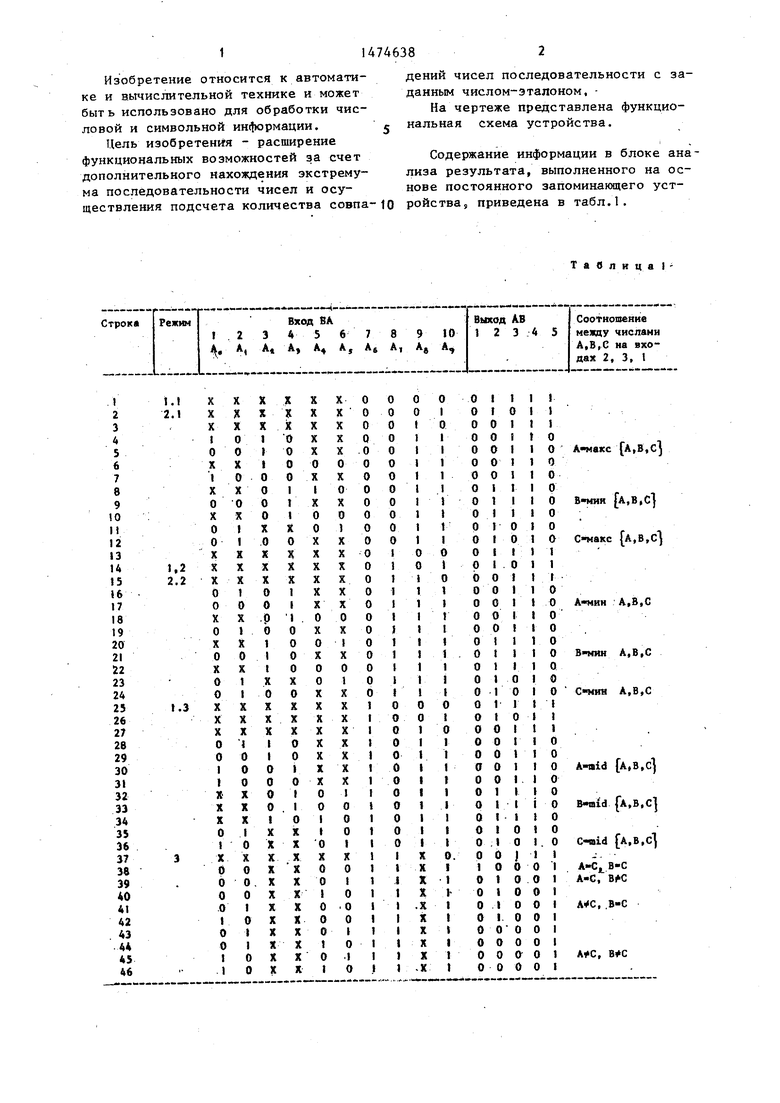

Т а в л и ц а I

Устройство для обработки информации содержит первый 1 , второй 2 и третий 3 информационные входы, вход i режима,первый 5 и второй 6 выходы, первую 7 и вторую 8 схемы сравнения, коммутатор 9 и блок 10 анализа результата, третью схему II сравнения,

первый 12, второй 13 и третий 14 регистры, накапливающий сумматор 15, первый 16 и второй 17 элементы И, коммутатор 18 и вход 19 синхронизации устройства.

Устройство работает следующим образом.

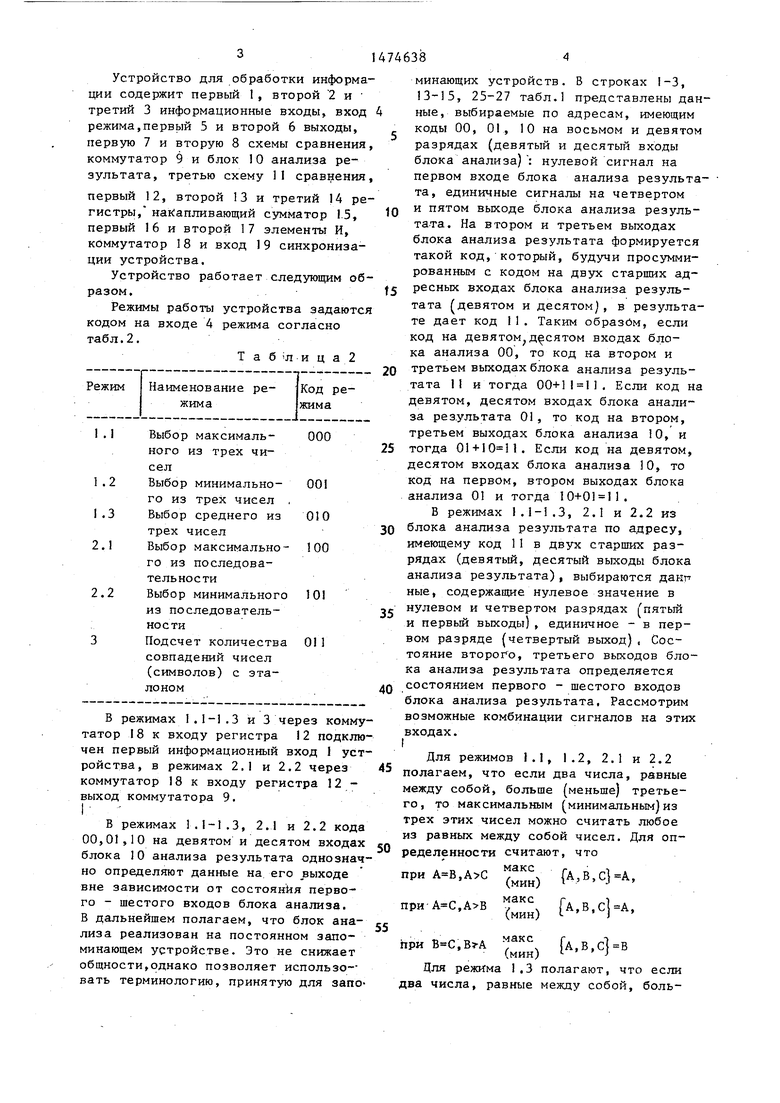

Режимы работы устройства задаются кодом на входе 4 режима согласно табл.2.

Таб лица2

1 .1 Выбор максималь- 000 ного из трех чисел

1.2Выбор минимально- 001 го из трех чисел ,

1.3Выбор среднего из 010 трех чисел

2.1Выбор максимально- 100 го из последовательности

2.2Выбор минимального 10 из последовательности

3 Подсчет количества 011 совпадений чисел (символов) с эталоном

- - - - - - .А .«. - -™ -- .„..- - .« . ,

В режимах 1.1-1.3 и 3 через коммутатор 18 к входу регистра 12 подключен первый информационный вход 1 устройства, в режимах 2.1 и 2.2 через коммутатор 18 к входу регистра 12 - выход коммутатора 9. I

В режимах 1.1-1.3, 2.1 и 2.2 кода 00,01,10 на девятом и десятом входах блока 10 анализа результата однозначно определяют данные на его выходе вне зависимости от состояния первого - шестого входов блока анализа. В дальнейшем полагаем, что блок анализа реализован на постоянном запоминающем устройстве. Это не снижает общности,однако позволяет использо- вать терминологию, принятую для запоминающих устройств. В строках 1-3, 13-15, 25-27 табл.1 представлены данные, выбираемые по адресам, имеющим коды 00, 01, 10 на восьмом и девятом разрядах (девятый и десятый входы блока анализа) : нулевой сигнал на первом входе блока анализа результата, единичные сигналы на четвертом Q и пятом выходе блока анализа результата. На втором и третьем выходах блока анализа результата формируется такой код, который, будучи просуммированным с кодом на двух старших ад- $ ресных входах блока анализа результата (девятом и десятом), в результате дает код 11. Таким образом, если код на девятом;десятом входах блока анализа 00, то код на втором и 0 третьем выходах блока анализа результата 11 и тогда 00+11 11. Если код на девятом, десятом входах блока анализа результата 01, то код на втором, третьем выходах блока анализа 10, и 5 тогда 01+10 11. Если код на девятом, десятом входах блока анализа 10, то код на первом, втором выходах блока анализа 01 и тогда 10+01 11.

В режимах 1.1-1.3, 2.1 и 2.2 из 0 блока анализа результата по адресу, имеющему код 11 в двух старших разрядах (девятый, десятый выходы блока анализа результата), выбираются дани ные, содержащие нулевое значение в с нулевом и четвертом разрядах (пятый и первый выходы), единичное - в первом разряде (четвертый выход), Состояние второго, третьего выходов блока анализа результата определяется Q состоянием первого - шестого входов блока анализа результата, Рассмотрим возможные комбинации сигналов на этих

входах. I

Для режимов 1.1, 1.2, 2.1 и 2.2 полагаем, что если два числа, равные между собой, больше (меньше) третьего, то максимальным (минимальным)из трех этих чисел можно считать любое из равных между собой чисел. Для определенности считают, что

при , (А, В, С}-А,

макс г. ) (мин) ГА.В.

0

при ,

при ,Вт-А

(А,В,

макс (мин)

Для режима 1.3 полагают, что если два числа, равные между собой, боль51

ше fменьше третьего, то средними из этих трех чисел можно считать любое из двух равных между собой. Для определенности считают, что

при mid A,В,G А, при mid ЈА,В,с А, при mid А,В,с В

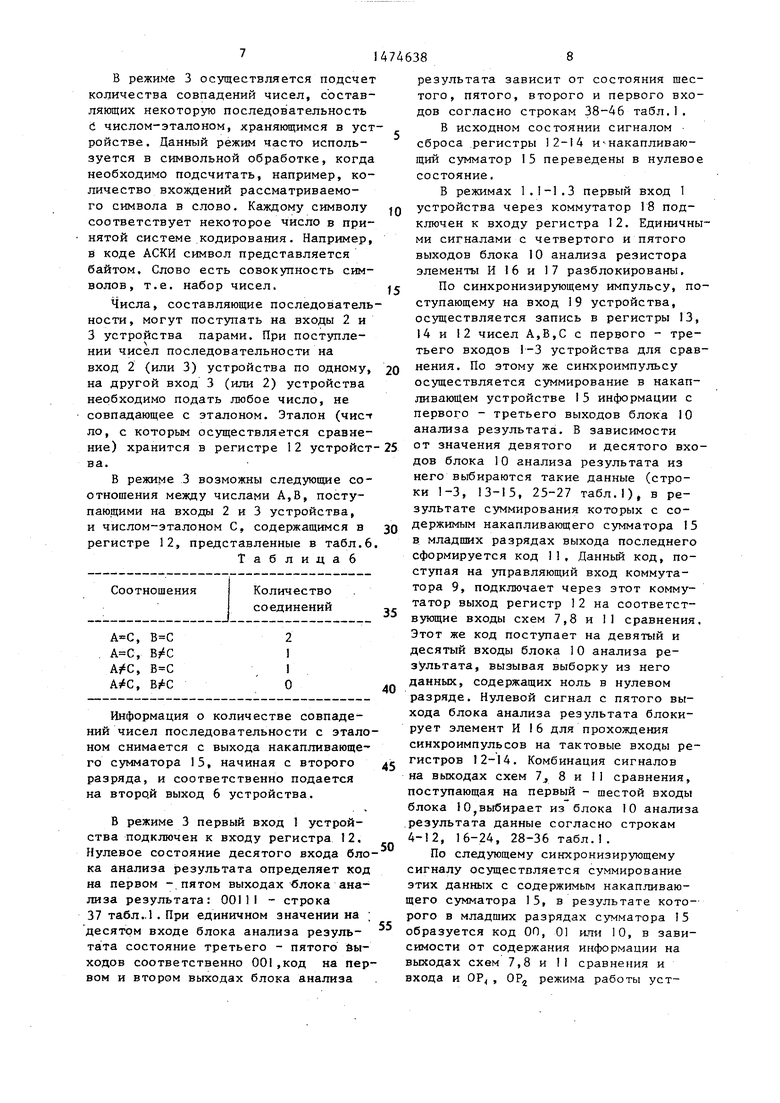

В табл. 3-5 представлены соотношения между числами А,В и С, однозначно определяющие соответственно максимальное, минимальное и среднее из этих чисел.

ТаблицаЗ

мин А,В,С

I

Таблица4 Соотношения

10

20

746386

Указанные соотношения определяют коды на выходах схем 7,8 и II сравнения и на первом - шестом входах бло- 5 ка анализа результата. Будем считать, что на первый, второй и третий информационные входы устройства поступают числа С,А,В. При коде 11 на девятом и десятом входах блока анализа результата значения первого - шестого входов блока анализа результата определяют такой код на втором и третьем выходах блока анализа результата, соединенных с младшими разрядами 15 выхода накапливающего сумматора 15, который, будучи просуммированным с . кодом 11, дает в результате код, обеспечивающий подключение на выход 5 устройства через коммутатор 9 соот- ветствующего регистра устройства. ,

Если на первом - шестом выходах блока анализа результата присутствует комбинация сигналов, соответствующая

макс тому, что А,миНч А,В,С, то с второго

Snid;

и третьего выходов блока анализа результата снимается код 01:11+01 00. Код 00 согласно табл.1 подключает через коммутатор 9 на выход 5 устройства выход регистра 13, содержащей число А.

Если на первом - шестом входах бло- 35 ка анализа результата присутствует комбинация сигналов, соответствующая

макс тому, что В ,минч А,В,С, то с втоSnid

40 рого и третьего выходов блока анализа результата снимается код 11:11+11 10. Код 10 согласно табл.1 подключает через коммутатор 9 на выход 5 устройства выход регистра 14.

25

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для обработки числовой и символьной информации. Цель изобретения - расширение функциональных возможностей за счет дополнительного нахождения экстремума последовательности чисел и осуществления подсчета количества совпадений чисел последовательности с заданным числом-эталоном. Устройство содержит схемы 7,8,11 сравнения, коммутаторы 9,18, блок 10 анализа результата, регистры 12,13,14, накапливающий сумматор 15, элементы И 16,17. Устройство позволяет проводить выбор максимального, минимального или среднего из трех чисел, осуществлять поиск экстремума последовательности чисел и подсчет количества совпадений чисел (символов), составляющих анализируемую последовательность (слово), с заданным числом - эталоном (с заданным символом). 1 ил., 6 табл.

ТаблицаЗ

mid А,В,С

Соотношения

Если на первом - шестом входах блока анализа результата присутствует комбинация сигналов, соответствующая

макс тому, что С ,минч А,В,С, то с второmid;

го и третьего выходов блока анализа результата снимается код 10:11+10 01. Код 01 согласно табл,1 подключит на выход 5 устройства через коммутатор 9 выход регистра 12. Информация в блоке анализа результата, составлена на основании описанного, представлена в строках 1-36 (табл.1).

В режиме 3 осуществляется подсчет количества совпадений чисел, составляющих некоторую последовательность и числом-эталоном, храняющимся в устройстве. Данный режим часто используется в символьной обработке, когда необходимо подсчитать, например, количество вхождений рассматриваемого СИМВОЛа В СЛОВО. КаЖДОМу СИМВОЛУ

соответствует некоторое число в принятой системе кодирования. Например, в коде АСКИ символ представляется байтом. Слово есть совокупность символов, т.е. набор чисел.

Числа, составляющие последовательности, могут поступать на входы 2 и 3 устройства парами. При поступлении чисел последовательности на вход 2 (или 3) устройства по одному, на другой вход 3 (или 2) устройства необходимо подать любое число, не совпадающее с эталоном. Эталон (чис-г ло, с которым осуществляется сравнение) хранится в регистре 12 устройст ва.

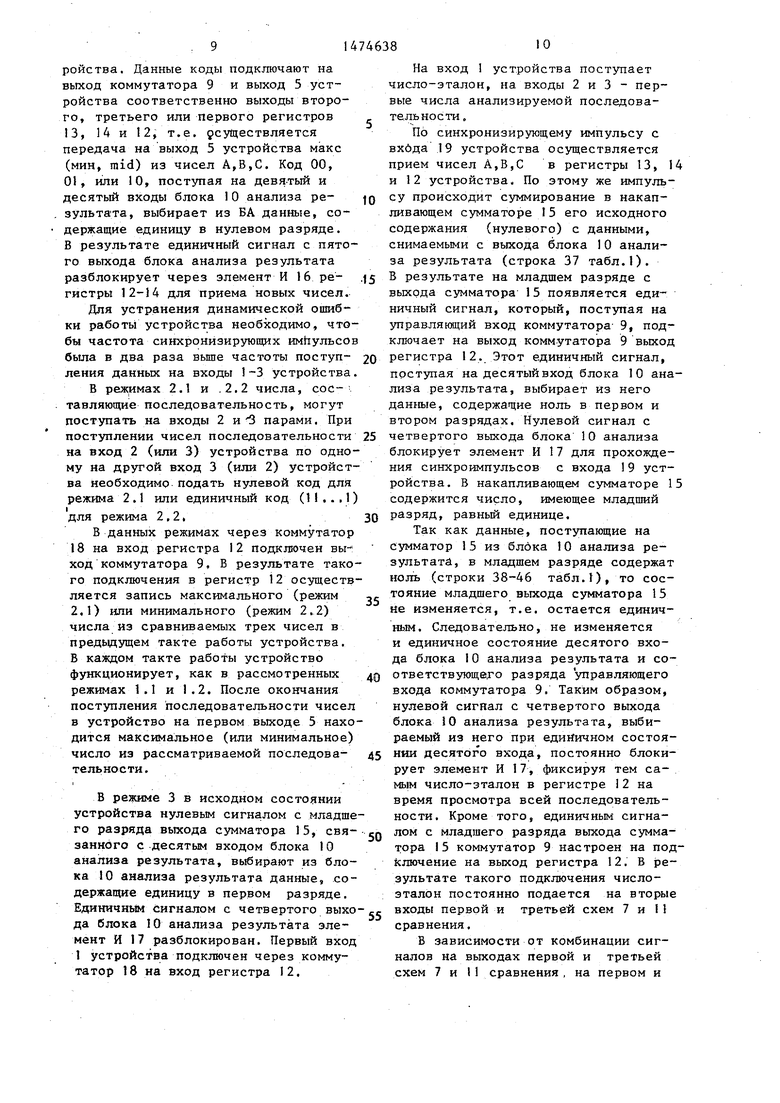

В режиме 3 возможны следующие соотношения между числами А,В, поступающими на входы 2 и 3 устройства, и числом-эталоном С, содержащимся в регистре 12, представленные в табл.6

Таблицаб

Информация о количестве совпадений чисел последовательности с эталоном снимается с выхода накапливающего сумматора 15, начиная с второго 45 разряда, и соответственно подается на второй выход 6 устройства.

В режиме 3 первый вход 1 устройства подключен к входу регистра 12. Нулевое состояние десятого входа блока анализа результата определяет код на первом - пятом выходах блока анализа результата: 00111 - строка 37 табл.1. При единичном значении на десятом входе блока анализа результата состояние третьего - пятого выходов соответственно 001,код на первом и втором выходах блока анализа

JQ

j

20 5

0

5

0

5

0

5

результата зависит от состояния шестого, пятого, второго и первого входов согласно строкам 38-46 табл.1.

В исходном состоянии сигналом сброса регистры 12-14 и-накапливающий сумматор 15 переведены в нулевое состояние.

В режимах 1.1-1.3 первый вход 1 устройства через коммутатор 18 подключен к входу регистра 12. Единичными сигналами с четвертого и пятого выходов блока 10 анализа резистора элементы И 16 и 17 разблокированы.

По синхронизирующему импульсу, поступающему на вход 19 устройства, осуществляется запись в регистры 13, 14 и 12 чисел А,В,С с первого - третьего входов 1-3 устройства для сравнения. По этому же синхроимпульсу осуществляется суммирование в накапливающем устройстве I5 информации с первого - третьего выходов блока 10 анализа результата. В зависимости от значения девятого и десятого входов блока 10 анализа результата из него выбираются такие данные (строки 1-3, 13-15, 25-27 табл.), в результате суммирования которых с содержимым накапливающего сумматора 15 в младших разрядах выхода последнего сформируется код 11, Данный код, поступая на управляющий вход коммутатора 9, подключает через этот коммутатор выход регистр 12 на соответствующие входы схем 7,8 и 11 сравнения. Этот же код поступает на девятый и десятый входы блока 10 анализа результата, вызывая выборку из него данных, содержащих ноль в нулевом разряде. Нулевой сигнал с пятого выхода блока анализа результата блокирует элемент И 16 для прохождения синхроимпульсов на тактовые входы регистров 12-14. Комбинация сигналов на выходах схем 13 8 и II сравнения, поступающая на первый - шестой входы блока 10fвыбирает из блока 10 анализа результата данные согласно строкам 4-12, 16-24, 28-36 табл.1.

По следующему синхронизирующему сигналу осуществляется суммирование этих данных с содержимым накапливающего сумматора 15, в результате которого в младших разрядах сумматора 15 образуется код 00, 01 или 10, в зависимости от содержания информации на выходах схем 7,8 и 11 сравнения и входа и ОР4 , ОР2 режима работы уст10

ройства. Данные коды подключают на выход коммутатора 9 и выход 5 устройства соответственно выходы второго, третьего или первого регистров 13, 14 и 12, т.е. осуществляется передача на выход 5 устройства макс (мин, raid) из чисел А,В,С. Код 00, 01, или 10, поступая на девятый и десятый входы блока 10 анализа результата, выбирает из БА данные, содержащие единицу в нулевом разряде. В результате единичный сигнал с пятого выхода блока анализа результата разблокирует через элемент И 16 ре- 15 гистры 12-}4 для приема новых чисел. Для устранения динамической ошибки работы устройства необходимо, чтобы частота синхронизирующих импульсов была в два раза выше частоты поступ- 20 ления данных на входы 1-3 устройства.

В режимах 2.1 и 2.2 числа, составляющие последовательность, могут поступать на входы 2 и З парами. При поступлении чисел последовательности 25 на вход 2 (или 3) устройства по одному на другой вход 3 (или 2) устройства необходимо подать нулевой код для режима 2.1 или единичный код (11 ... 1) для режима 2.2,30

В данных режимах через коммутатор 18 на вход регистра 12 подключен выход коммутатора 9, В результате такого подключения в регистр 12 осуществляется запись максимального (режим 2,1) или минимального (режим 2.2) числа из сравниваемых трех чисел в предыдущем такте работы устройства. В каждом такте работы устройство функционирует, как в рассмотренных режимах 1.1 и 1.2. После окончания поступления последовательности чисел в устройство на первом выходе 5 находится максимальное (или минимальное) число из рассматриваемой последовательности.

В режиме 3 в исходном состоянии устройства нулевым сигналом с младшего разряда выхода сумматора 15, связанного с десятым входом блока 10 анализа результата, выбирают из блока 10 анализа результата данные, содержащие единицу в первом разряде. Единичным сигналом с четвертого выхода блока 10 анализа результата элемент И 17 разблокирован. Первый вход 1 устройства подключен через коммутатор 18 на вход регистра 12.

1474638Ю

На вход 1 устройства поступает число-эталон, на входы 2 и 3 - первые числа анализируемой последовательности.

По синхронизирующему импульсу с входа 19 устройства осуществляется прием чисел А,В,С в регистры 13, 14 и 12 устройства. По этому же импульсу происходит суммирование в накапливающем сумматоре 15 его исходного содержания (нулевого) с данными, снимаемыми с выхода блока 10 анализа результата (строка 37 табл.1). В результате на младшем разряде с выхода сумматора 15 появляется единичный сигнал, который, поступая на управляющий вход коммутатора 9, подключает на выход коммутатора 9 выход регистра 12. Этот единичный сигнал, поступая на десятый вход блока 10 анализа результата, выбирает из него данные, содержащие ноль в первом и втором разрядах. Нулевой сигнал с четвертого выхода блока 10 анализа блокирует элемент И 17 для прохождения синхроимпульсов с входа 19 устройства. В накапливающем сумматоре 15 содержится число, имеющее младший разряд, равный единице.

Так как данные, поступающие на сумматор 15 из блока 10 анализа результата, в младшем разряде содержат ноль (строки 38-46 табл.1), то состояние младшего выхода сумматора 15 не изменяется, т.е. остается единичным. Следовательно, не изменяется и единичное состояние десятого входа блока 10 анализа результата и соответствующего разряда управляющего входа коммутатора 9. Таким образом, нулевой сигнал с четвертого выхода блока 10 анализа результата, выбираемый из него при единичном состоянии десятого входа, постоянно блокирует элемент И 17, фиксируя тем самым число-эталон в регистре 12 на время просмотра всей последовательности. Кроме того, единичным сигналом с младшего разряда выхода сумматора 15 коммутатор 9 настроен на подключение на выход регистра 12. В результате такого подключения число- эталон постоянно подается на вторые входы первой и третьей схем 7 и I сравнения.

В зависимости от комбинации сигналов на выходах первой и третьей схем 7 и 11 сравнения на первом и

35

40

45

50

55

втором выходах блока 10 анализа результата формируется код количества совпадений двух чисел, поступающих на второй и третий входы 2 и 3 уст- ройства, с числом-эталоном, хранимым в регистре 12. По синхронизирующему импульсу с выхода 19 устройства осуществляется суммирование этого кода с содержимым накапливающего суммато- pa 15, а также прием очередных чисел .последовательности в регистры 13 и 14.

В данном режиме частота поступления чисел на входы 2 и 3 устройства должна совпадать с частотой синхроимпульсов, формирование информации о количестве совпадений с эталоном чисел анализируемой последовательности из 2п чисел (при поступлении чисел на входы устройства парами) осуществляет с запаздыванием на один такт относительно поступления на входы 2,3 устройства (2п-1)- и 2п-го чисел После просмотра всей последователь- ности на втором выходе 6 устройства находится информация о количестве совпадений чисел этой последовательности с эталоном.

Предлагаемое устройство за счет лишь изменения содержания блока IО анализа результата позволяет решать широкий круг задачt связанных со сравнением между собой данных при числовой или символьной обработке. Например, при обработке символьной информации с целью контроля подсчитывают количество открывающих и закрывающих скобок,, Если эту функцию записать рекурсивно, то предложенное уст- ройство будет ее реализовать. Так, в регистры 13 и 14 устройства нужно занести коды соответственно открывающей и закрывающей скобок, а коды символов подавать на вход 1 устрой- ства. При соответствующей организации блока 10 анализа результата устройство будет реализовывать и указанную функцию,

Формула изобретения

Устройство для обработки информации, содержащее первую и вторую схех мы сравнения, первый коммутатор, блок анализа результата, причем входы первых групп первой и второй схем сравнения соответственно объединены, первый и второй выходы первой схемы

, O

5 0 5

0 0 5

0

5

сравнения соединены соответственно с первым и вторым входами блока анализа результата, первый и второй выходы второй схемы сравнения со.ецине- ны соответственно с третьим и четвертым входами блока анализа результата, выходы первого коммутатора являются информационными выходами устройства, отличаю-щееся тем, что, с целью расширения функциональных возможностей за счет дополнительного нахождения экстремума последовательности чисел и осуществления подсчета количества совпадений чисел последовательности с заданным числом-эталоном, в устройство введены третья схема сравнения, три регистра, накапливающий сумматор, второй коммутатор, два элемента И, причем вход синхронизации устройства соединен с первым входом первого элемента И и с синхро- входом накапливающего сумматора, первый, второй и третий входы которого соединены с первым, вторым и третьим выходами блока анализа результата, а выходы разрядов накапливающего сумматора, кроме младшего, являются выходами числа совпадений устройства, пятый и шестой входы блока анализа результата соединены соответственно с первым и вторым выходами третьей схемы сравнения, седьмой и восьмой входы блока анализа результата являются соответственно первым и вторым разрядами входа установки режима устройства, третий разряд входа установки режима устройства соединен с управляющим входом второго коммутатора, девятый и десятый входы блока анализа результата соединены соответственно с двумя младшими разрядами выхода накапливающего сумматора и с входами управления первого коммутатора, чет- вертый выход блока анализа результата соединен с первым входом второго элемента И, выход которого соединен с синхровходом первого регистра, пятый

выход блока анализа результата соединен с вторым входом первого элемен- i та И, выход которого соединен с вто-.

рым входом второго элемента И и син- хровходами второго и третьего регистров, входы первого анализируемого числа устройства соединены с первой группой входов второго коммутатора, информационные входы второго и третьего регистров являются соотзет13147463814

ственно входами второго и третьего ния, третья группа входов первого анализируемых чисел устройства, ин- коммутатора соединена с выходами раз- формационные входы первого регистра рядов третьего регистра, с второй

соединены с выходами второго комму-5 группой входов второй схемы сравнения татора, а выходы разрядов соединены и первой группой входов третьей схе- с первой группой входов первого ком- мы сравнения, выходы первого коммута- мутатора, вторая группа входов ко- тора соединены с вторыми группами торого соединена с выходами разрядов входов первой и третьей схем сравневторого регистра и первыми группамию ния и с второй группой входов второ- входов первой и второй схем аравне- го коммутатора.

| Устройство для сравнения чисел | 1984 |

|

SU1236461A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки цифровой информации | 1977 |

|

SU736094A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-14—Подача