Изобретение относится к запоминающим устройствам и может быть использовано для.передачи данных в устройствах .автоматики и вычислительной техники с си1гхронной произвольно последовательной выборкой.

Цель изобретения - повышение быстродействия устройства.

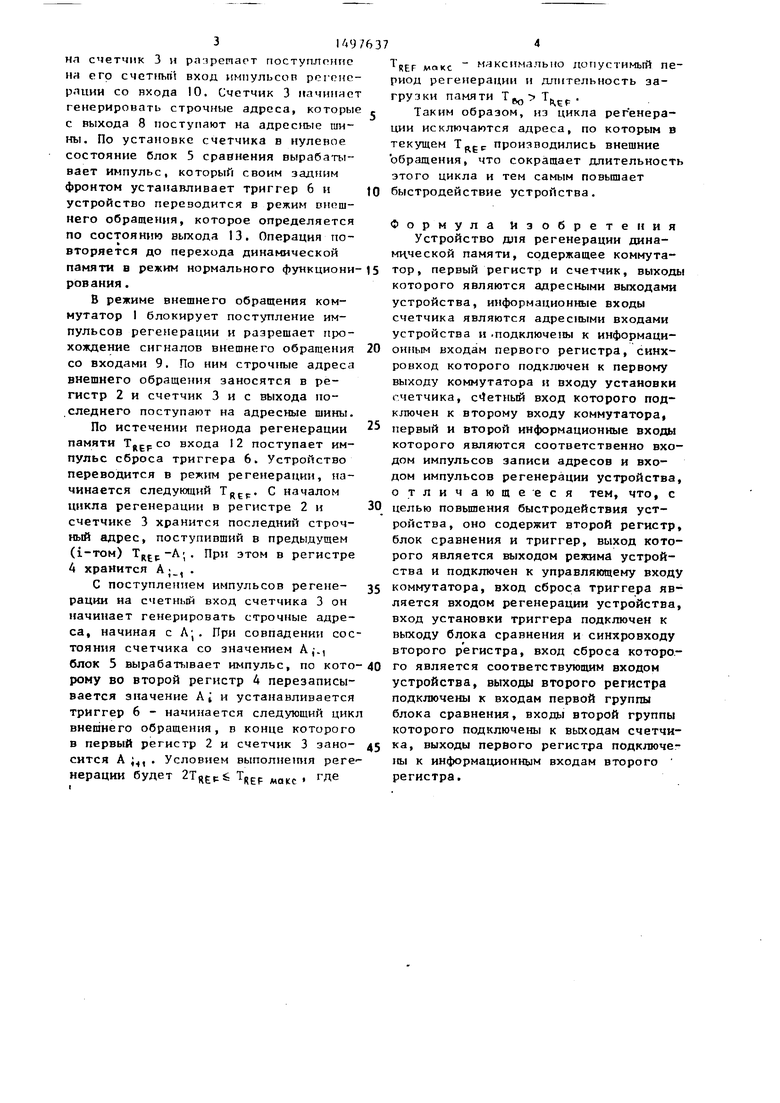

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит коммутатор 1, первьй регистр 2, счетчик 3, второй регистр 4, блок 5 сравнения, триггер 6 адресные входы 7 и выходы 8, вход 9 импульсов записи адресов, вход 10 импульсов регенерации, вход 11 сброса, вход 12 регенерации и выход 13. режима.

По входу 7 поступают строчные адреса внешних обращений, по входу 9 - их стробы.

Устройство работает следующим образом.

После подачи питаюп1его напряжения регистры и счетчик устанавливаются произвольно, а для перевода динамической памяти в нормальный режим функционирования иеобходимо произвести несколько циклов регенерации. Для зтого по входу II на регистр 4 и по входу 12 на триггер 6 подаются импульсы сброса. Устройство переводится в режим регенеряпии. По нулевому I состоянию триггера 6 коммутатор I блокирует подачу сигналов установки

;о

Од

00

3149

нл счетчик 3 и ра-лретагт поступление ня его c4CTi(bii i вход импульсов рсгонс- рлции со входа 10. Счетчик 3 начипнст генерировать строчные адреса, которые с выхода 8 поступают на адресные шины. По установке счетчика в нулевое состояние блок 5 сравнения вырабатывает импульс, который своим задним фронтом устанавливает триггер 6 и устройство переводится в режим внешнего обращения, которое определяется по состоянию выхода 13. Операция повторяется до перехода динамической памяти в режим нормального функционирования.

В режиме внешнего обращения коммутатор I блокирует поступление импульсов регенерации и разрешает прю- хождение сигналов внешнего обращения со входами 9. По ним строчные адреса внешнего обращения заносятся в регистр 2 и счетчик 3 и с выхода последнего поступают на адресные шины.

По истечении периода регенерации памяти Tjgp со входа 12 поступает импульс сброса триггера 6. Устройство переводится в режим регенерации, начинается следующий Tgjp. С началом цикла регенерации в регистре 2 и счетчике 3 хранится последний строчный адрес, поступивший в предыдущем (i-том) . При этом в регистре А хранится А;, .

С поступлением импульсов регене- рации на счетный вход счетчика 3 он начинает генерировать строчные адреса, начиная с Л;. При совпадении состояния счетчика со значением А,-., блок 5 вырабатывает импульс, по кото рому во второй регистр 4 перезаписывается значение Ai и устанавливается триггер 6 - начинается следующий цик внешнего обращения, в конце которого в первый регистр 2 и счетчик 3 зано- сится А ;, . Условием выполне1шя регенерации будет макс f

TREF voKc максимально допустимый период регенерации и длительность загрузки памяти .

Таким образом, из цикла регенерации исключаются адреса, по которым в текущем производились внешние обращения, что сокращает длительность этого цикла и тем самым повьщ1ает быстродействие устройства.

Формула Изобретения

Устройство для регенерации дина- мнческой памяти, содержащее коммутатор, первый регистр и счетчик, выходы которого являются адресными выходами устройства, информационные входы счетчика являются адресными входами устройства и -подключены к информационным входам первого регистра, синх- ровход которого подключен к первому выходу коммутатора и входу установки счетчика, с етный вход которого подключен к второму входу коммутатора, первый и второй информационные входы которого являются соответственно входом импульсов записи адресов и входом импульсов регенерации устройства, отличающееся тем, что, с целью повьш1еиия быстродействия устройства, оно содержит второй регистр, блок сравнения и триггер, выход которого является выходом режима устройства и подключен к управляющему входу коммутатора, вход сброса триггера является входом регенерации устройства, вход установки триггера подключен к выходу блока сравнения и синхровходу второго регистра, вход сброса которого является соответствующим входом устройства, выходы второго регистра подключены к входам первой группы блока сравнения, входы второй группы которого подключены к выходам счетчика, выходы первого регистра подключены к информационным входам второго регистра.

cs I vj,

«o

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для распределения и регенерации динамической памяти | 1989 |

|

SU1735857A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1608752A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1987 |

|

SU1462425A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Устройство для управления регенерацией динамической памяти | 1987 |

|

SU1474744A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

Изобретение относится к динамическим запоминающим устройствам и может быть использовано для передачи данных в устройствах автоматики и вычислительной техники с синхронной произвольно-последовательной выборкой. Цель изобретения - повышение быстродействия. Устройство содержит коммутатор , два регистра, компаратор, триггер, адресные и управляющие входы и выходы. Триггер задает режим работы устройства. В первом регистре запоминается последний строчный адрес внешнего обращения в текущем периоде регенерации, во втором регистре - адрес последнего обращения в предыдущем периоде. Из цикла регенерации исключаются адреса, прорегенерированные в текущем периоде регенерации. 1 ил.

Csl

1У

м X

| Полупроводниковые БИС запоминающих устройств | |||

| Справочник под ред | |||

| А.Ю.Гордонова и Ю.Н.Дьякова | |||

| М.: Радио и связь, 1987, с, 87-90, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР , № 691925, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-07-30—Публикация

1987-11-02—Подача