Изобретение относится к вычислительной технике и может быть использовано при конструировании многопроцессорных систем с программируемой архитектурой.

Цель изобретения - повышение быстродействия устройства.

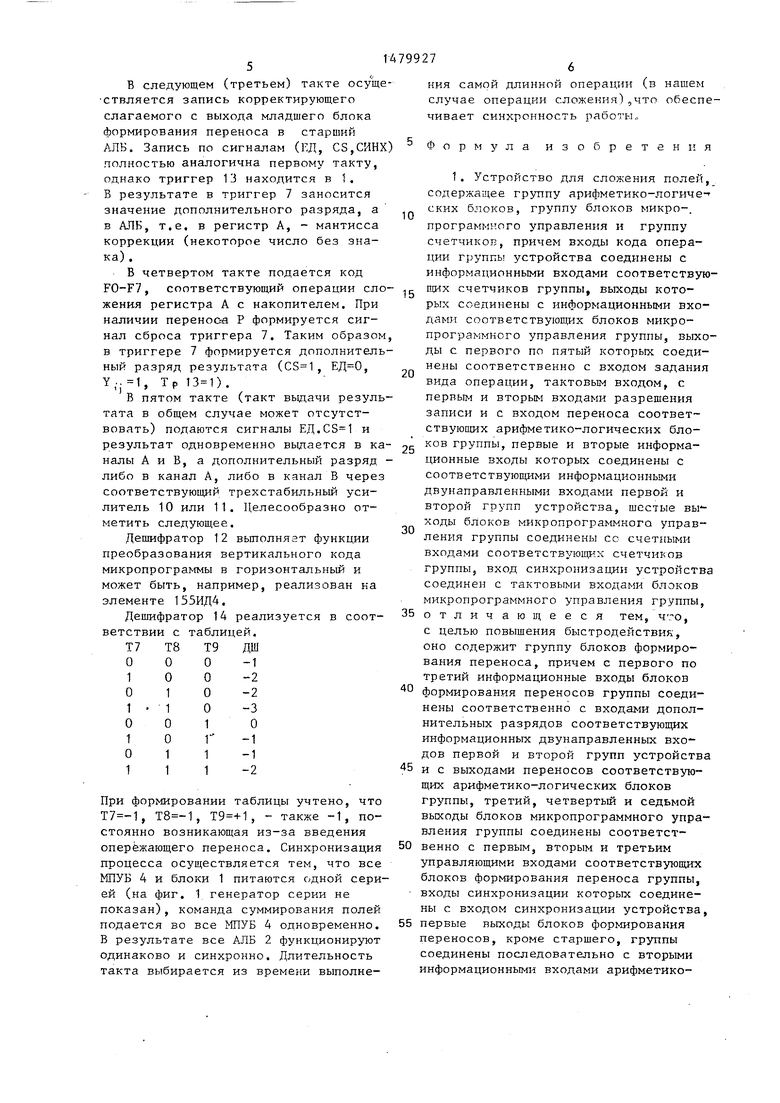

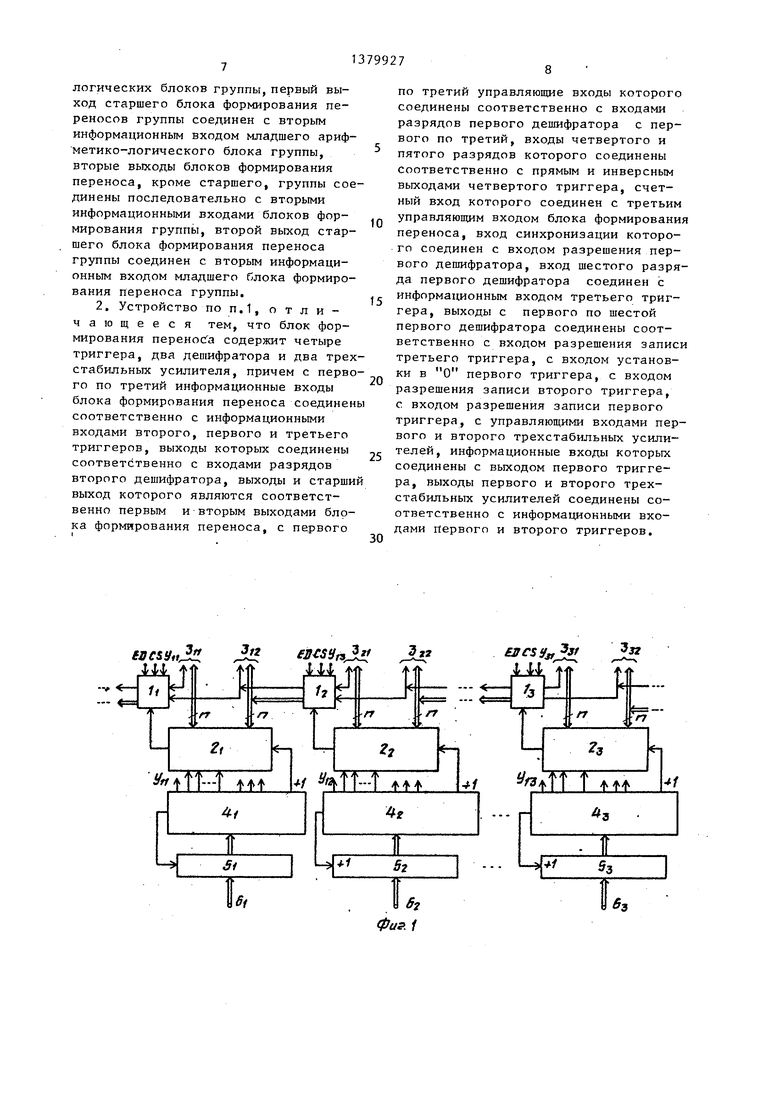

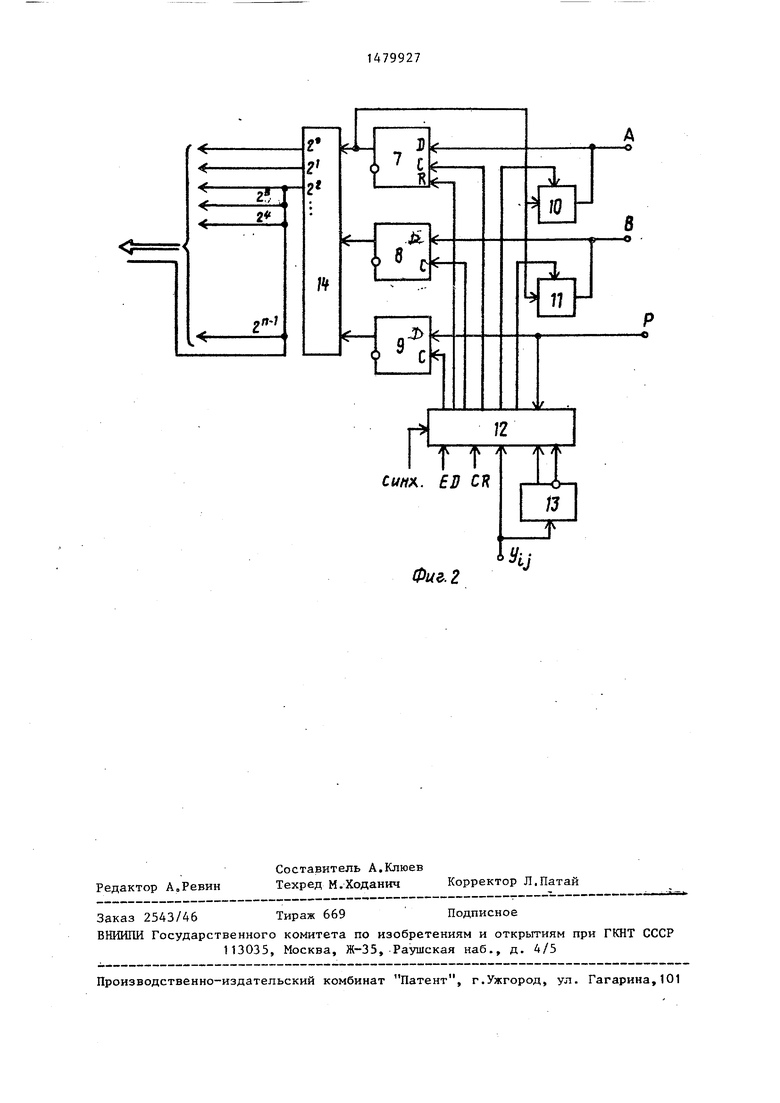

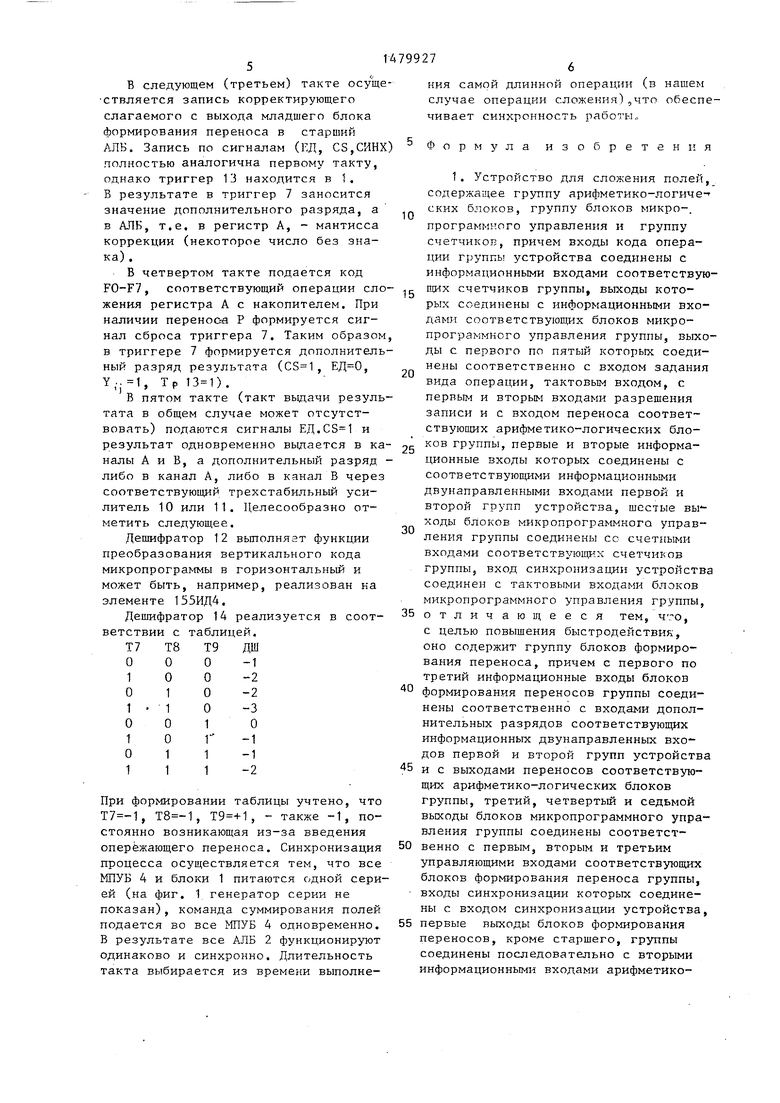

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 - схема блока формирования переноса.

Устройство содержит группу блоков 1. - 1 j формирования переноса, группу арифметико-логических блоков 21- 2,, группу первых информационных двунаправленных входов 3 (1 - 3 31 , группу вторых информационных двунаправленных входов 3 п- Ззг, группу блоков 4 , - 4Ч микропрограммного управления (МПУК), группу счетчиков 5 , - 5 з и группу входов 6., - 65 кода операции.

I2

Блок 1 формирования переноса содержит с первого по третий триггеры 7-9, первый 10 и второй 11 трех- стабильные усилители, первый дешифратор 12, четвертый триггер 13 и второй дешифратор 14.

В устройстве используется код опережающий перенос. Его идея заключается в следующем. Поле разбивается на группы разрядов. Каждая группа включает столько разрядов поля, сколько разрядов включает арифметико-логический блок (АЛБ). В этом случае, если m - число разрядов поля, п - разрядность АЛБ, то N

I , где - - целое с избытком. При этом одинаковая команда сложения поступает в N блоков микропрограммного управления (МПУБ), соотЛ«vl СО СО N3 4

ветствующих АЛБ. Каждый из МПУБ вырабатывает код сложения и одновременно формирует +1, поступающую на вход переноса (опережающий перенос). Для того, чтобы результат суммирования не изменился, в младшей группе вводится добавочный разряд, куда записывается -1 (1). Вес этой единицы равен весу младшего разряда старшей группы или 2° относительно младшей группы. При этом, если в младшей группе из значащих разрядов возникает перенос (+2°), то дополнительный разряд обнуляется (-2°+2° 0), в противном случае 1 в дополнительном разряде сохраняется. Так как при суммировании групп могут встретиться слагаемые, у которых в дополнительных разрядах стоят две единицы (ТО) и плюс 1 от организации опережающего переноса, то в общем случае после сложения будем иметь перенос, равный (11 -3). Ьсли не принять дополнительных мер, то перенос может неограниченно возрастать. Введем дополнительный такт суммирования, в котором к результату старшей группы прибавляется перенос из младшей группы. При суммировании переносов все дополнительные разряды равны нулю (перенос пошел в старшую группу) и переносы (С1) на выходе МПУБ тоже равны нулю. При этом перенос в старшую группу может принимать следующие значения: 0,-1,-2,-3 - десятичное кодирование или 00, 01,10,11 - двоичное кодирование. Нетрудно видеть, что действительной операцией будет операция вычитания. Для того, чтобы фактически выполнить операцию сложения, запишем перенос в дополнительном коде. Тогда, например, для 11

,111 ...101, перенос в ближайшую группу разрядов

будет иметь J. 111 ... 11, дополнения до полного поля

Поясним это на примере. Пусть поле содержит 16 разрядов

.

тт. 1

щт

2

кмк з

5шж

4

Формат

АЛБ - 4 разряда. Перенос возник в третьей группе. Тогда, чтобы вычесть, нужно размножить знак на оставшиеся разряды, включая знаковый. Итак,

0

5

0

5

0

5

0

5

0

5

°- 1. 1111 1101 дополне- перенос ние до во 2-ю полного группу поля из 3-й

Аналогично, для 10 и 1. Ясно, что дополнение до полного поля можно заменить переносом в младший -разряд следующей группы и 1 в дополнительном разряде ближайшей группы, тогда 11 будет иметь вид

J3.000. .. 00 .1.111. ..101, дополнение доп. перенос в до полного раз- ближайшую поляряд группу

Другими словами, с учетом дополнительного разряда перенос оперирует только с разрядами ближайшей группы. При атом, учитывая, что значение дополнительного разряда в самой группе равно нулю, после суммирования этот разряд будет равен либо Т, если перенос СО равен 0, либо 0, если . Поэтому после второго такта суммирования в дополнительных разрядах результата возможно появление только одной 1. Так как единицы в дополнительных разрядах могут принимать только отрицательные значения, то знак можно не хранить, а хранить только модуль числа.

Устройство работает следующим образом,

Первый аргумент поступает на вход А арифметико-логических блоков 2, а дополнительный разряд - на вход А блока 1 формирования переносов. Аналогично, для второго операнда, который поступает на вход В. Оба операнда поступают одновременно. По сигналам разрешения записи (ЕД,) и синхросерии дополнительные разряды записываются в триггеры 7 и 8, а по сигналам ЕД. и тактовому (CLS) операнды записываются в арифметико- логические блоки0 На этом первый такт раСготы завершается. Во втором такте на выходах задания вида операции (FO-F7) МПУБ 4 формируется код сложения (, ЕД 0, Yif1, Tp13 0). Происходит суммирование операндов . Результат записывается в регистр расширения АЛБ (по заднему фронту сигнала),а перенос с выхода СО АЛБ- в триггер У блока формирования переноса (по заднему фронту сигнала Y;J),

В следующем (третьем) такте осуществляется запись корректирующего слагаемого с выхода младшего блока формирования переноса в старший АЛБ. Запись по сигналам (ЕД, СЗ,СЙНХ) полностью аналогична первому такту, однако триггер 13 находится в 1. В результате в триггер 7 заносится значение дополнительного разряда, а в АПК, т.е. в регистр А, - мантисса коррекции (некоторое число без знака) .

В четвертом такте подается код FO-F7, соответствующий операции сложения регистра А с накопителем. При наличии переноса Р формируется сигнал сброса триггера 7. Таким образом, в триггере 7 формируется дополнительный разряд результата (, , Y,., Tp ).

В пятом такте (такт выдачи результата в общем случае может отсутствовать) подаются сигналы ЕД. и результат одновременно выдается в каналы А и В, а дополнительный разряд - либо в канал А, либо в канал В через соответствующий трехстабильный усилитель 10 или 11. Целесообразно отметить следующее.

Дешифратор 12 выполняет функции преобразования вертикального кода микропрограммы в горизонтальный и может быть, например, реализован на элементе 155ИД4.

Дешифратор 14 реализуется в соответствии с таблицей.

При формировании таблицы учтено, что , , , - также -1, постоянно возникающая из-за введения опережающего переноса. Синхронизация процесса осуществляется тем, что все МПУБ 4 и блоки 1 питаются одной серией (на фиг. 1 генератор серии не показан), команда суммирования полей подается во все МПУБ 4 одновременно. В результате все АЛБ 2 функционируют одинаково и синхронно. Длительность такта выбирается из времени выполне

5

0

5

0

5

ния самой длинной операции (в нашем случае операции сложения),что обеспечивает синхронность работы.,

Формула изобретения

1. Устройство для сложения полей, содержащее группу арифметико-логиче- ских блоков, группу блоков микро-, программного управления и группу счетчиков, причем входы кода операции группы устройства соединены с информационными входами соответствующих счетчиков группы, выходы которых соединены с информационными входами соответствующих блоков микропрограммного управления группы, выходы с первого по пятый которых соединены соответственно с входом задания вида операции, тактовым входом, с первым и вторым входами разрешения записи и с входом переноса соответствующих арифметико-логических блоков группы, первые и вторые информационные входы которых соединены с соответствующими информационными двунаправленными входами первой и второй групп устройства, шестые вы - ходы блоков микропрограммного управления группы соединены ее счетными входами соответствующих счетчиков группы, вход синхронизации устройства соединен с тактовыми входами блоков микропрограммного управления группы,

5

0

5

с целью повышения быстродействия, оно содержит группу блоков формирования переноса, причем с первого по третий информационные входы блоков 0 формирования переносов группы соединены соответственно с входами дополнительных разрядов соответствующих информационных двунаправленных входов первой и второй групп устройства и с выходами переносов соответствующих арифметико-логических блоков группы, третий, четвертый и седьмой выходы блоков микропрограммного управления группы соединены соответственно с первым, вторым и третьим управляющими входами соответствующих блоков формирования переноса группы, входы синхронизации которых соединены с входом синхронизации устройства, первые выходы блоков формирования переносов, кроме старшего, группы соединены последовательно с вторыми информационными входами арифметике

логических блоков группы,первый выход старшего блока формирования переносов группы соединен с вторым информационным входом младшего арифметико-логического блока группы, вторые выходы блоков формирования переноса, кроме старшего, группы соединены последовательно с вторыми информационными входами блоков формирования группы, второй выход старшего блока формирования переноса группы соединен с вторым информационным входом младшего блока формирования переноса группы.

2. Устройство по п.1, о т л и - чающееся тем, что блок формирования переносГа содержит четыре триггера, два дешифратора и два трех стабильных усилителя, причем с первого по третий информационные входы блока формирования переноса соединен соответственно с информационными входами второго, первого и третьего триггеров, выходы которых соединены соответственно с входами разрядов второго дешифратора, выходы и старши выход которого являются соответственно первым и вторым выходами блока формирования переноса, с первого

0

5

0

0

по третий управляющие входы которого соединены соответственно с входами разрядов первого дешифратора с первого по третий, входы четвертого и пятого разрядов которого соединены соответственно с прямым и инверсным выходами четвертого триггера, счетный вход которого соединен с третьим управляющим входом блока формирования переноса, вход синхронизации которого соединен с входом разрешения первого дешифратора, вход шестого разряда первого дешифратора соединен с информационным входом третьего триггера, выходы с первого по шестой первого дешифратора соединены соответственно с входом разрешения записи третьего триггера, с входом установки в О первого триггера, с входом разрешения записи второго триггера, с входом разрешения записи первого триггера, с управляющими входами первого и второго трехстабильных усилителей, информационные входы которых соединены с выходом первого триггера, выходы первого и второго трехстабильных усилителей соединены соответственно с информационными входами Первого и второго триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Вычислительное п-разрядное устройство | 1977 |

|

SU686028A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Операционное устройство процессора | 1979 |

|

SU809189A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Арифметико-логическая секция | 1987 |

|

SU1499333A1 |

Изобретение относится к области вычислительной техники и может быть использовано при реализации в многопроцессорных системах операции сложения данных с произвольным форматом путем объединения арифметико-логических блоков различных процессоров без организации последовательности переноса. Целью изобретения является повышение быстродействия. Эта цель достигается путем введения в устройство для сложения полей, содержащее группу арифметико-логических блоков, группу блоков микропрограммного управления, группу счетчиков, группы блоков формирования переноса с соответствующими связями. 1 з.п. ф-лы, 2 ил.

ac&y,,3z 3Ј ая9пЛ JU

ис5у„ я JЈ u

Т

Фие.2

Ч

| Устройство для суммирования | 1985 |

|

SU1295385A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Берзенко А.И | |||

| и др | |||

| Микропроцессорные комплекты повышенного быстродействия | |||

| М.: Радио и связь, 1981, с | |||

| Топочная решетка для многозольного топлива | 1923 |

|

SU133A1 |

Авторы

Даты

1989-05-15—Публикация

1987-07-20—Подача