Изобретение относится к вычислительной технике и может быть использовано при построении устройств отображения и обработки изображений.

Цель изобретения - упрощение и повышение надежности устройства.

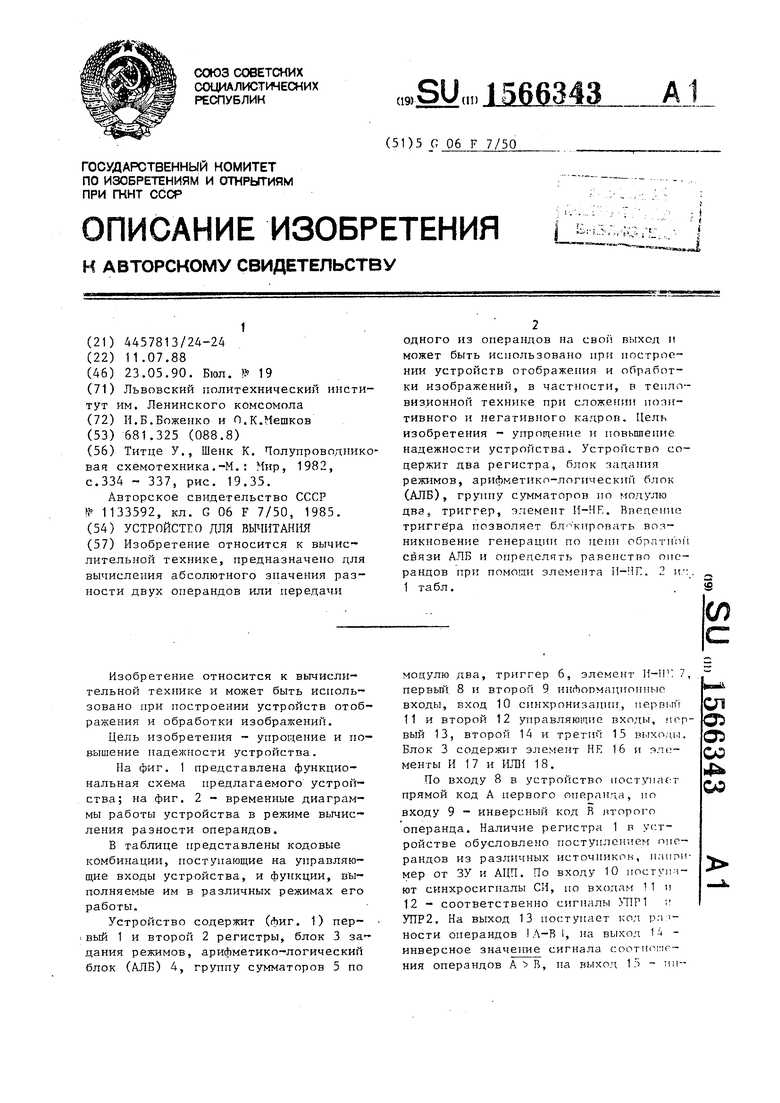

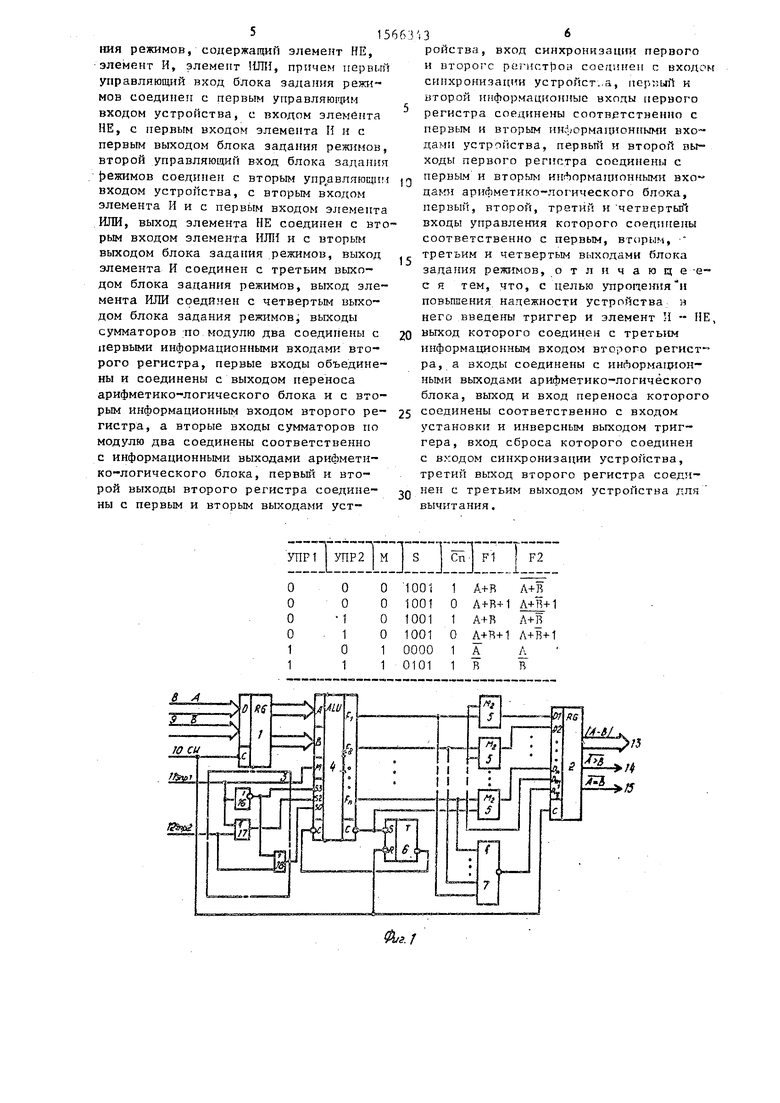

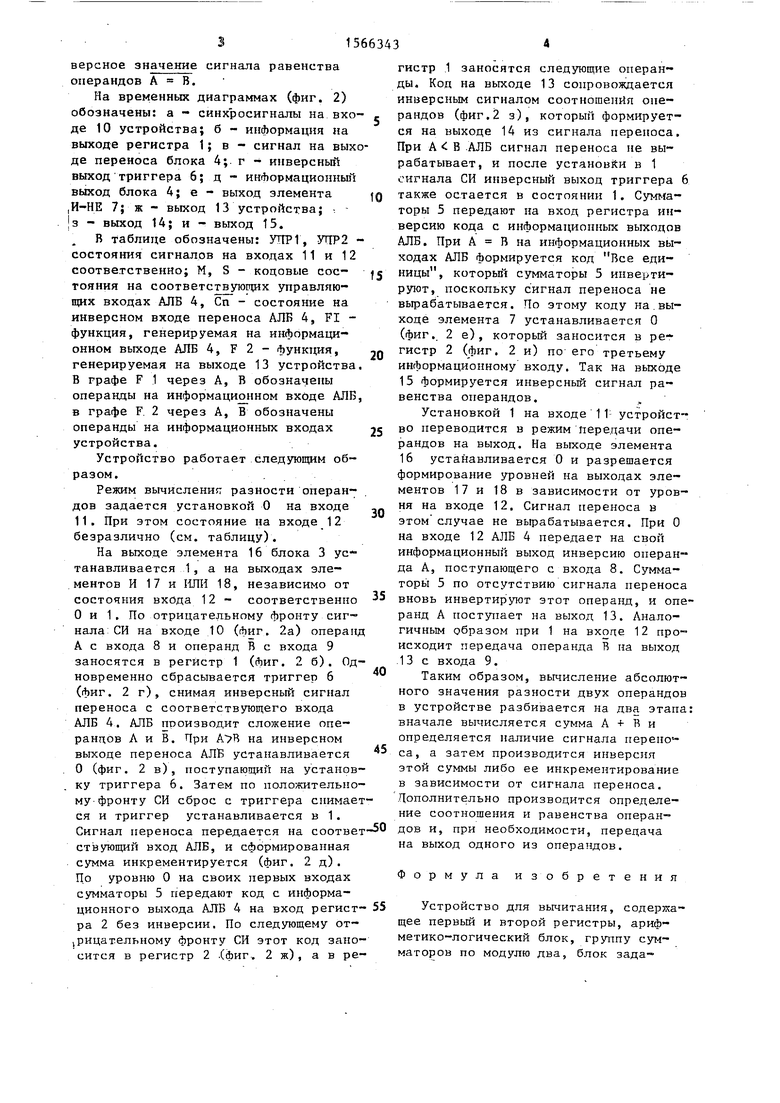

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства в режиме вычисления разности операндов.

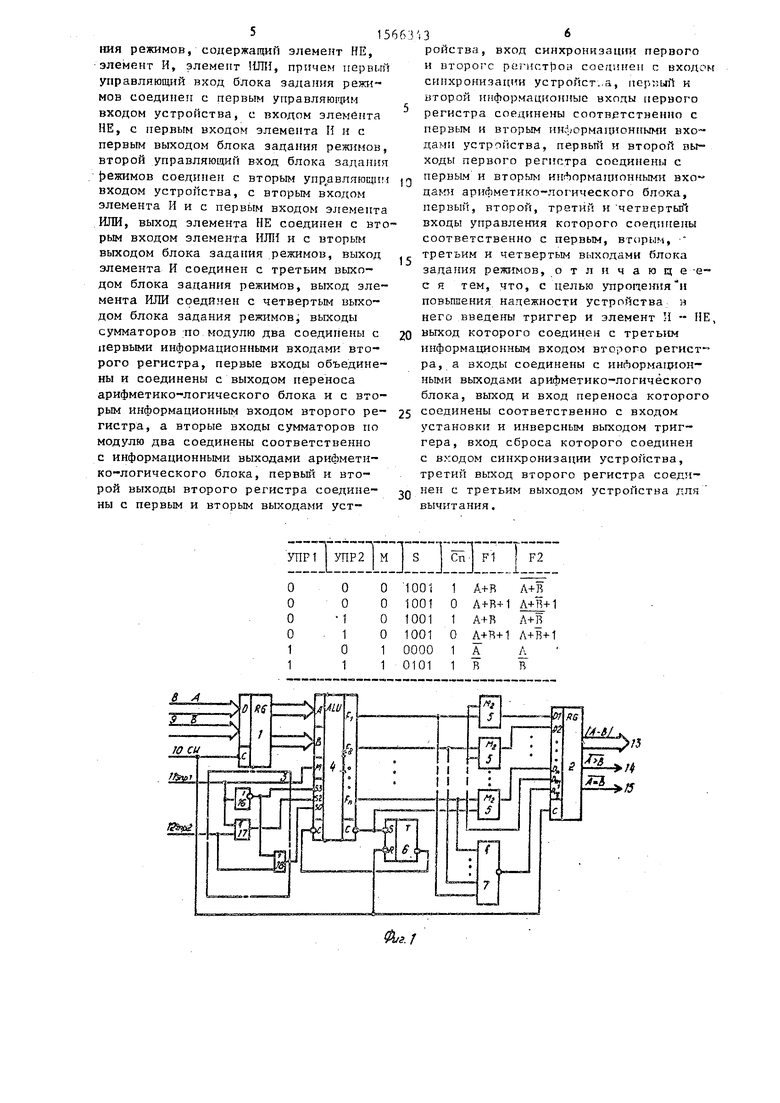

В таблице представлены кодовые комбинации, поступающие на управляющие входы устройства, и функции, выполняемые им в различных режимах его работы.

Устройство содержит (Лиг. 1) первый 1 и второй 2 регистры, блок 3 за™ дания режимов, арифметико-логический блок (АЛБ) 4, группу сумматоров 5 по

15выхо u i.

16II Т. Н модулю два, триггер 6, элемент H-II1 . /, первый 8 и второй 9 ннЛопмационпне входы, вход 10 синхронизации, нерпы

11и второй 12 управляющие входы, первый 13, второй 14 и третий

Блок 3 содержит элемент ПК менгы И 17 и ИЛИ 18.

По входу 8 в устройство IIOCTVINH г прямой код А первого операнда, по входу 9 - инверсный код В второго операнда. Наличие регистра 1 в устройстве обусловлено поступлением операндов из различных источником, п.,п,ч мер от ЗУ и АЦП. По входу 10 nocrvri- ют синхросигналы СИ, по входам 11 и

12- соответственно сигналы TIP1 ; УПР2. На выход 13 поступает код р, - ности операндов I Л-В , на выход 1 - инверсное значение сигнала сротчоп- ния операндов А В, на выхо i 1 - пел

о оэ со

4

СО

версное значение сигнала равенства операндов А В.

На временных диаграммах (фиг. 2) обозначены: а - синхросигналы на вхо- де 10 устройства; б - информация на выходе регистра 1; в - сигнал на выходе переноса блока 4; г - инверсный выход триггера 6; д - информационный выход блока 4; е - выход элемента ,И-НЕ 7; ж - выход 13 устройства; з - выход 14; и - выход 15.

В таблице обозначены: УПР1, УТР2 - состояния сигналов на входах 11 и 12 соответственно; М, S - кодовые сое- тояния на соответствующих управляющих входах АЛБ 4, Сп - состояние на инверсном входе переноса АЛБ 4, FI - функция, генерируемая на информационном выходе АЛБ 4, F 2 - функция, генерируемая на выходе 13 устройства. В графе F 1 через А, В обозначены операнды на информационном входе АЛБ, в графе F 2 через А, В обозначены операнды на информационных входах устройства.

Устройство работает следующим образом.

Режим вычисление разности операндов задается установкой 0 на входе 11. При этом состояние на входе 12 безразлично (см. таблицу).

На выходе элемента 16 блока 3 устанавливается 1, а на выходах элементов И 17 и ИЛИ 18, независимо от состояния входа 12 - соответственно О и 1. По отрицательному Фронту сигнала СИ на входе 10 (Фиг. 2а) операнд А с входа 8 и операнд В с входа 9 заносятся в регистр 1 (Лиг. 2 б). Одновременно сбрасывается триггеп 6 (Лиг. 2 г), снимая инверсный сигнал переноса с соответствующего входа АЛБ 4. АЛБ ПРОИЗВОДИТ сложение операндов А и В. При на инверсном выходе переноса АЛБ устанавливается О (фиг. 2 в), поступающий на установку триггера 6. Затем по положительному фронту СИ сброс с триггера снимает ся и триггер устанавливается в 1. Сигнал переноса передается на соответ ствующий вход АЛБ, и сформированная сумма инкрементируется (фиг. 2 д). По уровню 0 на своих первых входах сумматоры 5 передают код с информационного выхода АЛБ 4 на вход регист- ра 2 без инверсии. По следующему отрицательному фронту СИ этот код заносится в регистр 2 (Лиг. 2 ж), а в ре

0

5

0

Q

j

55

5

0

45

50

гистр 1 заносятся следующие операнды. Код на выходе 13 сопровождается инверсным сигналом соотношения операндов (фиг.2 з), который формируется на выходе 14 из сигнала переноса. При АЛБ сигнал переноса не вырабатывает, и после установки в 1 сигнала СИ инверсный выход триггера 6 также остается в состоянии 1. Сумматоры 5 передают на вход регистра инверсию кода с информационных выходов АЛБ. При А В на информационных выходах АЛБ формируется код Все единицы, который сумматоры 5 инвертируют, поскольку сигнал переноса не вырабатывается. По этому коду на выходе элемента 7 устанавливается О (фиг. 2 е), который заносится в регистр 2 (фиг. 2 и) по его третьему информационному входу. Так на выходе

15формируется инверсный сигнал равенства операндов.

Установкой 1 на входе 11 устройство переводится в режим передачи операндов на выход. На выходе элемента

16устанавливается 0 и разрешается формирование уровней на выходах элементов 17 и 18 в зависимости от уровня на входе 12. Сигнал переноса в этом случае не вырабатывается. При О на входе 12 АЛБ 4 передает на свой информационный выход инверсию операнда А, поступающего с входа 8. Сумматоры 5 по отсутствию сигнала переноса вновь инвертируют этот операнд, и операнд А поступает на выход 13. Аналогичным образом при 1 на вхоце 12 происходит передача операнда R на выход

13 с входа 9.

Таким образом, вычисление абсолютного значения разности двух операндов в устройстве разбивается на два этапа: вначале вычисляется сумма А + R и определяется наличие сигнала переноса, а затем производится инверсия этой суммы либо ее инкрементирование в зависимости от сигнала переноса. Цополнительно производится определение соотношения и равенства операндов и, при необходимости, передача на выход одного из операндов.

Формула изобретения

Устройство для вычитания, содержащее первый и второй регистры, арифметико-логический блок, группу сумматоров по модулю два, блок зада-

515

ния режимов, содержащий элемент НЕ, элемент И, элемент 1ШИ, причем первый управляющий вход блока задания режимов соединен с первым управляюг(нм входом устройства, с входом элемента НЕ, с первым входом элемента И и с первым выходом блока задания режимом, второй управляющий вход блока задания режимов соединен с вторым управляющим входом устройства, с вторым «ходом элемента И и с первым входом элемента ИЛИ, выход элемента НЕ соединен с вторым входом элемента ИЛИ и с вторым выходом блока задания режимов, выход элемента И соединен с третьим выходом блока задания режимов, выход элемента ИЛИ соединен с четвертым выходом блока задания режимов, выходы сумматоров по модулю два соединены с первыми информационными входами второго регистра, первые входы объединены и соединены с выходом переноса арифметико-логического блока и с вторым информационным входом второго ре- гистра, а вторые входы сумматоров по модулю два соединены соответственно с информационными выходами арифметико-логического блока, первый и второй выходы второго регистра соединены с первым и вторым выходами уст

0

5

5

0

0

,3

ройств.ч, вход синхронизации первого

и итирогг perncTpOif соединен с входам синхронизации устройст -ч, перпып и иторой информационные входы первого регистра соединены соответственно с nepatiM и вторым информационными входами устройства, первый и второй выходы первого регистра соединены с первым и вторым информационными вхо- цаг- М арифметико-логического блока, первый, второй, третий и четисртыи входы управления которого соединены соответственно с первым, , третьим и четвертым внходами блока задания режимов, отличающее- с я тем, что, с целью упрощения н повышения надежности устройства н него «ведены триггер и элемент II - НЕ, выход которого соединен с третьим информационным входом второго регистра, а входы соединены с инЛормацнол- ными выходами арифметико-логического блока, выход и вход переноса которого соединены соответственно с входом установки и инверсным выходом триггера, вход сброса которого соединен с вгодом синхронизации устройства, третий выход второго регистра соединен с третьим выходом устройства для вычитания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Устройство для сложения полей | 1987 |

|

SU1479927A1 |

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

| Процессор | 1989 |

|

SU1725224A1 |

| Арифметико-логическая секция | 1987 |

|

SU1499333A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

Изобретение относится к вычислительной технике, предназначено для вычисления абсолютного значения разности двух операндов или передачи одного из операндов на свой выход и может быть использовано при построении устройств отображения и обработки изображений, в частности, в тепловизионной технике при сложении позитивного и негативного кадров. Цель изобретения - упрощение и повышение надежности устройства. Устройство содержит два регистра, блок задания режимов, арифметико-логический блок (АЛБ), группу сумматоров по модулю два, триггер, элемент И-НЕ. Введение триггера позволяет блокировать возникновение генерации по цепи обратной связи АЛБ и определять равенство операндов при помощи элемента И-НЕ. 2 ил., 1 табл.

УПГ1 I УТТР2 |MSГп F1F2

8 А

Фиг. 2

| Тнтце У., Шенк К | |||

| Полупроводниковая схемотехника.-М.: Мир, 1982, с.334 - 337, рис | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Устройство для вычитания | 1983 |

|

SU1133592A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-11—Подача