ел

Os

а

Јь

о

00

Изобретение относится к вычислительной технике и может быть применено в различных типах запоминающих устройств (ОЗУ, ПЗУ. ППЗУ, РПЗУ) для построения устройств дешифрации.

Цель изобретения - повышение быстродействия устройства.

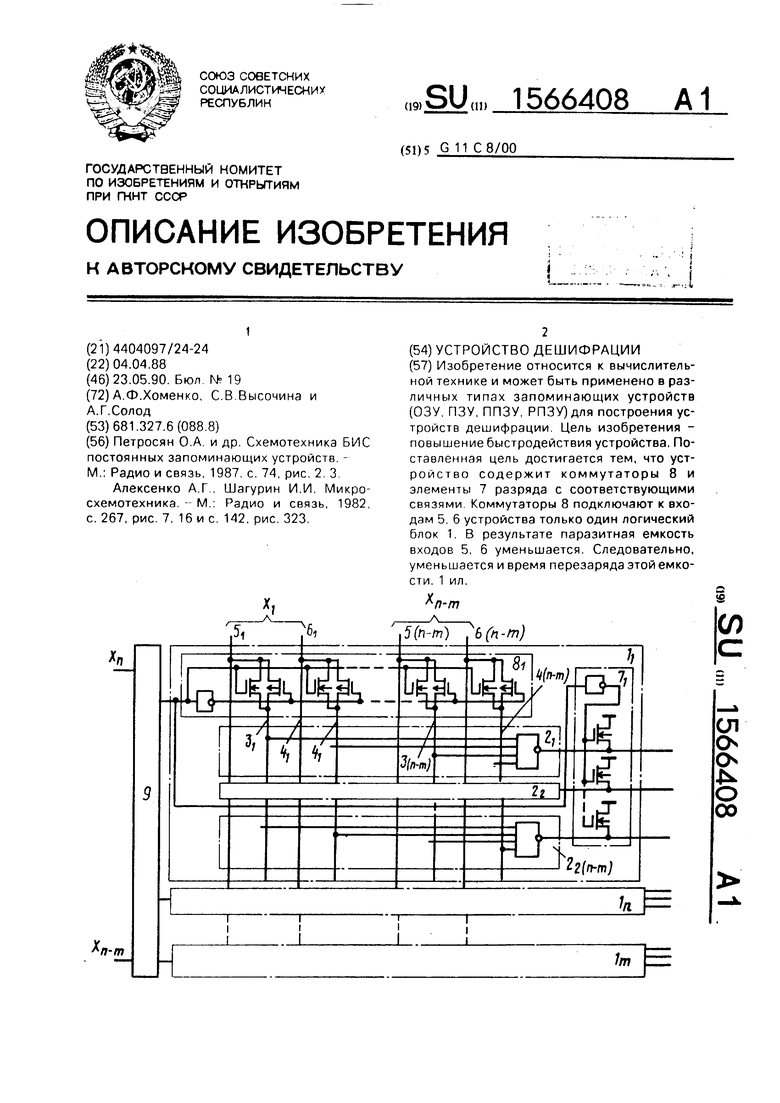

На чертеже представлена блок-схема устройства дешифрации.

Устройство дешифрации содержит ло- гические блоки 1, элементы И 2, прямые 3 и инверсные 4 адресные шины, прямые 5 и инверсные 6 входы второй группы устройства, элементы 7 разряда, коммутаторы 8 и дешифратор 9. При этом коммутаторы 8, элементы И 2, элемент 7, прямые 3 и инверсные 4 адресные шины представляют логический блок 1.

Устройство работает следующим образом.

При подаче адресных сигналов дешифратор 9 старших разрядов обрабатывает их, при этом на одном из выбранных выходов дешифратора 9 старших разрядов появляется высокий потенциал. При этом коммутато- ры 8 осуществляют подключение прямых 3 и инверсных 4 адресных шин к прямым 5 и инверсным 6 входам внутри данного блока 1. Одновременно происходит отключение транзисторов разряда в элементе 7 разряда от выходов устройства в выбранном блоке 1

Выбранная адресная комбинация в виде высоких и низких потенциалов с входов 5 и 6 через блок коммутаторов 8, группу прямых 3 и инверсных 4 шин поступает на входы элементов И 2, и на одном из их выходов появляется высокий потенциал. Очередная смена адресных сигналов вызывает обработку их по изложенному порядку в зависимости от кодовой ситуации адресных сигналов на входе дешифратора 9 и входах 5 и 6.

Формула изобретения Устройство дешифрации, содержащее дешифратор, входы которого являются входами первой группы устройства, логические блоки, каждый из которых состоит из элементов И, выходы которых являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в каждый логический блок введены коммутаторы и элемент разряда, выходы которого соединены с выходами соответствующих элементов И, а вход соединен с входами выборки коммутаторов, выходы которых соединены с соответствующими входами элементов И, соответствующие информационные входы коммутаторов всех логических блоков объединены и являются входами второй группы устройства, а входы элементов разряда соединены с соответствующими выходами дешифратора

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора информации из блоков памяти | 1988 |

|

SU1510011A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Программируемый формирователь управляющих воздействий микропроцессорной системы | 1989 |

|

SU1725210A1 |

Изобретение относится к вычислительной технике и может быть применено в различных типах запоминающих устройств (ОЗУ, ПЗУ, ППЗУ, РПЗУ) для построения устройств дешифрации. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит коммутаторы 8 и элементы 7 разряда с соответствующими связями. Коммутаторы 8 подключают к входам 5, 6 устройства только один логический блок 1. В результате паразитная емкость входов 5,6 уменьшается. Следовательно, уменьшается и время перезаряда этой емкости. 1 ил.

| Петросян О.А и др | |||

| Схемотехника БИС постоянных запоминающих устройств | |||

| - М.: Радио и связь, 1987, с | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микросхемотехника | |||

| - М/ Радио и связь, 1982, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Прибор для наглядного представления свойств кривых 2 порядка (механические подвижные чертежи) | 1921 |

|

SU323A1 |

Авторы

Даты

1990-05-23—Публикация

1988-04-04—Подача