ел

00

о

СЛ

ел

со

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации для декорреляции сигнала помехи.

Целью изобретения является повышение быстродействия устройства.

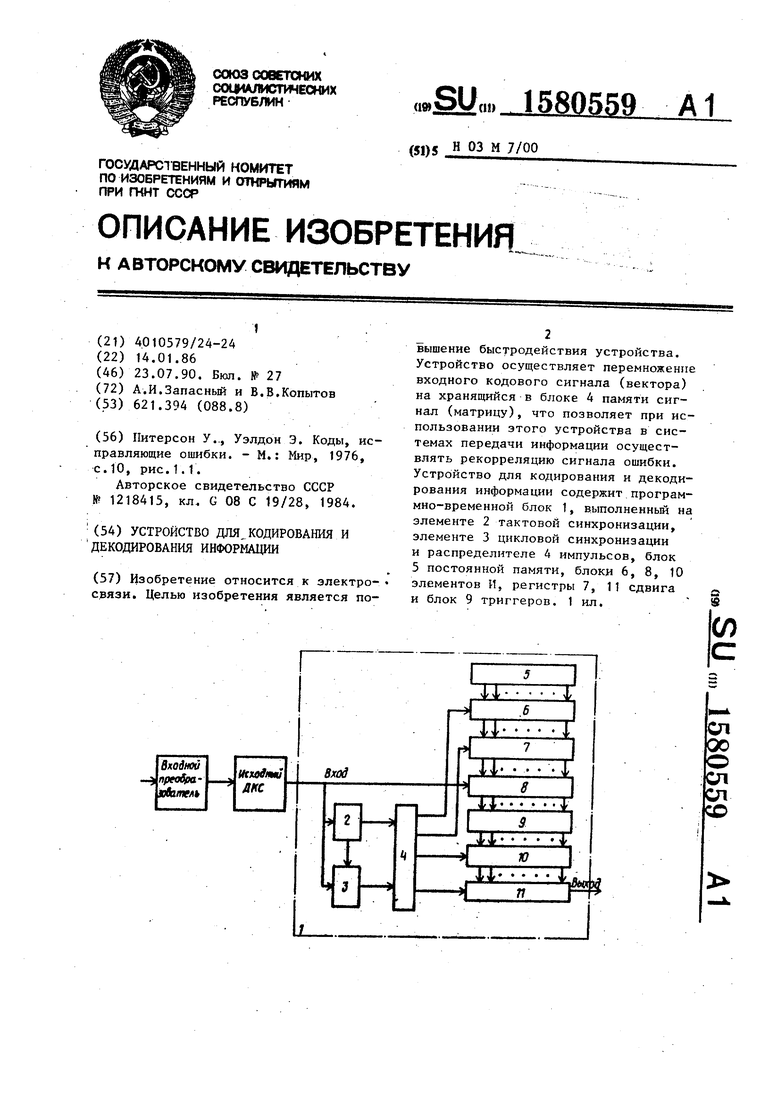

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит программно- временной блок 1, выполненный на элементе 2 тактовой синхронизации, элементе 3 цикловой синхронизации и распределителе 4 импульсов, блок 5 постоянной памяти, второй блок 6 элементов И, первый регистр 7 сдвига, первый блок 8 элементов И, блок 9 триггеров, третий блок 10 элементов И и регистр 11 сдвига.

Устройство работает следующим об- разом.

При поступлении на вход устройства n-разрядного кодового слова по сигналу Начало слова разрешается параллельный перенос кода задающего вектора из блока 5 через блок б в регистр 7. На управляющий вход регистра 7 с задержкой в один такт начинают поступать сдвигающие синхроимпульсу, обеспечивающие на каждом такте сдвиг содержимого регистра 7 на один разряд вправо и параллельную перезапись содержимого регистра 7 через блок 8 в блок 9 только при единичном значении очередного символа кодового слова. В блоке 9 осуществляется по- разрядное суммирование по модулю 2 содержимого регистра 7 и блока 9, т.е. осуществляется перемножение вектора кодового слова на матрицу, строки которой есть последовательные состояния регистра 7 на каждом такте. При поступлении сигнала Конец кодового слова на второй вход блока 10 разрешается параллельная перезапись содержимого блока 9 через блок 10 в

регистр 11, из которого с помощью считывающих синхроимпульсов преобразованный код поступает на выход устройства.

Поскольку преобразование осуществляется в процессе поразрядного поступления кодового слова на вход устройства, то задержка при преобразовании отсутствует, что повышает быстродействие устройства.

Формула изобретения

5 Устройство для кодирования и декодирования информации,содержащее программно-временной блок, вход которого является входом устройства, блок памяти, первьй, второй регистры,

0 выходы первого регистра соединены с соответствующими первыми входами первого блока элементов И, отличающееся тем, что, с целью повышения быстродействия устройства, в

5 него введены второй, третий блоки

элементов И и блок триггеров, выходы блока памяти соединены с соответствующими первыми входами второго блока элементов И, выходы которого соеQ динены с соответствующими информационными входами первого регистра, второй вход первого блока элементов И подключен к входу устройства, выходы первого блока элементов И соединены

5 через блок триггеров с соответствующими первыми входами третьего блока элементов И, выходы которого соединены с соответствующими информационными входами второго регистра, первый Q четвертый выходы программно-временного блока соединены соответственно с вторыми входами второго, третьего блоков элементов И и управляющими входами первого, второго регистров,

5 выход второго регистра является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

Изобретение относится к электросвязи. Цель изобретения является повышение быстродействия устройства. Устройство осуществляет перемножение входного кодового сигнала (вектора) на хранящийся в блоке 4 памяти сигнал (матрицу), что позволяет при использовании этого устройства в системах передачи информации осуществлять рекорреляцию сигнала ошибки. Устройство для кодирования и декодирования информации содержит программно-временный блок 1, выполненный на элементе 2 тактовой синхронизации, элементе 3 цикловой синхронизации и распределителе 4 импульсов, блок 5 постоянной памяти, блоки 6, 8, 10 элементов И, регистры 7, 11 сдвига и блок 9 триггеров. 1 ил.

| Иитерсон У., Уэлдон Э | |||

| Коды, исправляющие ошибки | |||

| - М.: Мир, 1976, с.10, рис.1.1 | |||

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

Авторы

Даты

1990-07-23—Публикация

1986-01-14—Подача