Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, реализуе гм на базовых матричных кристаллах.

Цель изобретения - повышение надежности элемента памяти.

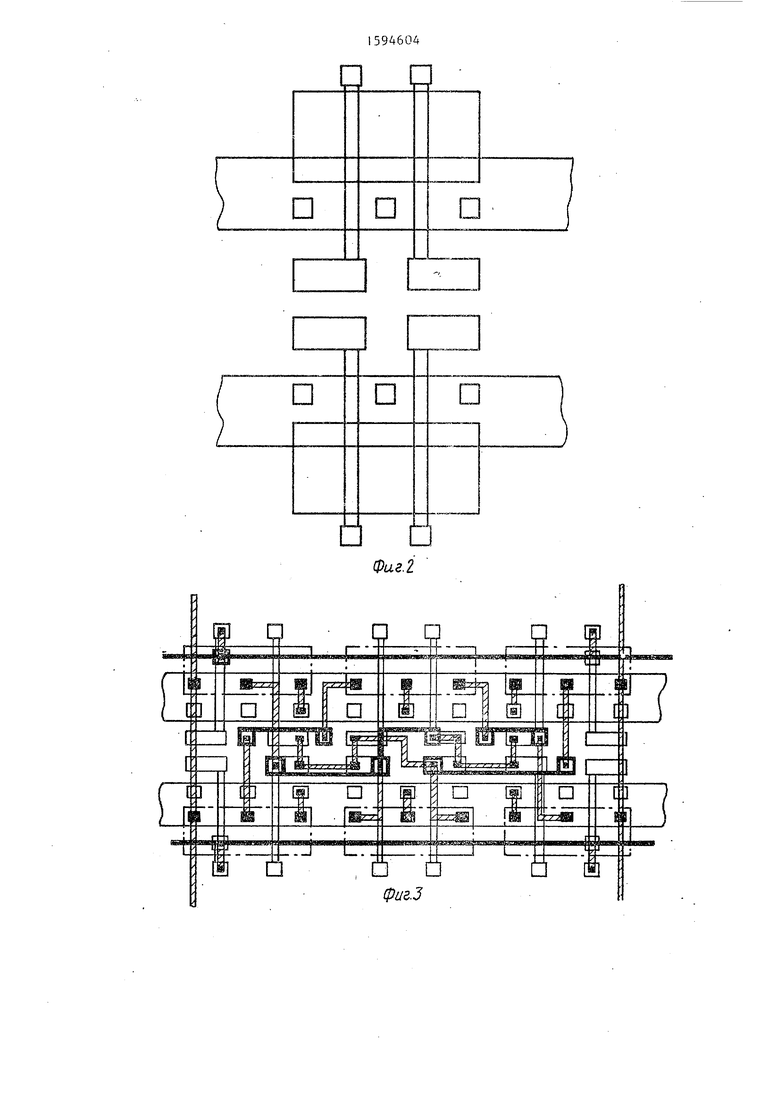

. На фиг. 1 представлена принципиальная схема элемента памяти; на , фиг. 2 - топология ячейки БЖ; на фиг. 3 - топологическая реализация элемента памяти.

Элемент памяти содержит первый 1 второй 2, третий Зи четвертый 4 элемен - ты НЕ, третий 5, первый 6, четвертый / и второй 8 ключевые элементы на транзисторах, первую 9 и вторую 10 адресные шины, прямую И и инверсную ,1 разрядные шины.

Элемент памяти работает следующим образом.

Элементы НЕ 1 и 2 образуют триг- герное кольцо,, которое осуществляет функцию хранения информации. Элементы НЕ 3 и 4 предназначены дай операции чтения. Поскольку информация с

триггерного кольца поступает на вхо- - ды элементов НЕ 3 и 4, то влияния емкости разрядах щин I 1 и 12 при операции счь тываш я (открываются транзисторы 7 и 8 р-каналь ие) при посту- плети на их затворы сигна)1а О нет Следоватапьно, паразитная емкость на разряд.ных шинах 11 и 12 не оказывает ьшкяния на cocтoяшie триггера При этом считывается парафазная информация (разрядные шины 11 и 12) поэтому момент истинной сш танной ин- Формации легко определяется при наличии парафазы 1.0 „ли 0,1. Запись информации осущесталяется поступлеш ем парафазной информации на разрядные шины и 12 и открыванием транзисторов 5 и 6 (п-канапьные транзисторы) поступление по шине 9 уровня 1. Поскольку при записг все равно необходим этап воздействия на триггерное кольцо, то в этом случае не важно наличие паразитной емкости на шинах II и 12.

У

)ыв;з

Предлагаемая развязка по считыва-; 1ШЮ и записи значительно повышает на- дежные характеристики элемента памяг- ти. Подобная организация не ограни- гшвает потребителя,, При этом выбраны ключевые элементы на транзисторах д:у1Я записи и считывания различного типа проводи:мости9 что позволяет достичь симметричности и полного топологичес- кого покрытия принципиальной схемой ячеистой структуры БМК, Это видно на примере реализации элемента памяти на основе БМК, На (jMr. 2 - ячейка 13Mk, на фиг, 3 - тополо:гая элемента памя-i ти (двухуровневая разводка- А I и А2) ,

Использование однотипных (по геометрическим размерам) транзисторов позволяет эффективней использовать площадь БМК,

Развязка по считывателю и записи повышает надежность устройства и позволяет строить накопитель ОЗУ произвольной емкости с неразрушаощим чтением.

Возможность определения считыва- ния истинной информа дии по напичию парафазы 1 0 или 0,1 на 11рямой и инверсной разрядных пшнах позволяет не производать сложных расчетов време)н- |ных параметров ддя упрагшяющих схем k гарантирует работу устройства при изменении электрофизических параметров транзисторов, т,е, если транзис- -торы работают (перекпюч;иотся с любыми временными характеристиками), то аботает устройство.

ормула изобретения

Элемент памяти, содержащий первый второй элементы НЕ, первый и второй ключевые элементы на транзисторах, стоки которых подключены к прямой разрядной шине, а затворы подключены соответственно к первой и второй адресным шинам, исток транзистора первого ключевого элемента соединен с входом первого элемента НЕ и выходом второго элемента НЕ, вход которого соединен с выходом первого элемента НЕ, отличающийся тем, что, с целью повышения надежности элемента памяти, он содержит третий и четвертый элементы НЕ и третий и четвертый ключевые элементы на транзисторах, стоки которых подключены к инверсной разрядной шине, а затворы - к первой и второй адресным шинам соответственно,, выход второго элемента.НЕ соединен с вхо- дом четвертого элемента НЕ, выход которого -соединен с истоком транзистора четвертого ключевого элемента, выход третьего элемента НЕ соединен с истоком второго транзистора второго ключевого элемента, а вход - с истоком транзистора третьего ключевого элемента.

П D

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, реализуемых на базовых матричных кристаллах. Целью изобретения является повышение надежности элемента памяти. Для этого в элемент памяти введены третий и четвертый элементы НЕ и третий и четвертый ключевые элементы на транзисторах. 3 ил.

Фиг.2

| IEEE journal of Solid-State Circuits | |||

| Vol | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| УСТРОЙСТВО ДЛЯ ОТБОРА ПРОБ | 1966 |

|

SU224887A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1990-09-23—Публикация

1988-09-28—Подача