(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации логических функций | 1989 |

|

SU1619247A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Устройство для выбора заданного числа повторений двоичных чисел | 1984 |

|

SU1267402A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство управления микропрограммной ЭВМ | 1989 |

|

SU1691840A1 |

| Устройство для масштабирования числа в интервально-модулярном коде | 1986 |

|

SU1305678A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования цифровых устройств. Цель изобретения - упрощение и увеличение быстродействия. Устройство содержит генератор импульсов 1, три счетчика 2,3,4, дешифратор 5, мультиплексор 7, блок сравнения 8, блок индикации 10. Цель изобретения достигается за счет введения дешифратора 6 и блока хранения результатов 9. 2 з.п. ф-лы, 3 ил.

сд

о

о

00 СП

со

иг.1

Изобретение относится к выш:. . тельной технике и может быть использовано в системах тестового диагностирования.

Целью изобретения является упрощение и увеличение быстродействия устройства.

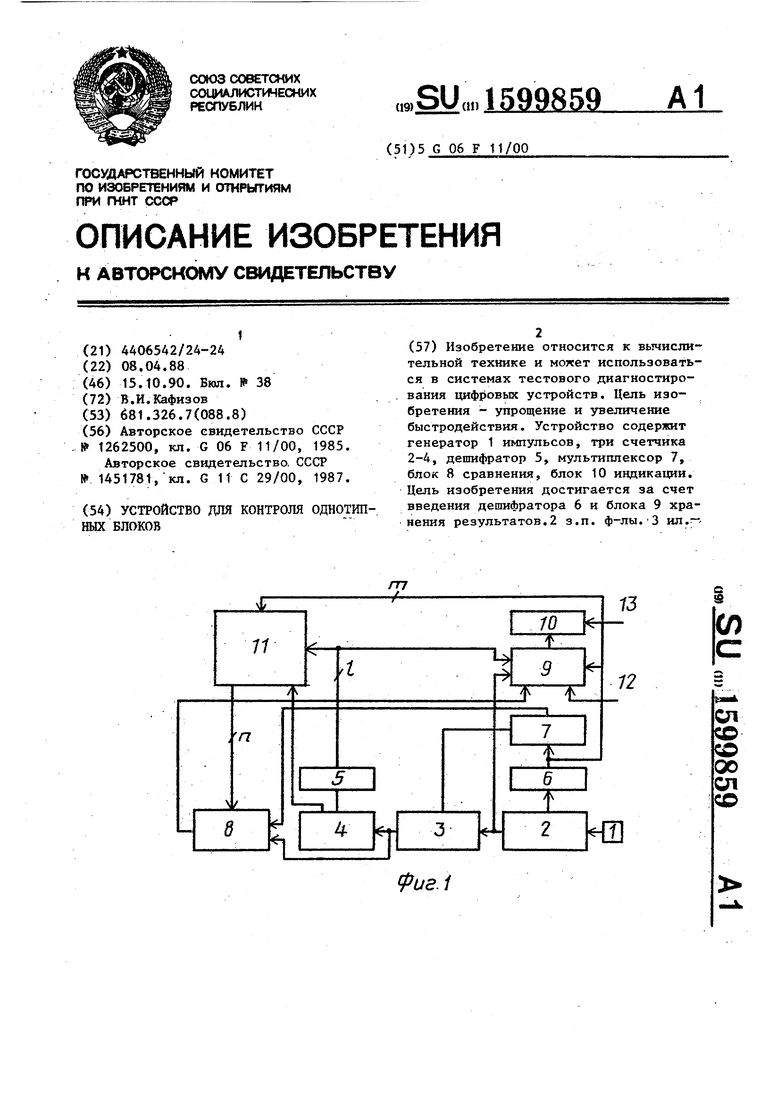

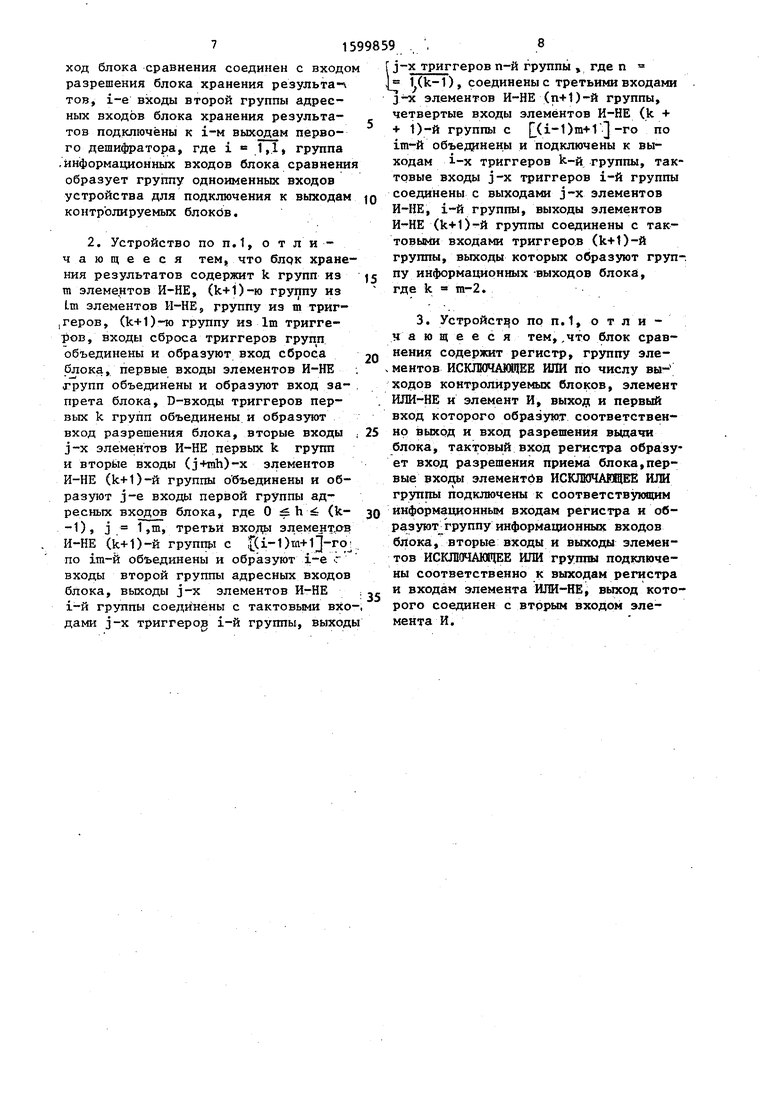

На фиг.1 приведена функциональная схема устройства; на фиг.2 - логическая схема блока хранения результатов; на фиг.З - схема блока сравне- ния.,

Устройство (фиг.1) содержит генератор 1 импульсов, счетчик 2, счетчик 3, счетчик 4, дешифратор 5, дешифратор 6, мультиплексор 7, блок 8 сравнения, блок 9 хранения результатов, блок 10 индикации, объект 11 контроля, входы сброса 12 и разрешения 13.

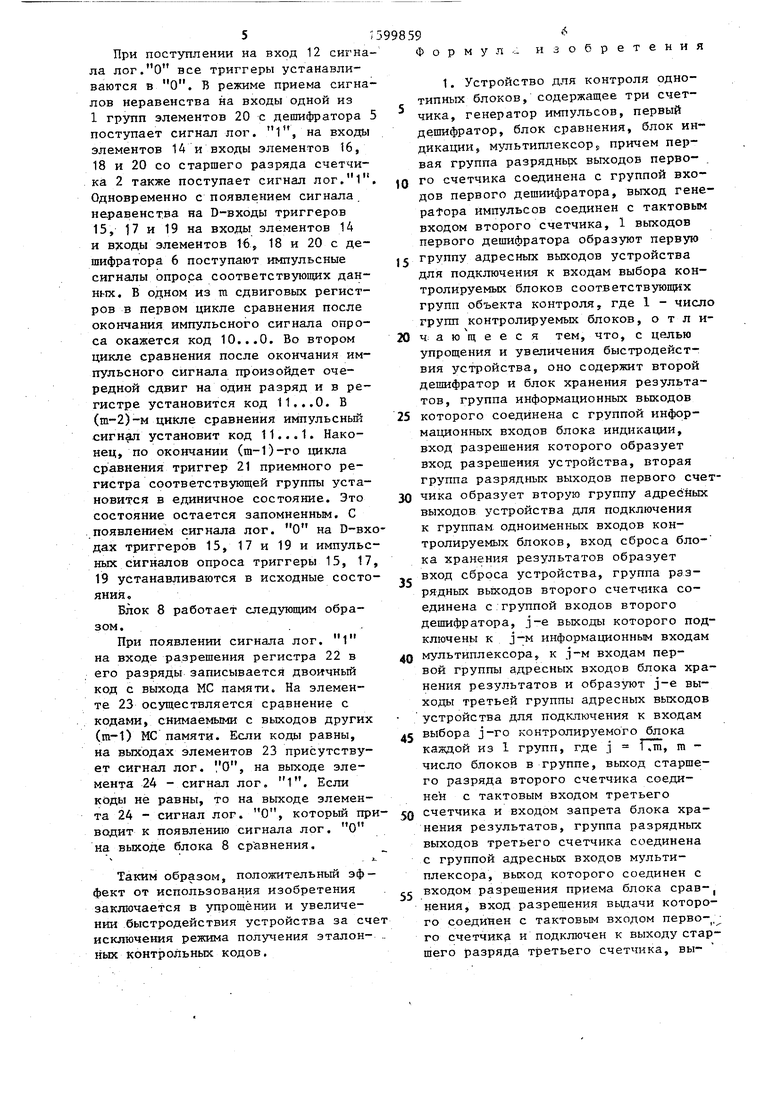

Блок 9 хранения результатов (фиг.2) содержит первую группу 1.4 элементов И-НЕ, первую группу 15 триггеров, вторую группу 16 элементов И-НЕ,вторую группу 17 триггеров, k-ю группу 18 элементов И-НЕ, k-ю группу 19 триггеров, (К+1)-ю группу 20 элементов И-НЕ, (и+1)-ю группу 21 триггеров; j-e триггеры групп с первой по k-ю включительно образуют m регистров сдвига, (k+1)-я группа триггеров образует 1 т-разрядных регистров, k га-2.

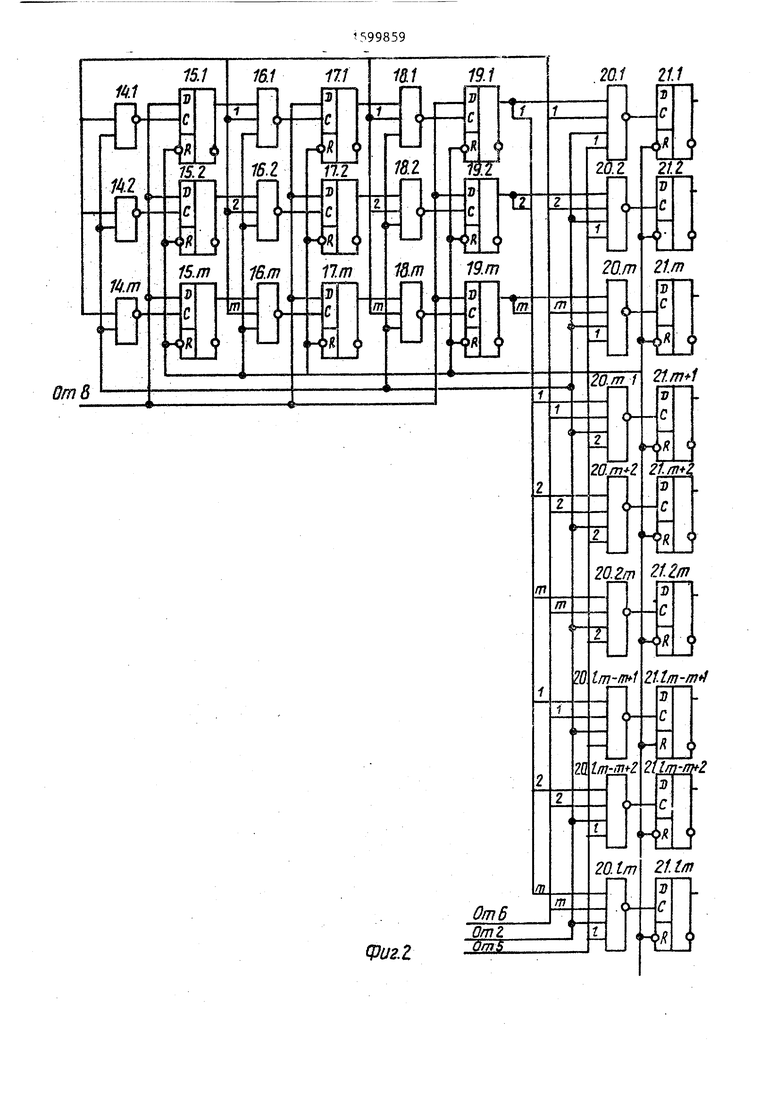

Блок 8 сравнения (фиг.З) состоит из регистра 22, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 23, количество которых равно максимальному количеству п выходов контролируемых блоков, элемента ИЛИ-НЕ 24 и элемента И 25.

Предположим, что объект 11 содержит 1 групп блоков по m блоков с одинаковым содержанием информации в каждой группе. Причем m 5 3. Работу устройства ра.ссмотрим на примере контроля 1 групп микросхем памяти серии 556 по m -микросхем в каждой rpjnn пе.

Устройство работает следующим образом.

Перед началом работы.по входу 12 блок 9 устанавливается в исходное состояние. Импульсы генератора 1 лодсчитьшаются счетчиками 2-4. По состоянию счетчика 4 опрашиваются адреса всех 1т микросхем (МС) памяти объекта 11. Сигналами с выхода дешифратора 5 выбирается для контроля очередная группа МС, а по состоя0

5

0

5

0

5

0

5

0

5 ,с

ниш счетчика 2 сигналами с вых. а дешифратора 6 из этой группы выбирается нужная МС памяти. Информационные сигналы выбранной МС памяти поступают с выхода объекта 11 на вход блока 8, По состояниям счетчиков 2 и 3 с помощью дешифратора 6 и мультиплексора 7 формируется импульсный сигнал, который поступает на вход разрешения приема блока 8. Через второй вход блока 8 проходят сигналы с выходов одной из m МС группы и поочередно сравниваются с сигналами с выходов других (та-1) МС той же группы. Процесс фиксации сигналов неравенства блоком 9 осуществляется после появления в старшем разряде счетчика 3 сигнала лог.1. В первом цикле пересчета счетчика 2 блок 9 находится в исходном состоянии, а во втором цикле сигналом лог. 1 с выхода старшего разряда счетчика 2 блоку 9 дается разрешение на фиксацию сигналов неравенства. Это делается для того, чтобы по текущему адресу процессом сравнения были охвачены все контролируемые данные. .-Если в проверяемой группе данных комбинация сигналов сравниваемого кода отличается от остальных сигналов данных (т-1) раз, то этот код является недостоверным. Поэтому каждое появление сигнала неравенства на выходе блока 8 фиксируется в блоке 9. Как только в блок 9 посту- пит количество сигналов неравенства (т-1) раз, то он сформирует сигнал недостоверности соответствующих кон- тролируемых данных в группе. Под действием постоянного сигнала недостоверности блок ТО осуществляет ивдици- рование этих данных. Процесс фиксации сигналов неравенства прекращается после появления в старшем разряде счетчика 3 Сигнала лог. О. Этот сигнал поступает на вход разрешения выдачи блока-8 и изменяет- состояние счетчика 4. Теперь до появления в старших разрядах счетчиков 2 и 3 сигнала лог. М. блок 9 очищается от результатов предьщущей фиксации неравенства. Причем запоминаемые и индицируемые недостоверные данные остаются до тех пор, пока на вход 12 не поступит сигнал сброса.

Блок 9 работает следующим образом.

При поступлении на вход 12 сигнала лог.О все триггеры устанавливаются в О. В режиме приема сигналов неравенства на входы одной из 1 групп элементов 20 с дешифратора поступает сигнал лог. 1, на входы элементов 14 и входы элементов 16,

18и 20 со старшего разряда счетчика 2 также поступает сигнал лог,1 Одновременно с появлением сигнала неравенства на D-БХОДЫ триггеров

15, 17 и 19 на входы элементов 14 и вкоды элементов 16, 18 и 20 с дешифратора 6 поступают импульсные сигналы опроса соответствующих дан- ннх. В одном из m сдвиговых регистров в первом цикле сравнения после окончания импульсного сигнала опроса окажется код 10,..0. Во втором цикле сравнения после окончания импульсного сигнала произойдет очередной сдвиг на один разряд и в регистре установится код 11...0. Б (т-2)-м сравнения импульсный сигнал установит код 11... 1. Наконец, по окончании (m-l)-ro цикла сравнения триггер 21 приемного ре- rHCTpia соответствующей группы установится в единичное состояние. Это состояние остается запомненным. С появлением сигнала лог. О на D-BX дах триггеров 15, 17 и 19 и импульс ньк сигналов опроса триггеры 15, 17

19устанавливаются в исходные состояния.

Блок 8 работает следующим образом..

При появлении сигнала лог. 1 на входе разрешения регистра 22 в его разряды записывается двоичный код с выхода МС памяти. На элементе 23 осуществляется сравнение с кодами, снимаемыми с выходов других (т-1) НС памяти. Если коды равны, на выходах элементов 23 присутствует сигнал лог. 0, на выходе элемента 24 - сигнал лог. 1. Если коды не равны, то на выходе элемента 24 - сигнал лог. О, который прводит к появлению сигнала лог. О на выходе блока 8 ср авнения,

%..

Таким образом, положительный эффект от использования изобретения заключается в упрощении и увеличении быстродействия устройства за сч исключения режима получения эталон- ных контрольных кодов.

1599859

Формул.и

р е т е н и я

0

5 группу адресных выходов устройства для подключения к входам выбора контролируемых блоков соответствующих групп объекта контроля, где 1 - число групп контролируемых блоков, о т л и- ч а ю щ е е с я тем, что, с целью упрощения и увеличения быстродействия устройства, оно содержит второй дешифратор и блок хранения результатов, группа информационных выходов

5 которого соединена с группой информационных входов блока индикации, вход разрешения которого образует вход разрешения устройства, вторая группа разрядньк выходов первого счет0 чика образует вторую группу адресных выходов устройства для подключения к группам одноименных входов контролируемых блоков, вход сброса бло- ка хранения результатов образует вход сброса устройства, группа разрядных вь&одов второго счетчика соединена с группой входов второго дешифратора, j-e выходы которого подключены к J-M информационным входам мультиплексора, к входам первой группы адресных входов блока хранения результатов и образуют j-e выходы третьей группы адресных выходов устройства для подключения к входам

с выбора j-ro контролируемого блока

5

0

0

каждой из 1 групп, где j , m - число блоков в группе, выход старшего разряда второго счетчика соединен с тактовым входом третьего счетчика и входом запрета блока хранения результатов, группа разрядных выходов третьего счетчика соединена с группой адресных входов мультиплексора, выход которого соединен с входом разрешения приема блока срав-, нения, вход разрешения выдачи которого соединен с тактовым входом перво-, го счетчику и подключен к выходу старшего разряда третьего счетчика, выход блока сравнения соединен с входо разрешения блока хранения результа-п тов, i-e входы второй группы адресных входов блока хранения результатов подключены к i-м выходам первого дешифратора, где i « 1,1 группа .информационных входов блока сравнени образует группу одноименных входов устройства для подключения к выходам контролируемых блоков.

j-x триггеров п-й группы , где п «

1,(k-1) , соединены с третьими входами 3/-Х элементов И-НЕ (п+1)-й группы, четвертые входы элементов И-НЕ (k + + 1)-й группы с (i-l)m-t-l Q-го по im-й объединены и подключены к выходам i-x триггеров k-й группы, тактовые входы j-x триггеров i-й группы соединены с выходами j-x элементов И-НЕ, i-й группы, выходы элементов И-НЕ (k+1)-й группы соединены с так- входами триггеров (k+1)-й группы, выходы которых образуют груп-. пу информационных-выходов блока, где k m-2.

П

22

Ш 24F

-nS

-Г1-

Ф(/г

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство | |||

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-10-15—Публикация

1988-04-08—Подача