Изобретение относится к электронной вычислительной технике и может быть использовано при построении электрических программируемых запоминающих устройств на лавинно-инжекционных МДП-транзисторах с плавающим затвором и ультрафиолетовым стиранием информации.

Цель изобретения - снижение потребляемой мощности дешифратора.

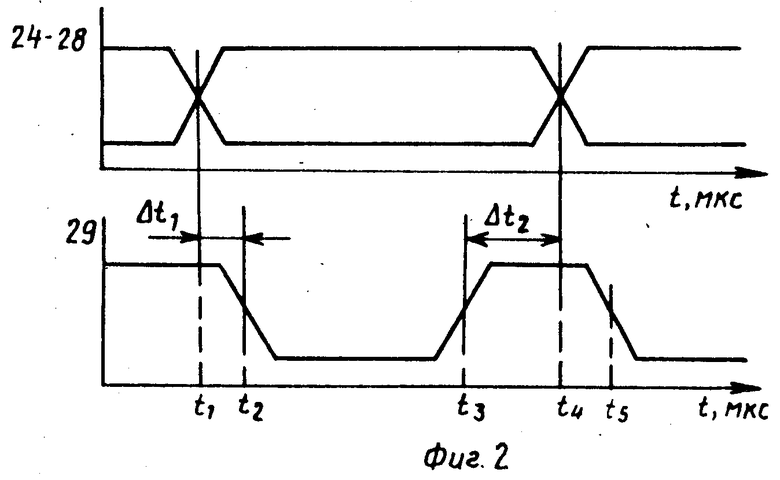

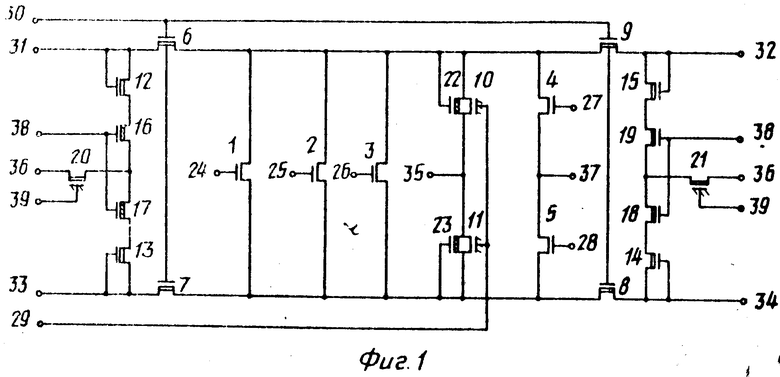

На фиг. 1 представлена электрическая схема дешифратора; на фиг.2 - временные диаграммы его работы.

Дешифратор адреса содержит адресные транзисторы 1-5, транзисторы 6 - 9 связи, первый и второй ключевые транзисторы 10 и 11, четыре нагрузочных транзистора 12 - 15, ключевые транзисторы 16 - 21 с третьего по восьмой, пятый и шестой нагрузочные транзисторы 22 и 23, адресные входы 24 - 28, первый и второй входы 29 и 30 управления режимом дешифратора, выходы 31-34, первую и вторую шины 35 и 36 питания, шину 37 нулевого потенциала, третий и четвертый входы 38 и 39 управления режимом дешифратора. Транзисторы 10 и 11 имеют пороговое напряжение 0 ± 0,2 В, транзисторы 1-5 - пороговое напряжение 0,6 ± 0,2 В, транзисторы 6-9, 12 - 15 - пороговое напряжение - 3,0 ± 0,5 В, транзисторы 20-23 - пороговое напряжение - 2,0 ± 0,5 В, транзисторы 16 - 19 - пороговое напряжение - 1,5 ± 0,5 В.

Дешифратор работает следующим образом.

1. Режим считывания. При считывании на входы 24 - 28 подается адресная комбинация, состоящая из прямого и инверсного кодов. Пусть на затворы транзисторов 1, 2, 3 и 5 приходит потенциал низкого уровня (логический 0), а на затвор (вход 27) транзистора 4 приходит потенциал высокого уровня (логическая 1). Вследствие этого транзисторы 1 - 3 и 5 находятся в закрытом состоянии, а транзистор 4 открыт. Напряжение на первой шине 35 питания может устанавливаться равным напряжению на шине 36. На шину 35 питания в режиме считывания подается напряжение, равное 5 ± 0,5 . На входе 29 формируется сигнал от устройства задержки. На вход 38 поступает потенциал низкого уровня, близкий к нулю. На входах 30 и 39 устанавливается потенциал высокого уровня, близкий к потенциалу шины 35. Транзисторы 6-9 находятся в открытом состоянии, так как их затворы подключены к входу 30 с высоким потенциалом. За промежуток времени от t1 до t2 (см. фиг.2), пока устанавливается адресный код, через транзисторы 10 и 11 протекает импульсный ток от шины 35 в течение времени Δt1. После перехода потенциала входа 29 из состояния высокого уровня в состояние низкого уровня транзисторы 10 и 11 закрываются, а импульсный ток через эти транзисторы прекращается. Сопротивление транзисторов 12 - 15 и 22, 23 очень большое, протекающий ток через такой транзистор может изменяться от 5 до 20 мкА и зависит от изменения электрофизических параметров структур в процессе изготовления пластин. Транзисторы 20 и 21 открыты, так как напряжение на их затворах равно потенциалу шины 35. В результате потенциал на стоках транзисторов 16 - 19 устанавливается равным потенциалу шины 36 питания. Затворы транзисторов 16 - 19 находятся под потенциалом шины 38, т.е. под потенциалом низкого уровня. Поскольку транзисторы 16 - 19 выполнены со слабым обеднением, то они будут находиться в полузакрытом состоянии, и на стоки транзисторов 12 - 15 будет передаваться потенциал, примерно равный по абсолютной величине пороговому напряжению 1,5 ± 0,5 В. Через открытые транзисторы 6, 9 и транзистор 4, выходы 31, 32 и подключенные к ним нагрузочные емкости разряжаются до потенциала, близкого к потенциалу шины 37. Выходы 33 и 34 с подключенными к ним нагрузочными емкостями остаются в заряженном состоянии до высокого уровня, так как транзисторы 1-3,5 закрыты и транзисторы 17 и 18 тоже находятся в закрытом состоянии. В результате гальваническая связь между выходами 33, 31 и 34, 32 через транзисторы 13, 17, 16, 12 и 14, 18, 19, 15 отсутствует. Транзистор 23 служит для поддержания высокого уровня напряжения на выходах 33 и 34.

2. Режим хранения (невыбора). Данный режим обеспечивает полное исключение токов потребления дешифратора адреса от обеих шин 35 и 36 питания. Это обусловлено тем, что на входах 24 - 28 устанавливается низкий уровень, который и запирает транзисторы 1 - 5. На входах 30, 38, 39 сохраняется состояние режима считывания, а на входе 29 от устройства задержки формируется высокий уровень. Это позволяет через транзисторы 10 и 11 осуществлять быстрый заряд выходов 31 - 34 вместе с емкостными нагрузками до напряжения шины 35 минус пороговое напряжение транзисторов 10 или 11. В соответствии с временной диаграммой, приведенной на фиг.2, режим хранения (невыбора) осуществляется в промежутке времени 0-t2 и t3-t5, а в момент времени t2-t3 происходит процесс считывания. Промежуток времени от t1 до t4 является циклом считывания дешифратора адреса и определяет его быстродействие (частоту обращения). Время Δ t2 определяется фронтом нарастания на входе 29 от устройства задержки, а также от токоформирующих свойств транзисторов 10 и 11, которые и определяют заряд выходов 31-34 с их емкостными нагрузками.

3. Режим программирования. На шину 36 питания подается высокое напряжение, равное, например, 18 ± 0,5 В. На шину 35 пи- тания подается напряжение, равное 5 ± 0,5 В. При этом временная диаграмма, приведенная на фиг.2, сохраняет силу и для данного режима. Вход 30 обнуляется в данном режиме, а на входе 29 напряжение формируется строго с задержкой относительно напряжений на адресных входах 24-28. На входах 38 и 39 устанавливается напряжение шины 36. При этом заряд выходов 31 - 34 с нагрузочными емкостями до потенциала шины 36 происходит, например, через открытые транзисторы 20, 17 и 21, 18, а также через транзисторы 13 и 14. Для этого необходимо допустить, что входные транзисторы 1 - 3, 5 закрыты, а входной транзистор 4 открыт. Будем использовать терминологию: выходы 31 и 32 являются первой строкой, а выходы 33 и 34 являются второй строкой. Первая строка обнуляется, так как открыт входной транзистор 4. Вследствие того, что на затворах транзисторов связи 6-9 устанавливается нулевой потенциал через вход 30, а на истоках транзисторов 7 и 8 поддерживается напряжение шины 35 через транзистор 23, транзисторы 7 и 8 переходят в закрытое состояние, а через последовательные цепочки транзисторов 20, 17, 13 и 21, 18, 14 происходит заряд второй строки до полного напряжения шины 36. В момент времени 0-t2 и t3-t5, когда открываются транзисторы 10 и 11 и закрываются все транзисторы 1-5, все транзисторы связи 6-9 переходят в закрытое, а первая и вторая строки заряжаются до напpяжения шины 36. Необходимо отметить, что в режиме программирования потребляемая мощность дешифратором адреса возрастает за счет увеличения тока потребления от шины 36 и будет превышать потребляемую мощность в режиме считывания.

4. Адаптивный режим программирования. В данном режиме объединены все три предыдущих режима работы дешифратора адреса. Отличие заключается только в том, что считывание и хранение (невыбор) производятся при высоком напряжении на шине 36 (18 ± 0,5 В). В данном режиме на шину 35 подается напряжение, равное 6,0 ± 0,25 В, для того, чтобы контроль записанной информации осуществлялся с большим запасом, чем максимальное рабочее напряжение. Вход 30 в режимах хранения и считывания имеет потенциал шины 35, а в режиме пограммирования переходит в состояние с низким потенциалом, близким к нулю. Вход 29 формируется от устройства задержки в соответствии с временной диаграммой (см. фиг.2), т.е. в режиме хранения она находится под потенциалом шины 35, а в режимах считывания (программирования) - под низким потенциалом, близким к нулю. Вход 38 в режимах хранения и считывания находится под низким потенциалом, а в режиме пpограммирования на нее подается напряжение шины 36. Вход 39 в режимах хранения и считывания находится под потенциалом шины 35, а в режиме программирования на нее подается напряжение шины 36. Все режимы работы подробно описаны выше.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Элемент памяти | 1984 |

|

SU1163356A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании СППЗУ на лавинно-инжекционных МДП-транзисторах с плавающим затвором. Цель изобретения - снижение протребляемой мощности дешифратора. Поставленная цель достигается введением в дешифратор адреса нагрузочных транзисторов 22, 23 и ключевых транзисторов 20, 21 с соответствующими связями. Транзисторы 22, 23 ограничивают потребляемый ток. В режиме считывания и хранения на вход 38 подается сигнал низкого уровня, запирающий ключевые транзисторы 16-19. 2 ил.

ДЕШИФРАТОР АДРЕСА, содержащий пять адресных транзисторов, четыре транзистора связи, шесть ключевых транзисторов, четыре нагрузочных транзистора, затворы адресных транзисторов являются адресными входами дешифратора, стоки адресных транзисторов с первого по четвертый соединены с истоками первого и четвертого транзисторов связи и стоком первого ключевого транзистора, исток которого подключен к первой шине питания дешифратора и соединен с истоком второго ключевого транзистора, а затвор является первым входом управления режимом дешифратора и соединен с затвором второго ключевого транзистора, сток которого соединен с истоками первого, второго, третьего, пятого адресных транзисторов и истоками второго и третьего транзисторов связи, затворы которых соединены с затворами первого и четвертого транзисторов связи и являются вторым входом управления режимом дешифратора, исток четвертого адресного транзистора соединен со стоком пятого адресного транзистора и подключен к шине нулевого потенциала дешифратора, выходами которого являются стоки транзисторов связи с первого по четвертый соответственно, которые соединены со стоками и затворами нагрузочных транзисторов с первого по четвертый соответственно, истоки которых соединены со стоками ключевых транзисторов с третьего по шестой соответственно, затворы которых объединены и являются третьим входом управления режимом дешифратора, истоки третьего и пятого ключевых транзисторов соединены с истоками четвертого и шестого ключевых транзисторов соответственно, отличающийся тем, что, с целью снижения потребляемой мощности, дешифратор содержит пятый и шестой нагрузочные транзисторы, стоки и истоки которых соединены со стоками и истоками первого и второго ключевых транзисторов соответственно, а затворы - со стоками первого и второго ключевых транзисторов соответственно, седьмой и восьмой ключевые транзисторы, истоки которых соединены с истоками третьего и пятого ключевых транзисторов соответственно, стоки подключены к второй шине питания дешифратора, а затворы объединены и являются четвертым входом управления режимом дешифратора.

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-12-30—Публикация

1989-09-29—Подача