сь

4 О ч|

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1095240A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Резервированное запоминающее устройство | 1989 |

|

SU1716572A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1037348A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

Изобретение относится к вычислительной технике и предназначено для использования в устройствах повышенной надежности, в частности для запоминающих устройств специализированных вычислительных машин. Целью изобретения является повышение надежности устройства. Каждый канал многоканального резервированного запоминающего устройства содержит накопитель 1, блок 4 сравнения, блок 8 управления, коммутатор 13, первую 14 и вторую 17 группы сумматоров по модулю два, регистр 15 и группу элементов И 16, Изобретение позволяет повысить надежность устройства за счет введения раздельного резервирования на уровне одного бита. При отказе накопителя одного канала в устройстве осуществляется восстановление отказавших разрядов за счет сравнения с информацией исправного канала. Если отказавшие разряды появляются в нескольких каналах, то их восстановление осуществляется за счет введения временной избыточности и дополнительной операции сравнения с модифицированной информацией. 2 табл., 3 ил. сл с

I J7 I и Я

ФигЛ

Изобретение относится к вычислительной технике и предназначено для использо- вания в устройствах повышенной надежности, в частности для запоминающих устройств специализированных вычис- лительных машин.

Цель изобретения - повышение надежности устройства.

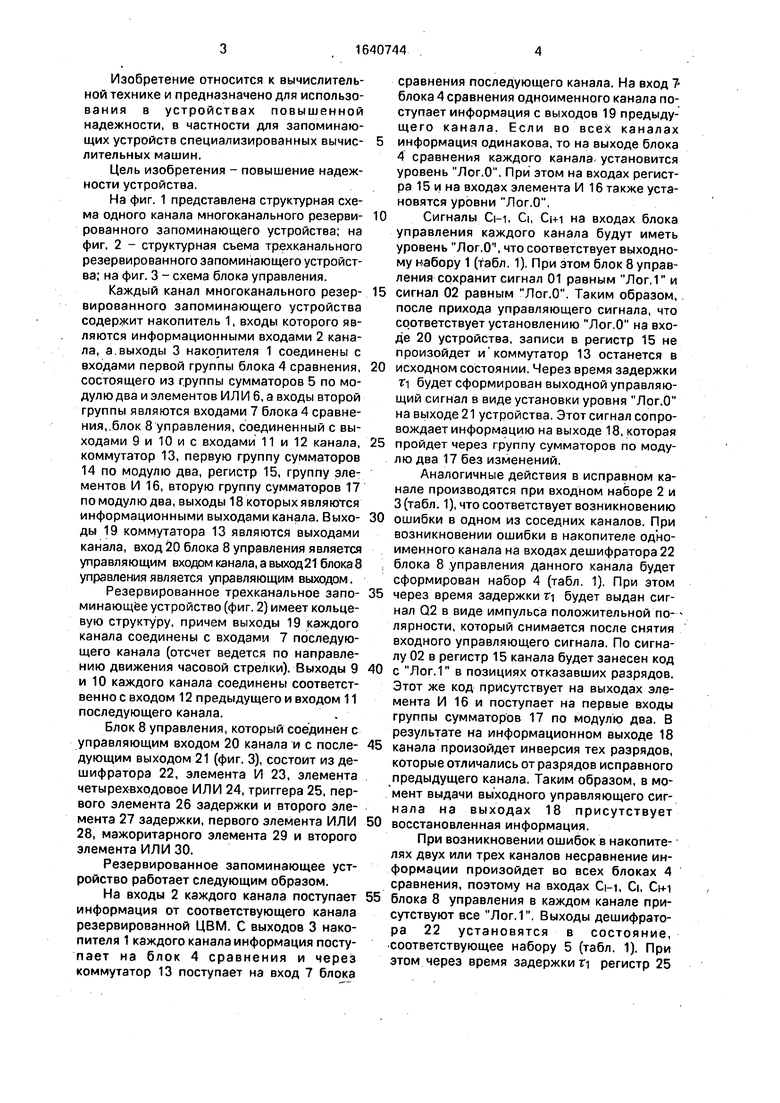

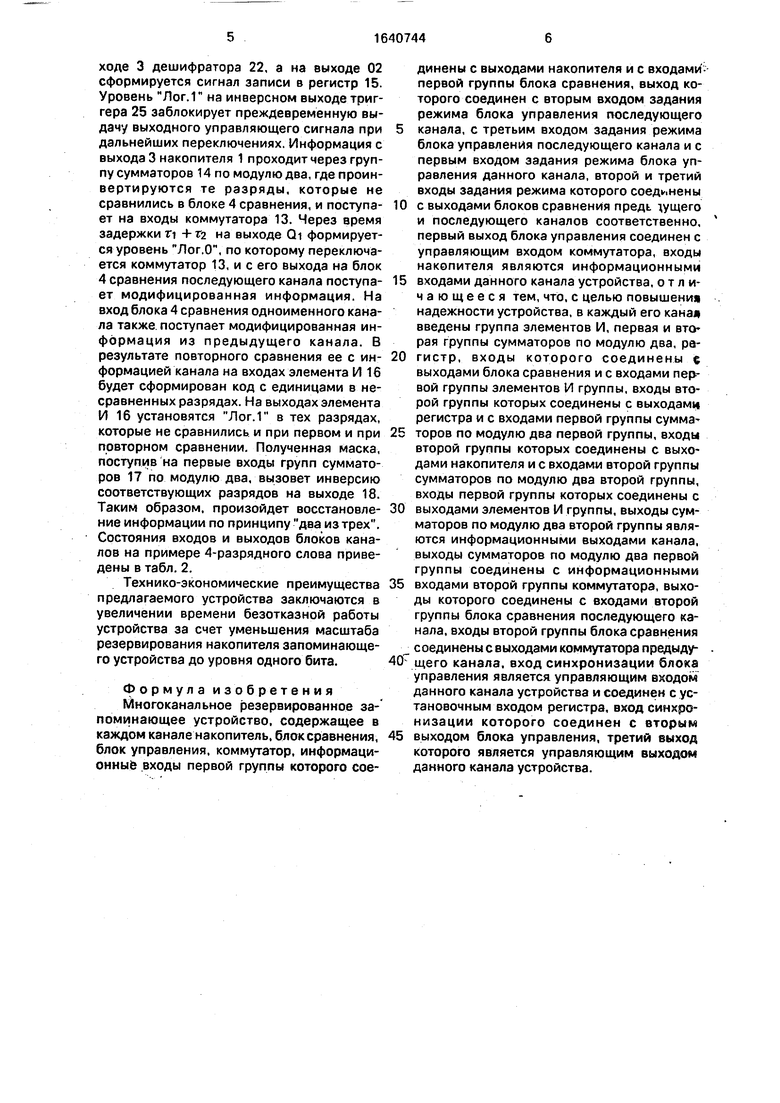

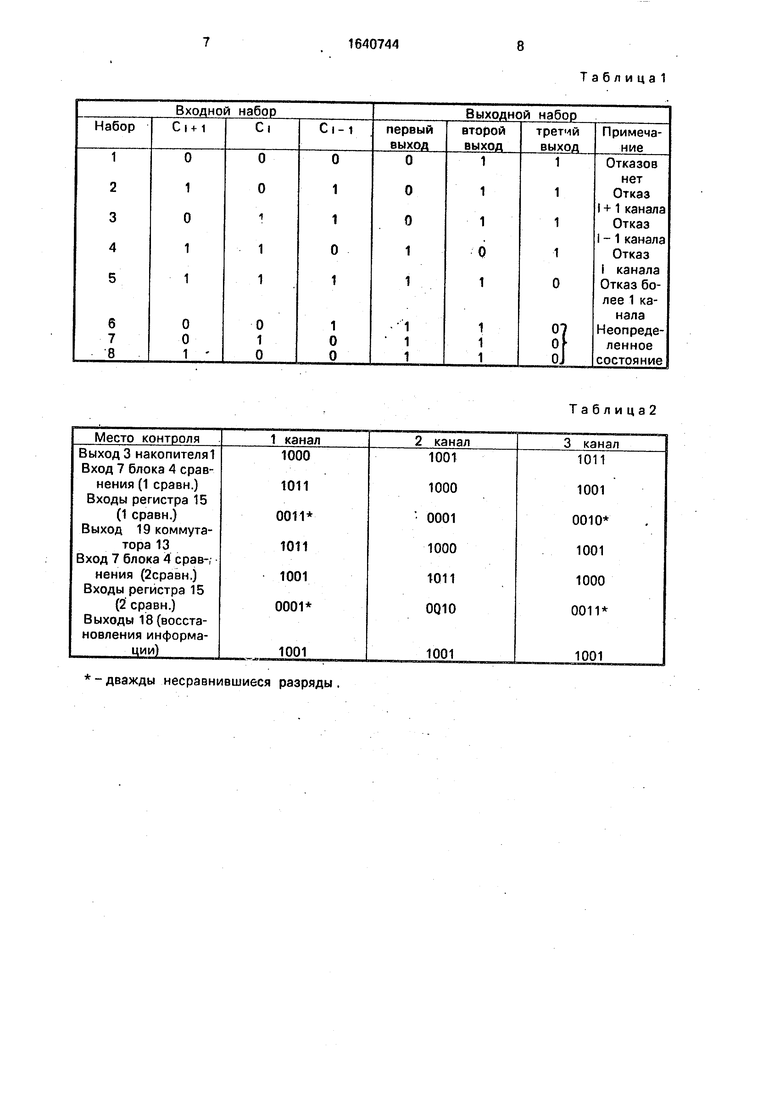

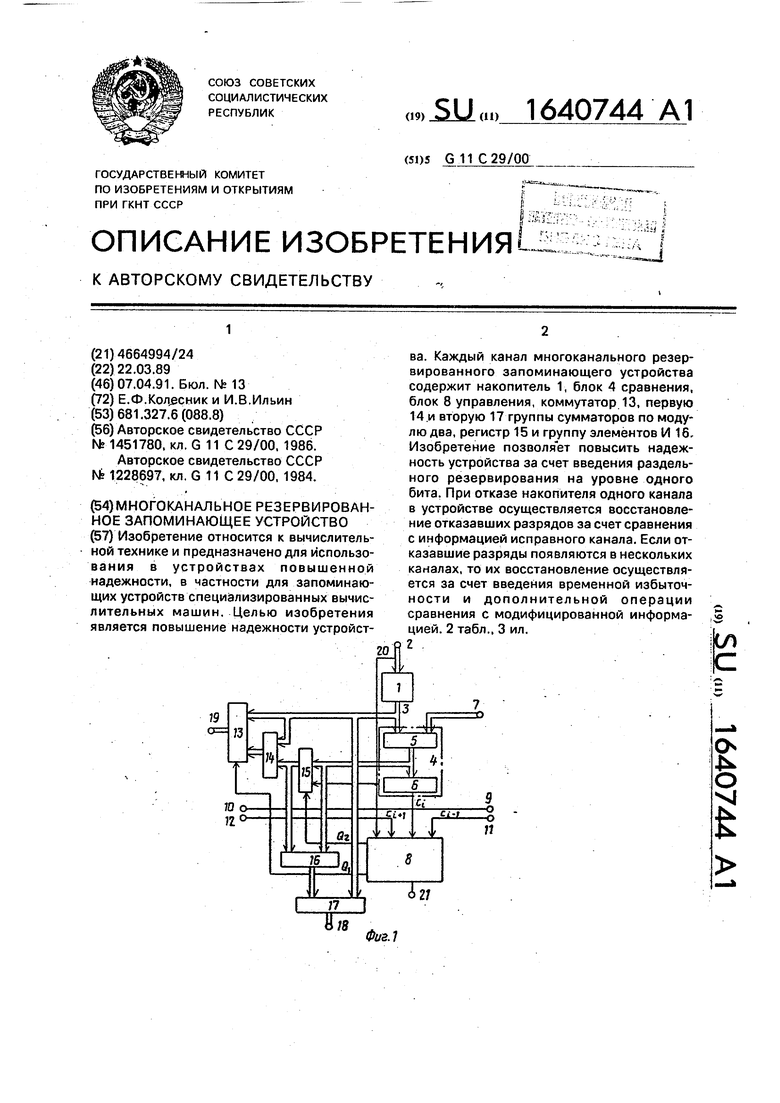

На фиг. 1 представлена структурная схема одного канала многоканального резерви- рованного запоминающего устройства; на фиг. 2 - структурная съема трехканального резервированного запоминающего устройства; на фиг. 3 - схема блока управления.

Каждый канал многоканального резер- вированного запоминающего устройства содержит накопитель 1, входы которого являются информационными входами 2 канала, а выходы 3 накопителя 1 соединены с входами первой группы блока 4 сравнения, состоящего из группы сумматоров 5 по модулю два и элементов ИЛ И 6, а входы второй группы являются входами 7 блока 4 сравнения, блок 8 управления, соединенный с выходами 9 и 10 и с входами 11 и 12 канала, коммутатор 13, первую группу сумматоров 14 по модулю два, регистр 15, группу элементов И 16, вторую группу сумматоров 17 по модулю два, выходы 18 которых являются информационными выходами канала. Выхо- ды 19 коммутатора 13 являются выходами канала, вход 20 блока 8 управления является управляющим входом канала, а выход 21 блока 8 управления является управляющим выходом.

Резервированное трехканальное запо- минающее устройство (фиг. 2) имеет кольцевую структуру, причем выходы 19 каждого канала соединены с входами 7 последующего канала (отсчет ведется по направлению движения часовой стрелки). Выходы 9 и 10 каждого канала соединены соответственно с входом 12 предыдущего и входом 11 последующего канала.

Блок 8 управления, который соединен с управляющим входом 20 канала и с после- дующим выходом 21 (фиг. 3), состоит из дешифратора 22, элемента И 23, элемента четырехвходовое ИЛИ 24, триггера 25, первого элемента 26 задержки и второго элемента 27 задержки, первого элемента ИЛИ 28, мажоритарного элемента 29 и второго элемента ИЛИ 30.

Резервированное запоминающее устройство работает следующим образом.

На входы 2 каждого канала поступает информация от соответствующего канала резервированной ЦВМ. С выходов 3 накопителя 1 каждого канала информация поступает на блок 4 сравнения и через коммутатор 13 поступает на вход 7 блока

сравнения последующего канала. На вход блока 4 сравнения одноименного канала поступает информация с выходов 19 предыдущего канала. Если во всех каналах информация одинакова, то на выходе блока 4 сравнения каждого канала установится уровень Лог.О. При этом на входах регистра 15 и на входах элемента И 16 также установятся уровни Лог.О.

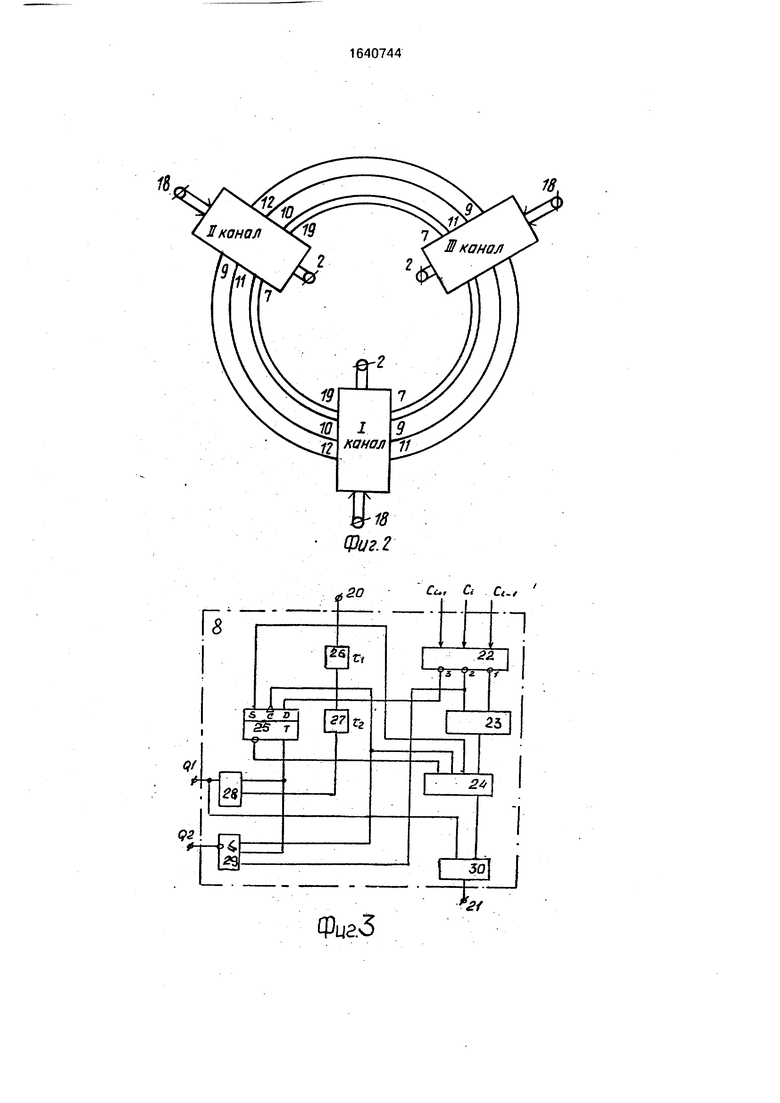

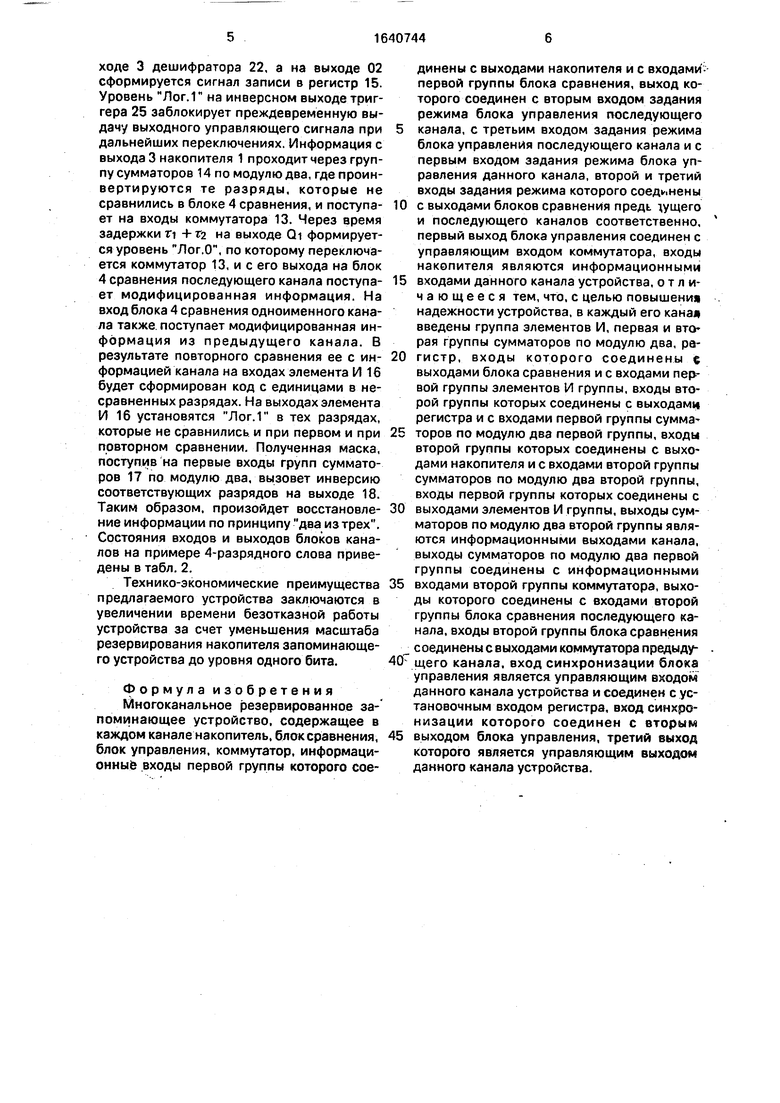

Сигналы См. Ci, Ci+i на входах блока управления каждого канала будут иметь уровень Лог.О11, что соответствует выходному набору 1 (табл. 1), При этом блок 8 управления сохранит сигнал 01 равным Лог.1 и сигнал 02 равным Лог.О. Таким образом, после прихода управляющего сигнала, что соответствует установлению Лог 0 на входе 20 устройства, записи в регистр 15 не произойдет и коммутатор 13 останется в исходном состоянии. Через время задержки Ti будет сформирован выходной управляющий сигнал в виде установки уровня Лог.О на выходе 21 устройства. Этот сигнал сопровождает информацию на выходе 18, которая пройдет через группу сумматоров по модулю два 17 без изменений.

Аналогичные действия в исправном канале производятся при входном наборе 2 и 3 (табл. 1), что соответствует возникновению ошибки в одном из соседних каналов. При возникновении ошибки в накопителе одноименного канала на входах дешифратора 22 блока 8 управления данного канала будет сформирован набор 4 (табл. 1). При этом через время задержки т будет выдан сигнал Q2 в виде импульса положительной полярности, который снимается после снятия входного управляющего сигнала. По сигналу 02 в регистр 15 канала будет занесен код с Лог.1 в позициях отказавших разрядов. Этот же код присутствует на выходах элемента И 16 и поступает на первые входы группы сумматоров 17 по модулю два. В результате на информационном выходе 18 канала произойдет инверсия тех разрядов, которые отличались от разрядов исправного предыдущего канала. Таким образом, в момент выдачи выходного управляющего сигнала на выходах 18 присутствует восстановленная информация.

При возникновении ошибок в накопителях двух или трех каналов несравнение информации произойдет во всех блоках 4 сравнения, поэтому на входах См, Ci, CI-M блока 8 управления в каждом канале присутствуют все Лог.1. Выходы дешифратора 22 установятся в состояние, соответствующее набору 5 (табл. 1). При этом через время задержки т регистр 25

ходе 3 дешифратора 22, а на выходе 02 сформируется сигнал записи в регистр 15. Уровень нЛог.1 на инверсном выходе триггера 25 заблокирует преждевременную выдачу выходного управляющего сигнала при дальнейших переключениях. Информация с выхода 3 накопителя 1 проходит через группу сумматоров 14 по модулю два, где проин- вертируются те разряды, которые не сравнились в блоке 4 сравнения, и поступает на входы коммутатора 13. Через время задержки п + Т2 на выходе Qi формируется уровень Лог.О, по которому переключается коммутатор 13, и с его выхода на блок 4 сравнения последующего канала поступает модифицированная информация. На вход блока 4 сравнения одноименного канала также поступает модифицированная информация из предыдущего канала. В результате повторного сравнения ее с информацией канала на входах элемента И 16 будет сформирован код с единицами в несравненных разрядах. На выходах элемента И 16 установятся Лог. Г в тех разрядах, которые не сравнились и при первом и при повторном сравнении. Полученная маска, поступив на первые входы групп сумматоров 17 по модулю два, вызовет инверсию соответствующих разрядов на выходе 18. Таким образом, произойдет восстановление информации по принципу два из трех. Состояния входов и выходов блоков каналов на примере 4-разрядного слова приведены в табл. 2.

Технико-экономические преимущества предлагаемого устройства заключаются в увеличении времени безотказной работы устройства за счет уменьшения масштаба резервирования накопителя запоминающего устройства до уровня одного бита.

Формула изобретения Многоканальное резервированное запоминающее устройство, содержащее в каждом канале накопитель, блок сравнения, блок управления, коммутатор, информационные входы первой группы которого соединены с выходами накопителя и с входами- первой группы блока сравнения, выход которого соединен с вторым входом задания режима блока управления последующего

канала, с третьим входом задания режима блока управления последующего канала и с первым входом задания режима блока управления данного канала, второй и третий входы задания режима которого соединены

с выходами блоков сравнения предь дущего и последующего каналов соответственно, первый выход блока управления соединен с управляющим входом коммутатора, входы накопителя являются информационными

входами данного канала устройства, отличающееся тем, что, с целью повышения надежности устройства, в каждый его какал введены группа элементов И, первая и вторая группы сумматоров по модулю два, рагистр, входы которого соединены е выходами блока сравнения и с входами первой группы элементов И группы, входы второй группы которых соединены с выходами регистра и с входами первой группы сумма

торов по модулю два первой группы, входы второй группы которых соединены с выходами накопителя и с входами второй группы сумматоров по модулю два второй группы, входы первой группы которых соединены с

выходами элементов И группы, выходы сумматоров по модулю два второй группы являются информационными выходами канала, выходы сумматоров по модулю два первой группы соединены с информационными

входами второй группы коммутатора, выходы которого соединены с входами второй группы блока сравнения последующего канала, входы второй группы блока сравнения соединены с выходами коммутатора предыдущего канала, вход синхронизации блока управления является управляющим входом данного канала устройства и соединен с установочным входом регистра, вход синхронизации которого соединен с вторым

выходом блока управления, третий выход которого является управляющим выходом данного канала устройства.

дважды несравнившиеся разряды

Т а б л и ц а 1

Таблица2

#.

20

Си, d Ct.,

| Трехканальное мажоритарное резервированное запоминающее устройство | 1986 |

|

SU1451780A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Авторское свидетельство СССР Мг 1228697, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-07—Публикация

1989-03-22—Подача