Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей в устройствах обработки данных и в вычислительных устройствах

1 елью изобретения является повышение быстродействия преобразователя и расширение диапазона преобразования.

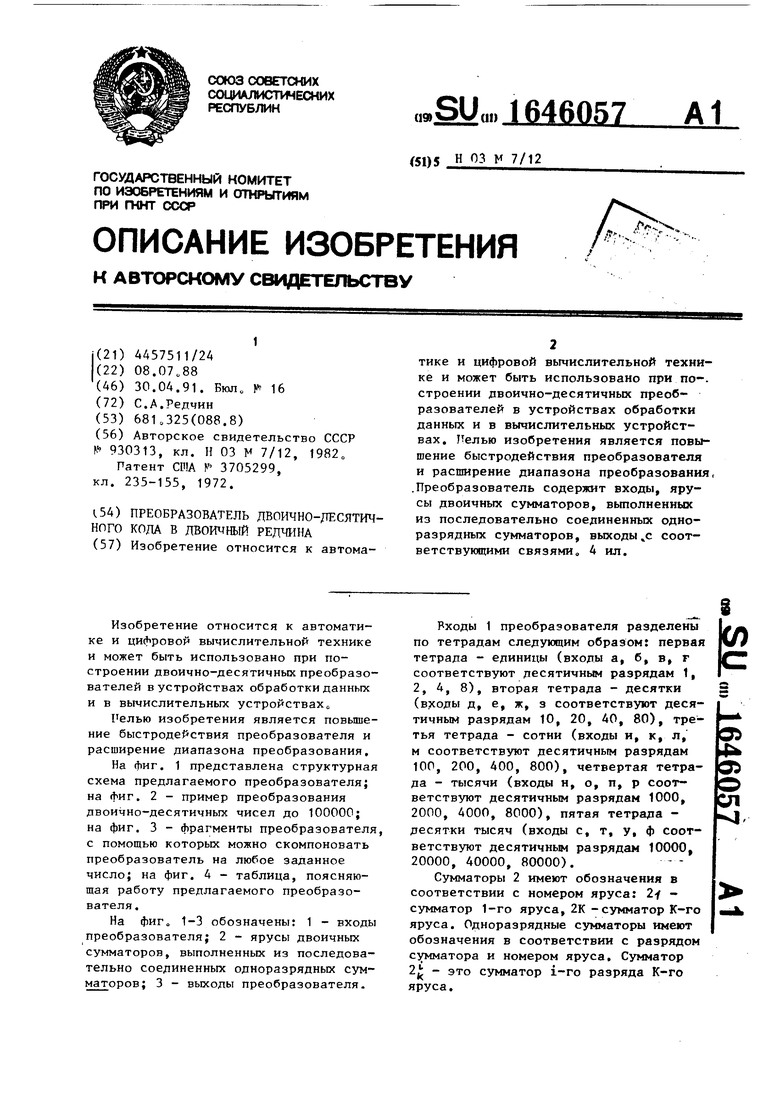

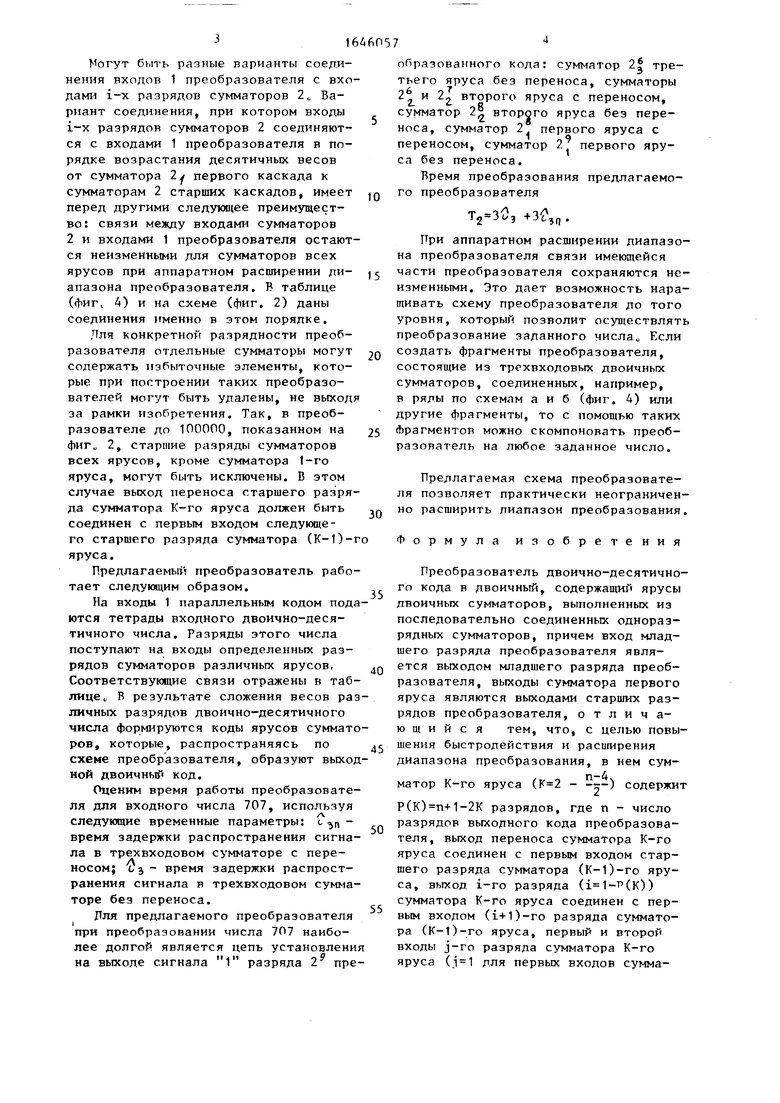

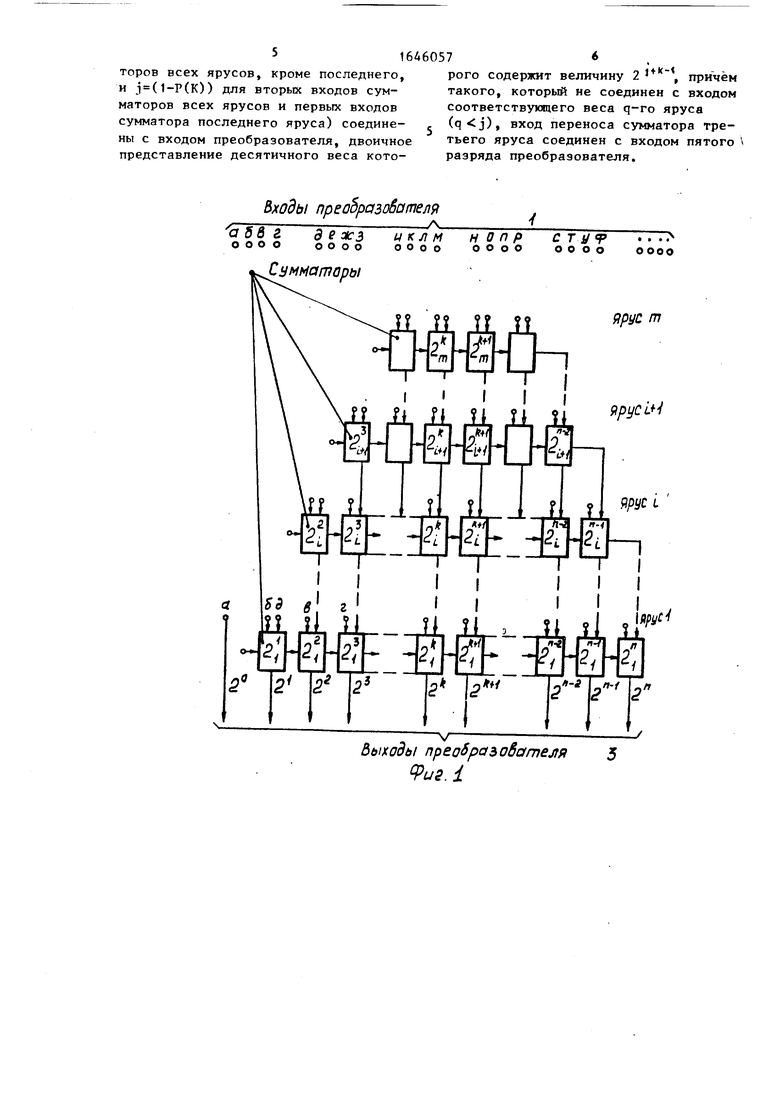

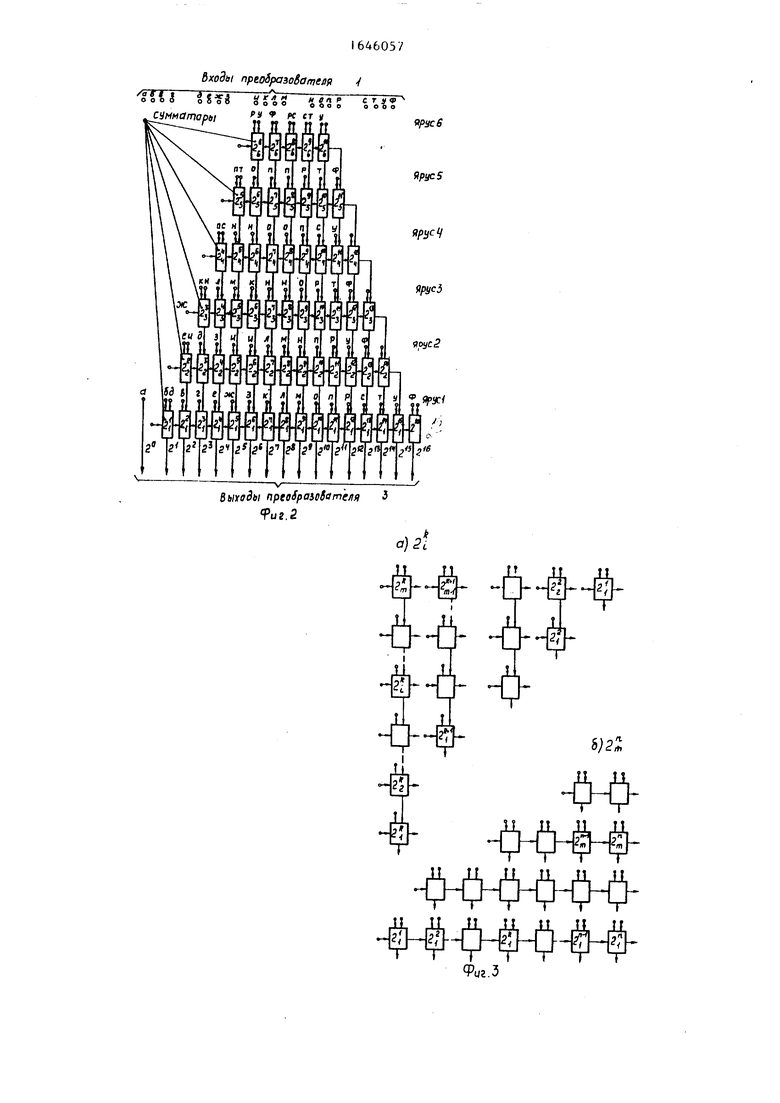

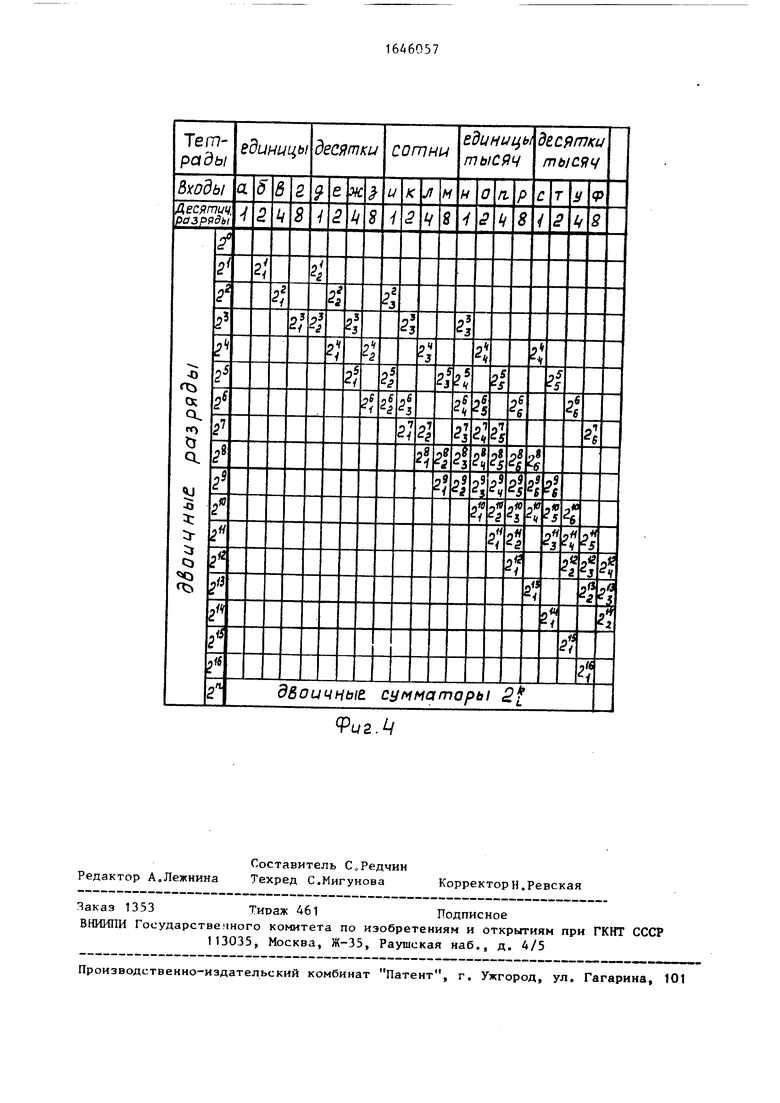

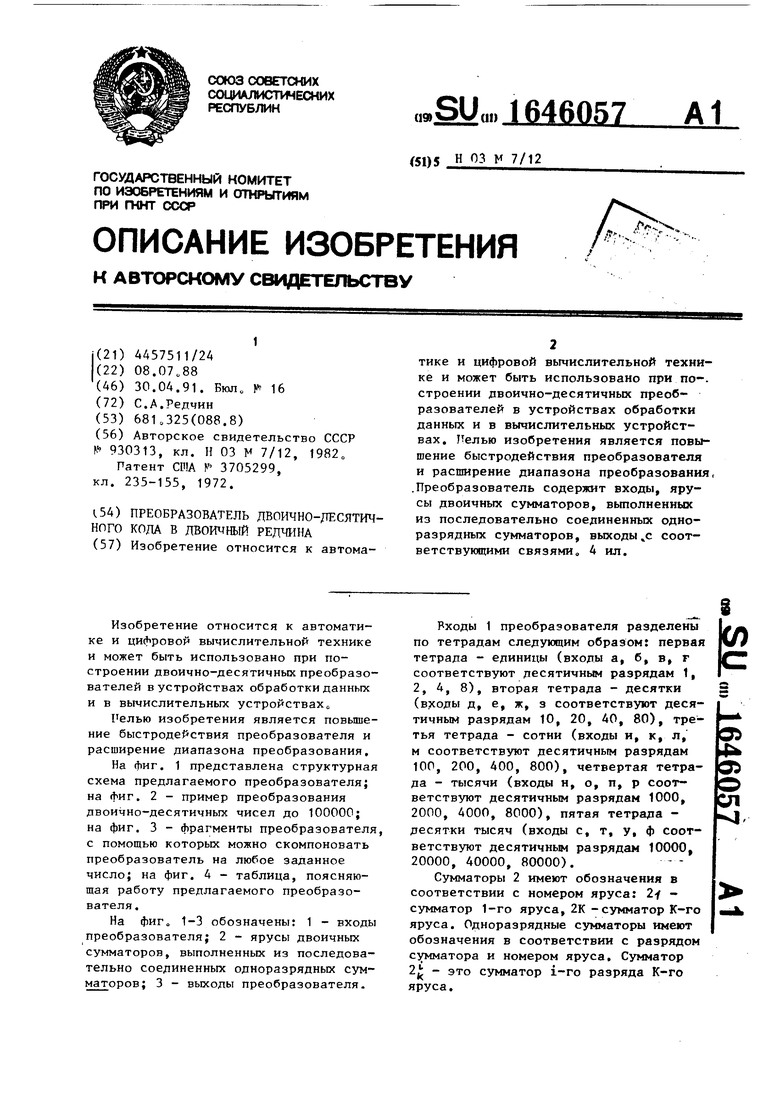

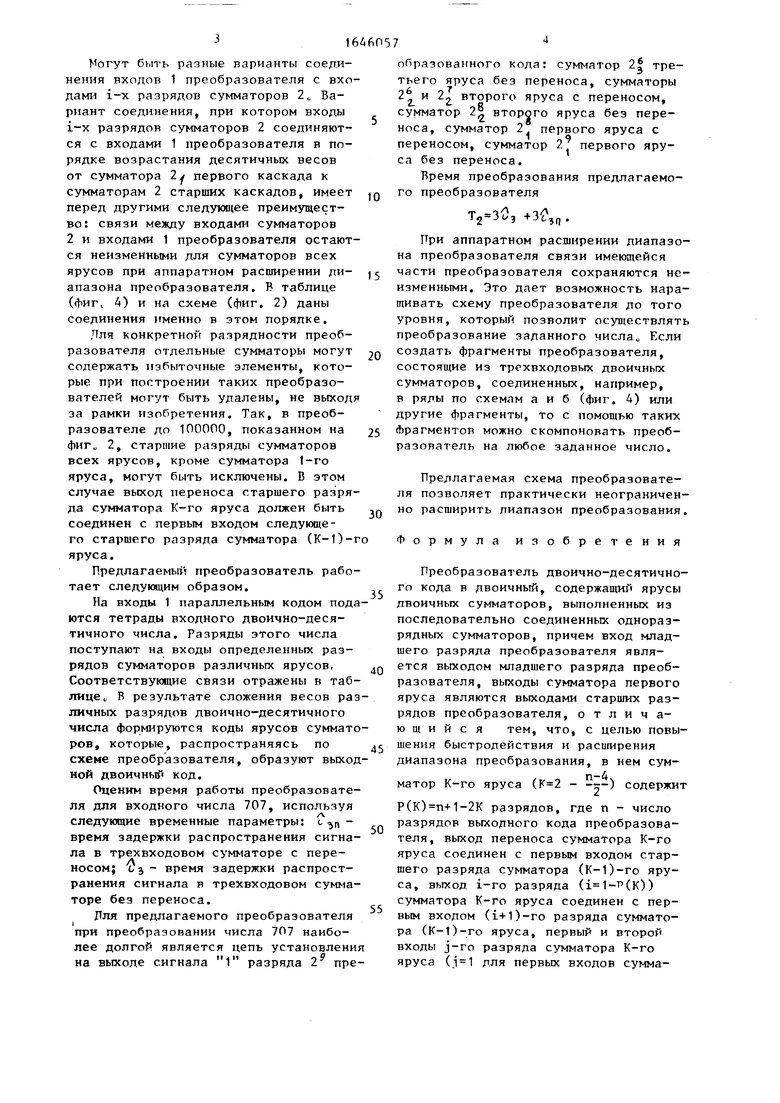

На фиг. 1 представлена структурная схема предлагаемого преобразователя; на фиг. 2 - пример преобразования двоично-десятичных чисел до 100000; на фиг. 3 - фрагменты преобразователя, с помощью которых можно скомпоновать преобразователь на любое заданное число; на фиг. 4 - таблица, поясняющая работу предлагаемого преобразователя.

На фиг„ 1-3 обозначены: 1 - входы преобразователя; 2 - ярусы двоичных сумматоров, выполненных из последовательно соединенных одноразрядных сумматоров; 3 - выходы преобразователя.

3

Рходы 1 преобразователя разделены по тетрадам следующим образом: первая тетрада - единицы (входы а, б, в, г соответствуют десятичным разрядам 1, 2, 4, 8), вторая тетрада - десятки (входы д, е, ж, з соответствуют десятичным разрядам 10, 20, 40, 80), третья тетрада - сотни (входы и, к, л, м соответствуют десятичным разрядам 100, 200, 400, 800), четвертая тетрада - тысячи (входы н, о, п, р соответствуют десятичным разрядам 1000, 2000, 4000, 8000), пятая тетрада - десятки тысяч (входы с, т, у, ф соответствуют десятичным разрядам 10000, 20000, 40000, 80000).

Сумматоры 2 имеют обозначения в соответствии с номером яруса: 2f - сумматор 1-го яруса, 2К -сумматор К-го яруса. Одноразрядные сумматоры имеют обозначения в соответствии с разрядом сумматора и номером яруса. Сумматор 2Ј - это сумматор 1-го разряда К-го яруса.

щ

65

Јь ОЭ О СЛ J

3164

Могут быть разные варианты соединения входов 1 преобразователя с входами 1-х разрядов сумматоров 20 Вариант соединения, при котором входы 1-х разрядов сумматоров 2 соединяются с входами 1 преобразователя в порядке возрастания десятичных весов от сумматора 2 у первого каскада к сумматорам 2 старших каскадов, имеет перед другими следующее преимущество: связи между входами сумматоров 2 и входами 1 преобразователя остаются неизменными для сумматоров всех ярусов при аппаратном расширении диапазона преобразователя. В таблице (фиг, 4) и на схеме (фиг. 2) даны соединения именно в этом порядке.

Для конкретной разрядности преобразователя отдельные сумматоры могут содержать избыточные элементы, которые при построении таких преобразователей могут быть удалены, не выходя за рамки изобретения. Так, в преобразователе до 100000, показанном на фиг„ 2, старшие разряды сумматоров всех ярусов, кроме сумматора 1-го яруса, могут быть исключены. В этом случае выход переноса старшего разряда сумматора К-го яруса должен быть соединен с первым входом следующего старшего разряда сумматора (К-1)-г яруса.

Предлагаемый преобразователь работает следующим образом.

На входы 1 параллельным кодом подаются тетрады входного двоично-десятичного числа. Разряды этого числа поступают на входы определенных разрядов сумматоров различных ярусов, Соответствующие связи отражены в таблице о В результате сложения весов различных разрядов двоично-десятичного числа формируются коды ярусов сумматоров, которые, распространяясь по схеме преобразователя, образуют выходной двоичный код.

Оценим время работы преобразователя для входного числа 707, следующие временные

время задержки распространения сигнас пере

используя параметры: о „

ла в трехвходовом сумматоре носом; ьз - время задержки распространения сигнала в трехвходовом сумматоре без переноса.

Для предлагаемого преобразователя при преобразовании числа 707 наиболее долгой является цепь установлени на выходе сигнала 1 разряда 2 пре

об L

яруса с переносом, второго яруса без переоПразованного кода: сумматор Z| третьего яруса без переноса, сумматоры 2 и 2 второго сумматор 2J|

носа, сумматор 2 первого яруса с переносом, сумматор 1 первого яруса без переноса.

Время преобразования предлагаемого преобразователя

, 43,„.

5

0

5

4Q 30

35

50

55

При аппаратном расширении диапазона преобразователя связи имеющейся части преобразователя сохраняются неизменными. Это дает возможность наращивать схему преобразователя до того уровня, который позволит осуществлять преобразование заданного числа Если создать фрагменты преобразователя, состоящие из трехвходовых двоичных сумматоров, соединенных, например, в ряды по схемам а и б (фиг. 4) или другие фрагменты, то с помощью таких Фрагментов можно скомпоновать преобразователь на любое заданное число.

Предлагаемая схема преобразователя позволяет практически неограниченно расширить диапазон преобразования.

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий ярусы двоичных сумматоров, выполненных из последовательно соединенных одноразрядных сумматоров, причем вход младшего разряда преобразователя является выходом младшего разряда преобразователя, выходы сумматора первого яруса являются выходами старших разрядов преобразователя, отличающийся тем, что, с целью повышения быстродействия и расширения диапазона преобразования, в нем сумп-4матор К-го яруса ( - -) содержит

Р(К)п+1-2К разрядов, где п - число разрядов выходного кода преобразователя, выход переноса сумматора К-го яруса соединен с первым входом старшего разряда сумматора (К-1)-го яруса, выход i-ro разряда ((K)) сумматора К-го яруса соединен с первым входом (i+1)-ro разряда сумматора (K-l)-ro яруса, первый и второй входы j-ro разряда сумматора К-го яруса ( для первых входов сумматоров всех ярусов, кроме последнего, и j(l-P(K)) для вторых входов сумматоров всех ярусов и первых входов сумматора последнего яруса) соединены с входом преобразователя, двоичное представление десятичного веса кото6057

рого содержит величину 2 Ч причём такого, который не соединен с входом соответствующего веса q-ro яруса (), вход переноса сумматора третьего яруса соединен с входом пятого разряда преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1043627A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1982 |

|

SU1097995A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501277A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU699520A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при по-, строении двоично-десятичных преобразователей в устройствах обработки данных и в вычислительных устройствах. УТелью изобретения является повышение быстродействия преобразователя и расширение диапазона преобразования, .Преобразователь содержит входы, ярусы двоичных сумматоров, выполненных из последовательно соединенных одноразрядных сумматоров, выходы „с соответствующими связями, 4 ил.

Входы прео&разобателя

а 66 г д е жзи к л м

оооо о о о о о о о о

Сумматоры

О П р ооо

С Т У Р

ОООО

О ООО

и

т

11

Г

Д.

Ярус т

SL

11 Л

9руС 14

ЯРУС L

2}-Я- -Ј

I I I I

Л 11

Т

Г-Г у у

,/

Выходы преобраьобателя Фиг.

-№№№ -№S-fr

-frfr -щ

-й- -о-й

г тг

тт

TT

I

ТГ

(°

«n(b

f virsujpgatDdfOidu iigoxng

foffdn

ЬэМк

Srtd

9 Й 5 Л/«/«Д/ Йи

.Sr.l S8 8 °,Sg.

/ mrsupgoeodfoadumgoxg

/.

9Ц2.Ц

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU930313A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1991-04-30—Публикация

1988-07-08—Подача