Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки цифровой информации.

Цель изобретения - расширение функциональных возможностей путем дополнительного вычисления Функций методом линейной интерполяции.

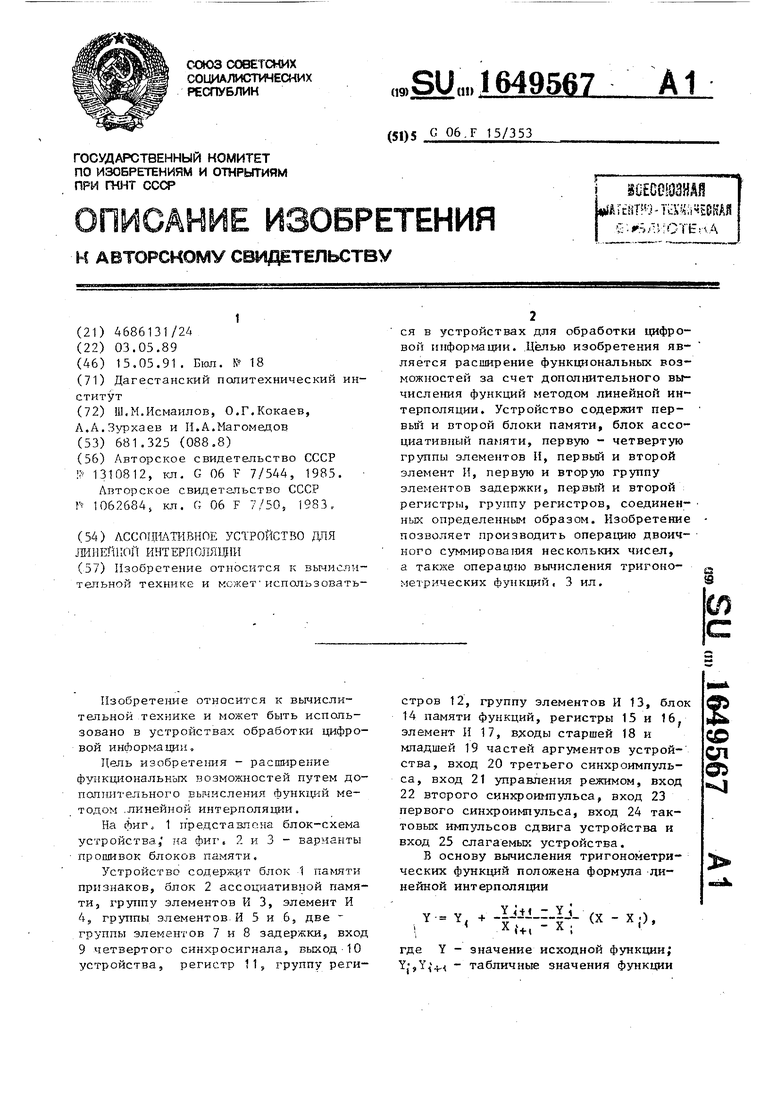

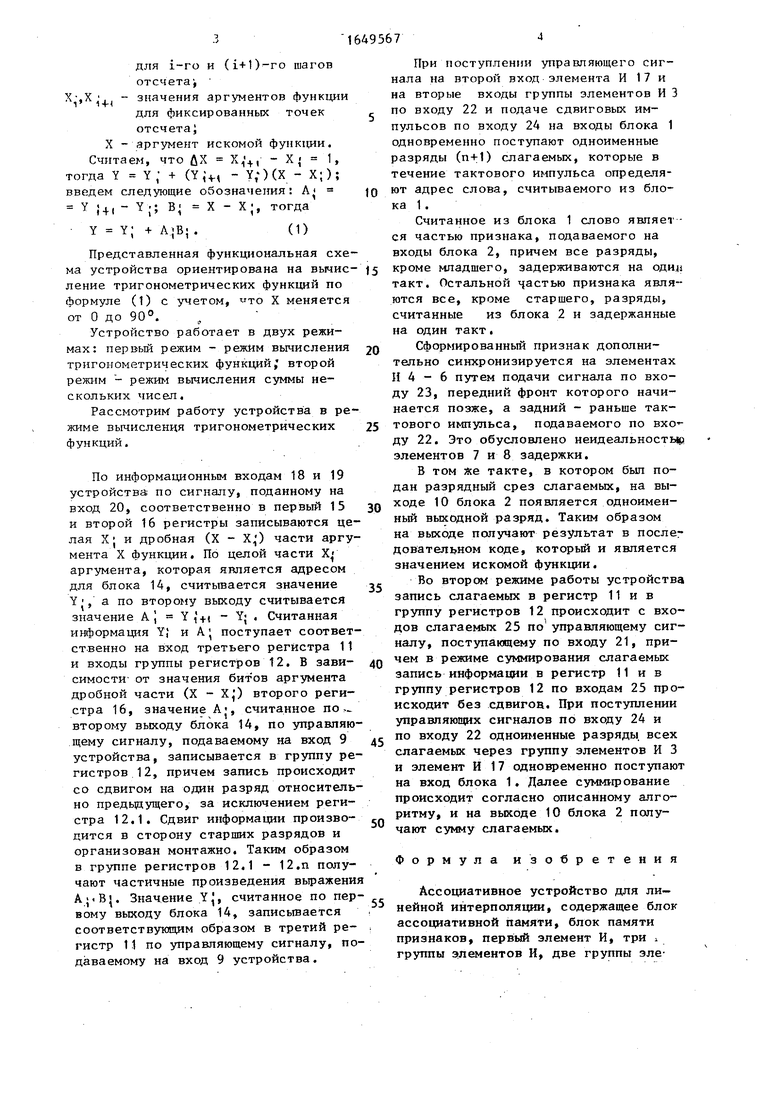

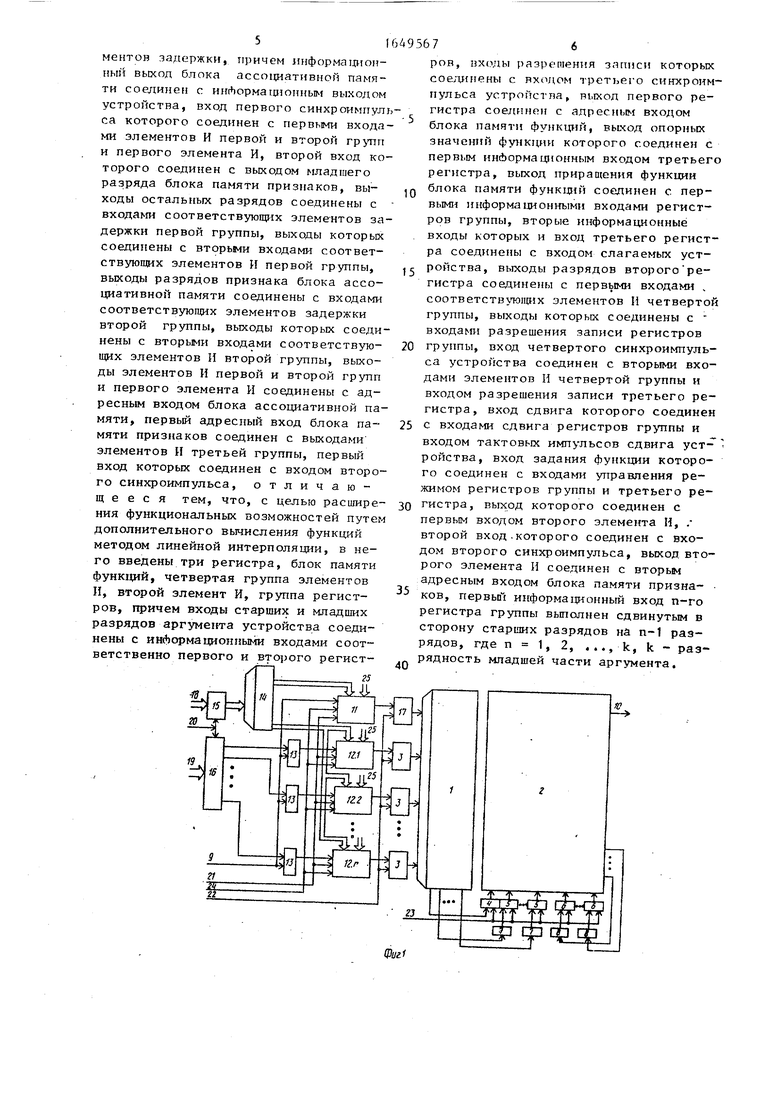

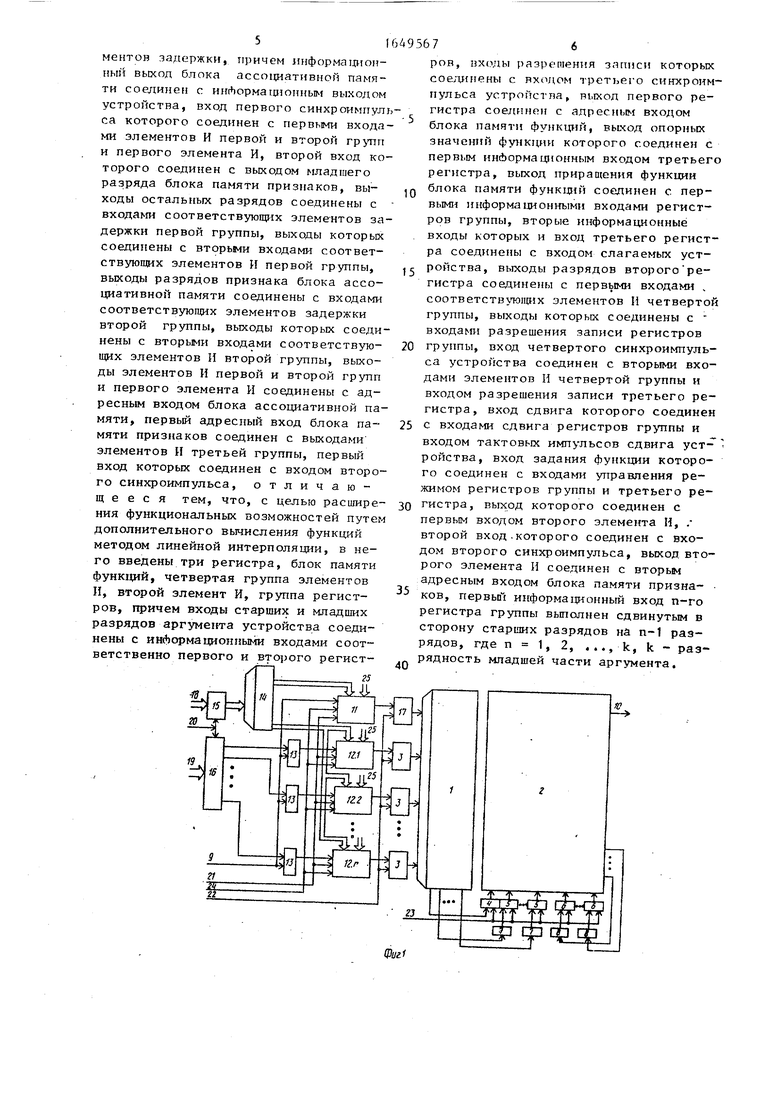

На Лиг, 1 представлена блок-схема устройства, ча фиг 2 и 3 - варианты прОШИБОК блоков памяти.

Устройство содержит блок 1 памяти признаков, блок 2 ассоциативной памя- тиэ группу элементов И 3, элемент И 45 группы элементов И 5 и 6, две - группы элеменч ов 7 и 8 задержки, вход 9 четвертого синхросигнала, выход 10 устройства, регистр 11, группу регистров 12, группу элементов И 13, блок 14 памяти функций, регистры 15 и 16; элемент И 17, входы старшей 18 и младшей 19 частей аргументов устройства, вход 20 третьего синхроимпульса, вход 21 управления режимом, вход 22 второго синхроимпульса, вход 23 первого синхроимпульса, вход 24 тактовых импульсов сдвига устройства и вход 25 слагаемых устройства.

В основу вычисления тригонометрических функций положена формула линейной интерполяции

2

СО

сд

о

sl

Y;-H - Y

(X - X;),

где

Х(Ч( -X;

Y - значение исходной функции;

Y , табличные значения функции

для 1-го и (i+1)-го шагов отсчета; Xi Xi +4 значения аргументов функции

для фиксированных точек

отсчетаJ

X - аргумент искомой функции. Считаем, что fiX Х, - Х{ 1, тогда Y Y; + (Y,., - Y;)(X - X;); введем следующие обозначения: А

Y i-н - Y;; в; x - x;. тогда

Y Y; + AjB;.(1)

Представленная функциональная схема устройства ориентирована на вычис- ление тригонометрических функций по формуле (1) с учетом, то X меняется от 0 до 90°.

Устройство работает в двух режимах: первый режим - режим вычисления тригонометрических функций; второй режим - режим вычисления суммы нескольких чисел.

Рассмотрим работу устройства в режиме вычисления тригонометрических функций.

По информационным входам 18 и 19 устройства по сигналу, поданному на вход 20, соответственно в первый 15 и второй 16 регистры записываются целая Х| и дробная (X - X,) части аргумента X Функции. По целой части Х аргумента, которая является адресом для блока 14, считывается значение Y , а по второму выходу считывается значение Aj Y , +i - Y; . Считанная информация Y; и А | поступает соответственно на вход третьего регистра 11 и входы группы регистров 12. В зави- симости от значения битов аргумента дробной части (X - Xj) второго регистра 16, значение А1, считанное по- второму выходу блока 14, по управляющему сигналу, подаваемому на вход 9 устройства, записывается в группу регистров 12, причем запись происходит со сдвигом на один разряд относительно предыдущего, за исключением регистра 12.1. Сдвиг информации произво- цится в сторону старших разрядов и организован монтажно. Таким образом в группе регистров 12,1 - 12.п получают частичные произведения выражения А «В«. Значение YJ, считанное по пер- вому выходу блока 14, записывается соответствующим образом в третий регистр 11 по управляющему сигналу, подаваемому на вход 9 устройства.

При поступлении управляющего сигнала на второй вход элемента И 17 и на вторые входы группы элементов И 3 по входу 22 и подаче сдвиговых импульсов по входу 24 на входы блока 1 одновременно поступают одноименные разряды (п+1) слагаемых, которые в течение тактового импульса определяют адрес слова, считываемого из блока 1 .

Считанное из блока 1 слово являет - ся частью признака, подаваемого на входы блока 2, причем все разряды, кроме младшего, задерживаются на оди такт. Остальной частью признака являются все, кроме старшего, разряды, считанные из блока 2 и задержанные на один такт,

Сформированный признак дополнительно синхронизируется на элементах И 4 - 6 путем подачи сигнала по входу 23, передний фронт которого начинается позже, а задний - раньше тактового импульса, подаваемого по ду 22. Это обусловлено неидеальностьц) элементов 7 и 8 задержки.

В том Же такте, в котором был подан разрядный срез слагаемых, на выходе 10 блока 2 появляется одноименный выходной разряд. Таким образом на выходе получают результат в последовательном коде, который и является значением искомой Функции.

Во втором режиме работы устройства запись слагаемых в регистр 11 и в группу регистров 12 происходит с входов слагаемых 25 по управляющему сигналу, поступающему по входу 21, причем в режиме суммирования слагаемых запись информации в регистр 11 и в группу регистров 12 по входам 25 происходит без сдвигов. При поступлении управляющих сигналов по входу 24 и по входу 22 одноименные разряды, всех слагаемых через группу элементов И 3 и элемент И 17 одновременно поступают на вход блока 1. Далее суммирование происходит согласно описанному алгоритму, и на выходе 10 блока 2 получают сумму слагаемых.

Формула изобретения

Ассоциативное устройство для линейной интерполяции, содержащее блок ассоциативной памяти, блок памяти признаков, первый элемент И, три i группы элементов И, две группы эле5

ментов задержки, причем информационный выход блока ассоциативной памяти соединен с информационным выходом устройства, вход первого синхроимпульса которого соединен с первыми входами элементов И первой и второй групп и первого элемента И, второй вход которого соединен с выходом младшего разряда блока памяти признаков, выходы остальных разрядов соединены с - входами соответствующих элементов задержки первой группы, выходы которых соединены с вторыми входами соответствующих элементов И первой группы, выходы разрядов признака блока ассоциативной памяти соединены с входами соответствующих элементов задержки второй группы, выходы которых соединены с вторыми входами соответствующих элементов И второй группы, выходы элементов И первой и второй групп и первого элемента И соединены с адресным входом блока ассоциативной памяти, первьй адресный вход блока памяти признаков соединен с выходами элементов И третьей группы, первый вход которых соединен с входом второго синхроимпульса, отличающееся тем, что, с целью расширения функциональных возможностей путем дополнительного вычисления функций методом линейной интерполяции, в него введены три регистра, блок памяти функций, четвертая группа элементов II, второй элемент И, группа регистров, причем входы старших и младших разрядов аргумента устройства соединены с информационными входами соответственно первого и второго регист

10

495676

ров, нходы разрешения записи которых соедицрны с входом третьего синхроимпульса устройства, я их од первого регистра соединен с адресным входом блока памяти функций, выход опорных значений функции которого соединен с первым информационным входом третьего регистра, выход приращения функции блока памяти функций соединен с первыми информационными входами регистров группы, вторые информационные входы которых и вход третьего регистра соединены с входом слагаемых устройства, выходы разрядов второго регистра соединены с первыми входами , соответствующих элементов И четвертой группы, выходы которых соединены с входами разрешения записи регистров группы, вход четвертого синхроимпульса устройства соединен с вторыми входами элементов И четвертой группы и входом разрешения записи третьего регистра, вход сдвига которого соединен с входами сдвига регистров группы и входом тактовых импульсов сдвига устройства, вход задания функции которого соединен с входами управления режимом регистров группы и третьего регистра, выход которого соединен с первым входом второго элемента И, / второй вход-которого соединен с входом второго синхроимпульса, выход второго элемента И соединен с вторым адресным входом блока памяти призна-

15

20

25

30

35 ков, первый информационный вход п-го регистра группы выполнен сдвинутым в сторону старших разрядов на п-1 разрядов, где п 1, 2, ..., k, k - разрядность младшей части аргумента.

40

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления элементарных функций в модулярной системе счисления | 1985 |

|

SU1291977A1 |

| Устройство для вычисления функции аRстG х/у | 1988 |

|

SU1647555A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1465884A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для вычисления тригонометрических функций с плавающей запятой | 1986 |

|

SU1425661A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

Изобретение относится к вычиелч- тельной технике и мьжет неполнаоваться в устройствах для обработки цифровой информации. Целью изобретения является расширение функциональных возможностей за счет дополнительного вычисления функций методом линейной интерполяции. Устройство содержит первый и второй блоки памяти, блок ассоциативный памяти, первую - четвертую группы элементов И, первый и второй элемент И, первую и вторую группу элементов задержки, первый и второй регистры, группу регистров, соединенных определенным образом. Изобретение позволяет производить операцию двоичного суммирования нескольких чисел, а также операцию вычисления тригонометрических функций, 3 ил.

#.

№

гз

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для предварительной обработки информации | 1982 |

|

SU1062684A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-03—Подача