5

СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам (ЗУ) с контролем правильности хранения информации, и может быть использовано для построения буферных ЗУ в системах связи. Цель изобретения - повышение достоверности контроля. Запоминающее устройство с контролем информации содержит блок 1 памяти, информационные входы 2 и выходы 3, блок 4 управления, вход 5 синхронизации записи, первый сигнатурный анализатор 6, первый блок сравнения 7, выход 8 результата контроля второй 9 блок сравнения, второй 10 сигнатурный анализатор, третий блок 11 сравнения, первый 12 и второй 13 счетчики, выход 15 сопровождения контроля, выход 16 разрешения считывания, выход 17 сопровождения считывания, входы синхронизации контроля 18 и считывания 19. 3 ил.

If 13

о

XI

N N5 О

Фиг f

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам (ЗУ) с контролем правильности хранения информации, и может быть использовано для построения буферного ЗУ в системах связи.

Цель изобретения - повышение достоверности контроля.

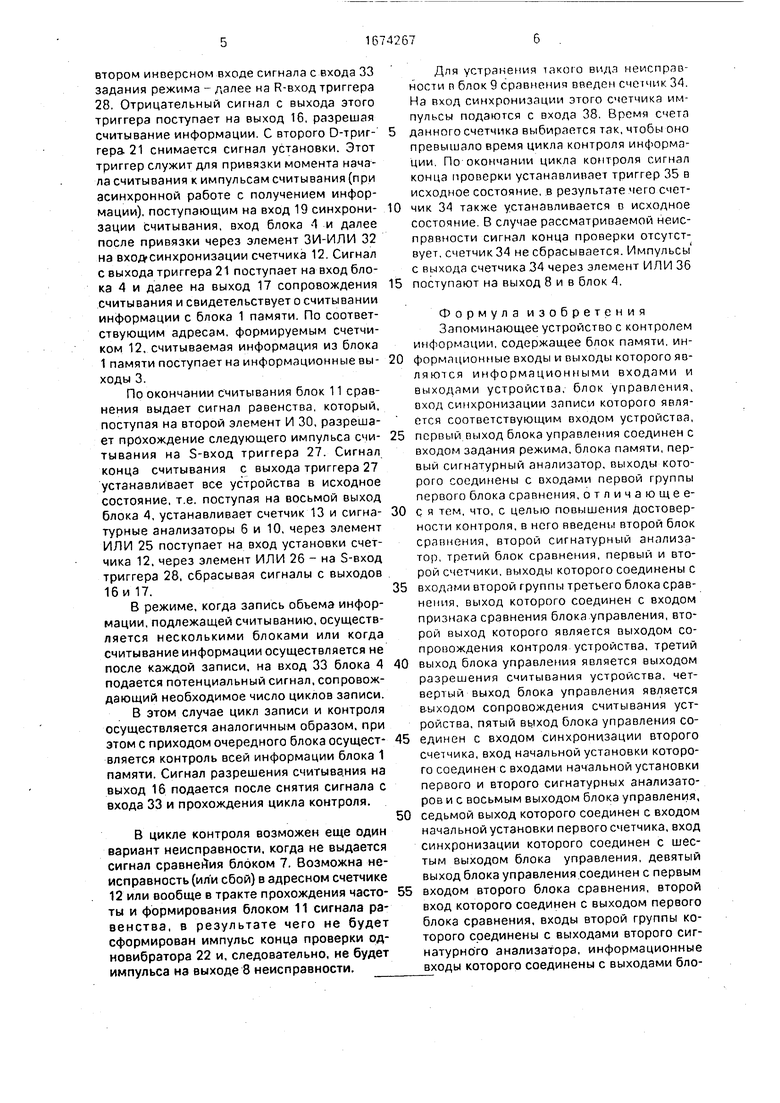

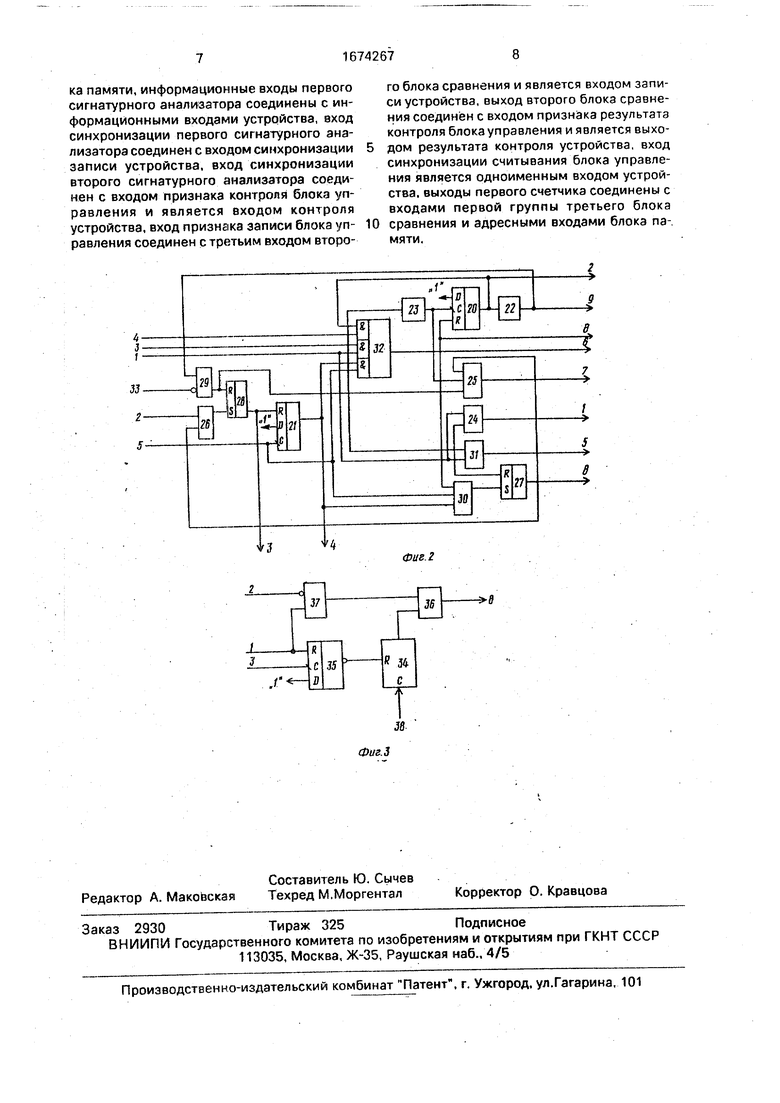

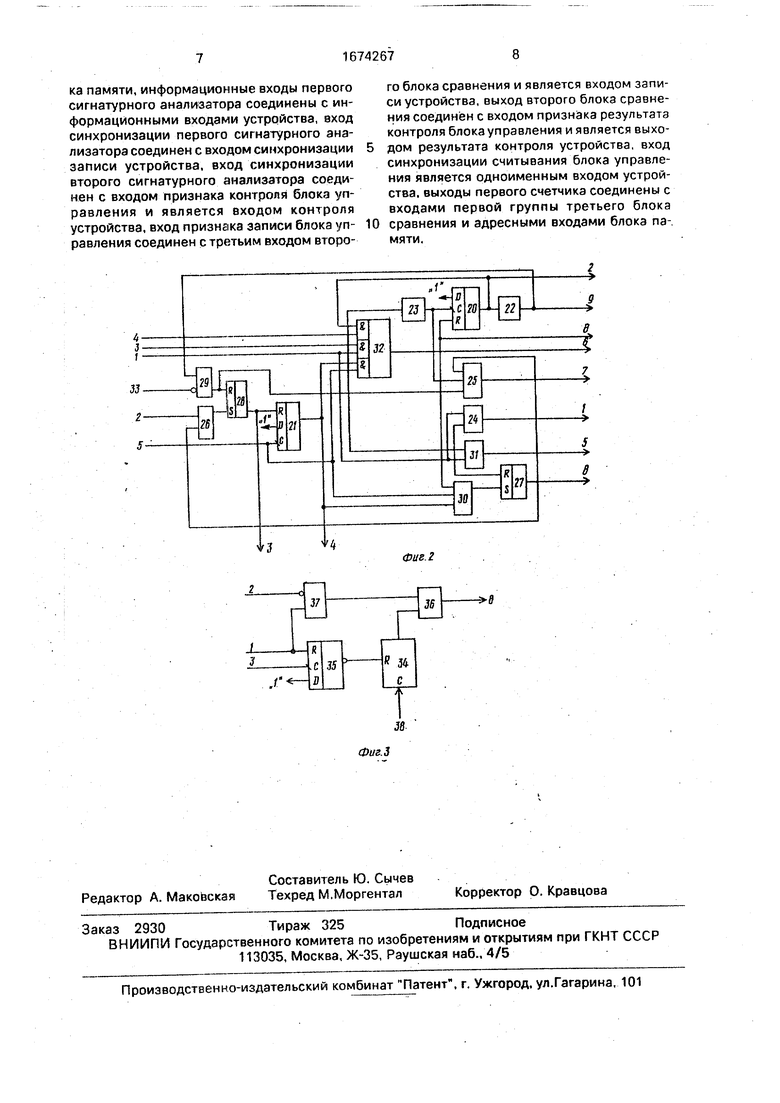

На фиг. 1 приведена схема запоминающего устройства с контролем информации; на фиг. 2 - схема блока управления; на фиг.

3- схема второго блока контроля.

На фиг. 1-3 обозначены блок 1 памяти, информационные входы 2 и выходы 3, блок

4управления, вход 5 синхронизации запи- си, первый сигнатурный анализатор 6, первый блок 7 сравнения, выход 8 результата контроля, второй блок 9 сравнения, второй сигнатурный анализатор 10, третий блок 11 сравнения, первый 12 и второй 13 счетчики, вход 14 записи, выход 15 сопровождения контроля, выход 16 разрешения считывания, выход 17 сопровождения считывания, входы признака контроля 18 и считывания

19, первый 20 и второй 21 триггеры, первый 22 и второй 23 одновибраторы, формирователь 24, первый 25 и второй 26 элементы ИЛИ. третий 27 и четвертый 28 триггеры, первый 29, второй 30 и третий 31 элементы И, элемент ЗИ-ИЛИ 32, вход 33 задания режима, счетчик 34, триггер 35, элемент ИЛИ 36, элемент И 37, выход 38 синхронизации.

Устройство работает следующим образом.

Перед началом работы на S-вход триггера 27 и R-вход триггера 35 подается сигнал начальной установки (цепи начальной установки не показаны). В результате остальные триггеры и счетчик устанавливаются в ис- ходное состояние. При необходимости записать блок информации с входа 14 записи подается сигнал (потенциальный) на вход блока 4 управления, с входа 5 синхронизации записи на вход блока управления и на вход синхронизации первого сигнатурного анализатора 6. В блоке 4 импульсы записи при сопровождении сигнала записи с входа 14 через элемент ЗИ-ИЛИ 32 и элемент И 31 поступают соответственно на шестой и пя- тый выходы блока 4 и далее на входы синхронизации первого 12 и второго 13 счетчиков. Информация, поступающая на информационные входы 2 устройства, записывается в блок 1 памяти по адресам, фор- мируемым счетчиком 12,

Счетчики 12 и 13 как во время записи, так и по окончании ее, имеют одинаковое значение, т.е. блок 11 сравнения выдает сигнал равенства на вход блока 4. Кроме блока

1 памяти информация поступает в первый сигнатурный анализатор 6 По срезу сигм э л а записи на входе 14 в блоке 9 сравнения взводится триггер 35. а в блоке 4 второй одновибратор 23 вырабатывает импульс установки, который через первый элемент ИЛИ 25 поступает на седьмой выход блока 4 и устанавливает в исходное состояние счетчик 12. С выхода блока 11 сравнения снимается сигнал равенства. По срезу импульса, поступающего с выхода одновибра- тора 23, первый триггер 20 переключается в единичное состояние, т.е. начинается цикл контроля. Потенциальный сигнал с выхода триггера 20 поступает на второй выход блока 4 и далее на выход 15 сопровождения контроля, а также на элемент ЗИ-ИЛИ 32, разрешая прохождение импульсов контроля с входа 18 контроля через вход признака контроля блока 4, элемент ЗИ-ИЛИ 32 на вход синхронизации счетчика 12. По соответствующим адресам, формируемым счетчиком 12, из блока 1 памяти считываемая информация поступает на второй сигнатурный анализатор 10.

Значения выходов счетчиков 12 и 13 сравниваются блоком 11 сравнения, который при достижении равенства этих значений выдает сигнал равенства, т.е. окончания считывания. По этому сигналу триггер 20 устанавливается в нулевое состояние и снимает сигнал с выхода 15. По срезу этого сигнала первый одновибратор 22 вырабатывает импульс конца проверки на девятый выход блока 4 и далее на первый вход блока 9 сравнения. В блоке 9 импульс конца проверки поступает на элемент И 37, а также устанавливает в исходное состояние триггер 35. Далее, если на втором инверсном входе элемента И 37 присутствует нулевой сигнал с второго входа блока 9, импульс конца проверки через элемент ИЛИ 36 поступает на вход 8 и на вход признака результата контроля блока 4. Нулевой сигнал на инверсный вход элемента И 37 поступает с выхода 7 блока сравнения и формируется в случае неравенства сигналов с выхода сигнатурных анализаторов 6 и 10, что свидетельствует о несоответствии записанной в блок 1 памяти и считанной информации. В блоке 4 импульс неисправности через второй элемент ИЛИ 26 поступает на S-вход второго триггера 28, запрещая формирования сигналов на выходах 16 разрешения считывания и 17 сопровождения считывания.

В случае положительного исхода цикла контроля импульс конца проверки с выхода одновибратора 22 поступает на вход первого элемента И 29 и - при отсутствии но

втором инверсном входе сигнала с входа 33 задания режима - далее на R-вход триггера 28. Отрицательный сигнал с выхода этого триггера поступает на выход 16, разрешая считывание информации. С второго D-триг- гера 21 снимается сигнал установки. Этот триггер служит для привязки момента начала считывания к импульсам считывания (при асинхронной работе с получением информации), поступающим на вход 19 синхронизации считывания, вход блока -1 и далее после привязки через элемент ЗИ-ИЛИ 32 на входгсинхронизации счетчика 12. Сигнал с выхода триггера 21 поступает на вход блока 4 и далее на выход 17 сопровождения считывания и свидетельствует о считывании информации с блока 1 памяти. По соответствующим адресам, формируемым счетчиком 12, считываемая информация из блока 1 памяти поступает на информационные выходы 3.

По окончании считывания блок 11 сравнения выдает сигнал равенства, который, поступая на второй элемент И 30, разрешает прохождение следующего импульса считывания на S-вход триггера 27. Сигнал конца считывания с выхода триггера 27 устанавливает все устройства в исходное состояние, т.е. поступая на восьмой выход блока 4, устанавливает счетчик 13 и сигнатурные анализаторы 6 и 10, через элемент ИЛИ 25 поступает на вход установки счетчика 12, через элемент ИЛИ 26 - на S-пход триггера 28, сбрасывая сигналы с выходов 16и 17.

В режиме, когда запись объема информации, подлежащей считыванию, осуществляется несколькими блоками или когда считывание информации осуществляется не после каждой записи, на вход 33 блока 4 подается потенциальный сигнал, сопровождающий необходимое число циклов записи.

В этом случае цикл записи и контроля осуществляется аналогичным образом, при этом с приходом очередного блока осуществляется контроль всей информации блока 1 памяти. Сигнал разрешения считывания на выход 16 подается после снятия сигнала с входа 33 и прохождения цикла контроля.

В цикле контроля возможен еще один вариант неисправности, когда не выдается сигнал сравнения блоком 7. Возможна неисправность (или сбой) в адресном счетчике 12 или вообще в тракте прохождения частоты и формирования блоком 11 сигнала равенства, в результате чего не будет сформирован импульс конца проверки од- новибратора 22 и, следовательно, не будет импульса на выходе 8 неисправности.

Для устранения т .жен о вид неисправности п блок 9 сравнения ВРРДОН счетчик 34. На вход синхронизации этого счетчика импульсы подаются с входа 38. Время счгтп

данного счетчика выбирается так, чтобы оно превышало время цикла контроля информации. По окончании цикла контроля сигнал конца проверки устанавливает триггер 35 в исходное состояние, в результате чего счетчик 34 также устанавливается о исходное состояние В случае рассматриваемой неисправности сигнал конца проверки отсутствует, счетчик 34 не сбрасывается. Импульсы с выхода счетчика 34 через элемент ИЛИ 36

поступают на выход 8 и в блок 4,

Формула изобретения Запоминающее устройство с контролем информации, содержащее блок памяти, информационные входы и выходы которого яв- ляются информационными входами и выходами устройства, блок управления, вход синхронизации записи которого является соответствующим входом устройства,

первый пыход блока управления соединен с входом задания режима, блока памяти, первый сигнатурный анализатор, выходы которого соединены с входами первой группы первого блока сравнения, отличаю щеес я тем. что, с целью повышения достоверности контроля, в него введены второй блок сравнения, второй сигнатурный анализатор, третий блок сравнения, первый и второй счетчики, выходы которого соединены с

входами второй г руппы третьего блока сравнения, выход которого соединен с входом признака сравнения блока управления, второй выход которого является выходом сопровождения контроля устройства, третий

выход блока управления является выходом разрешения считывания устройства, четвертый выход блока управления является выходом сопровождения считывания устройства, пятый выход блока управления соединен с входом синхронизации второго счетчика, вход начальной установки которого соединен с входами начальной установки первого и второго сигнатурных анализаторов и с восьмым выходом блока управления,

седьмой выход которого соединен с входом начальной установки первого счетчика, вход синхронизации которого соединен с шестым выходом блока управления, девятый выход блока управления соединен с первым

входом второго блока сравнения, второй вход которого соединен с выходом первого блока сравнения, входы второй группы которого соединены с выходами второго сигнатурного анализатора, информационные входы которого соединены с выходами блока памяти, информационные входы первого сигнатурного анализатора соединены с информационными входами устройства, вход синхронизации первого сигнатурного анализатора соединен с входом синхронизации записи устройства, вход синхронизации второго сигнатурного анализатора соединен с входом признака контроля блока управления и является входом контроля устройства, вход признака записи блока управления соединен с третьим входом второ

го блока сравнения и является входом записи устройства, выход второго блока сравнения соединен с входом признака результата контроля блокауправления и является выходом результата контроля устройства, вход синхронизации считывания блока управления является одноименным входом устройства, выходы первого счетчика соединены с входами первой группы третьего блока сравнения и адресными входами блока памяти.

Т

Jfl

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-08-30—Публикация

1988-05-05—Подача